解決痛點

隨著集成電路工藝越漸復雜,芯片設計規模越來越大,在生產過程中產生缺陷和出現良率問題的概率也就越來越高。為了達到DPPM(百萬分比的缺陷率)的嚴格要求,需要通過多道測試來剔除有缺陷的芯片,并且診斷出良率根因。

DFT(Design for Test)技術作為業界的標準手段,通過在芯片設計時加入測試專用電路,增加芯片的可測試性。如何降低測試成本,同時測試電路占用芯片設計上較小的面積,達到更高的故障覆蓋率,已成為當前產業界的一個關鍵難題。此外,在測試到芯片上的故障后,精準定位到故障位置是另一嚴峻挑戰。

為解決以上痛點,杭州廣立微電子股份有限公司與其子公司上海億瑞芯電子科技有限公司強強聯合,于2023年11月25日在杭州發布業界領先的可測性設計自動化和良率診斷解決方案(DFTEXP流程和解決方案)。

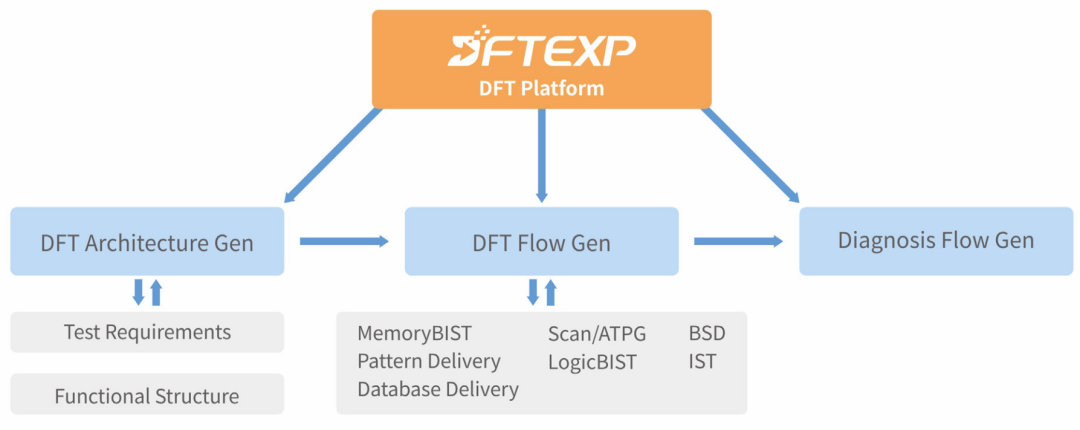

DFTEXP是一個完整的EDA平臺,此平臺集成了全新的DFT工具、DFT設計和良率診斷分析流程,用戶可以輕松應對復雜的SoC芯片、大規模芯片的診斷測試、汽車電子的功能性安全測試以及良率提升的挑戰,并取得質量與成本雙贏,為行業打造完善良率提升生態。

DFTEXP平臺優勢

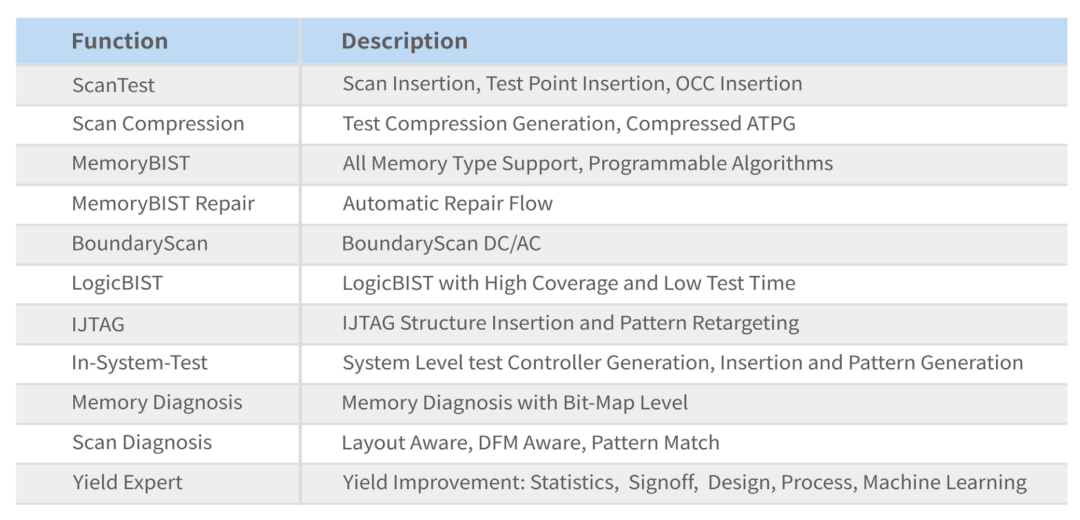

DFTEXP涵蓋DFT全流程工具,支持MCU、AI、GPU、Network、5G基帶、AP等不同應用領域芯片和規模的DFT設計實現需求,并且支持系統級測試的In-System-Test, 以支持汽車電子的功能安全測試方案。

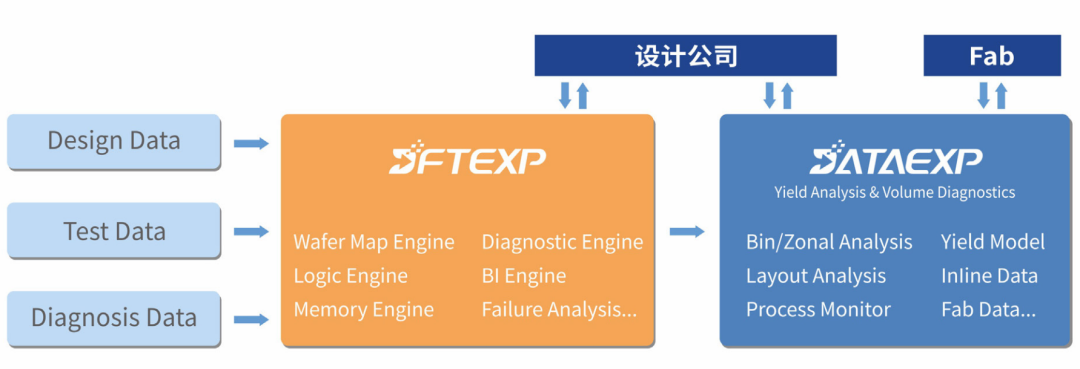

全方位的良率提升方案,可以適應不同工藝、不同Fab的要求。通過DFT Diagnosis和Fab大數據分析系統,可快速發現影響良率的根因,建立提升方案。

從DFT的測試診斷結果,可結合DATAEXP-YMS中多維度的芯片相關數據,如產品版圖、WAT/CP/FT測試數據、產線上的工藝步驟、設備、和缺陷等監控數據,從而更精準地識別故障行為和分析故障根因,加速芯片產品上市場的周期。

DFT自動化實現流程,以及完備的版本驗收流程。同時支持RTL和Netlist Flow,并且通過Hierarchical DFT和Hierarchical ATPG流程,加速產品Time-To-Market; 建立完備的版本驗收流程,滿足各種工藝設計的DPPM要求。

新發布的DFTEXP 解決方案與廣立微現有的DATAEXP-YMS良率提升系統協同互補,為芯片設計企業打通從版圖設計到最終測試各環節的“一站式”數據鏈,助力芯片設計公司在開發產品時降本增效,更快速地發現故障和良率根因。同時也為晶圓制造廠,提供完整的DFT和良率診斷工具,提升工藝水平,更好地服務芯片設計公司。

廣立微將持續緊密關注行業發展動態和技術前沿,全力投入研發創新。我們致力于為客戶提供精準應對挑戰、抓住機遇的智能化支持,以助推中國芯片行業蓬勃發展邁上新的臺階。

審核編輯:彭菁

-

集成電路

+關注

關注

5387文章

11534瀏覽量

361647 -

芯片設計

+關注

關注

15文章

1015瀏覽量

54879 -

自動化

+關注

關注

29文章

5563瀏覽量

79240 -

廣立微電子

+關注

關注

0文章

40瀏覽量

1931

原文標題:重磅發布?廣立微全新推出領先的可測性設計(DFT)自動化和良率診斷協同解決方案DFTEXP

文章出處:【微信號:gh_7b79775d4829,微信公眾號:廣立微Semitronix】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PLC在工業自動化的應用及解決方案

廣立微INF-AI助力格科微產品良率提升

廣立微發布業界領先的可測性設計自動化和良率診斷解決方案

廣立微發布業界領先的可測性設計自動化和良率診斷解決方案

評論