技術前沿:扇出型板級封裝FOPLP

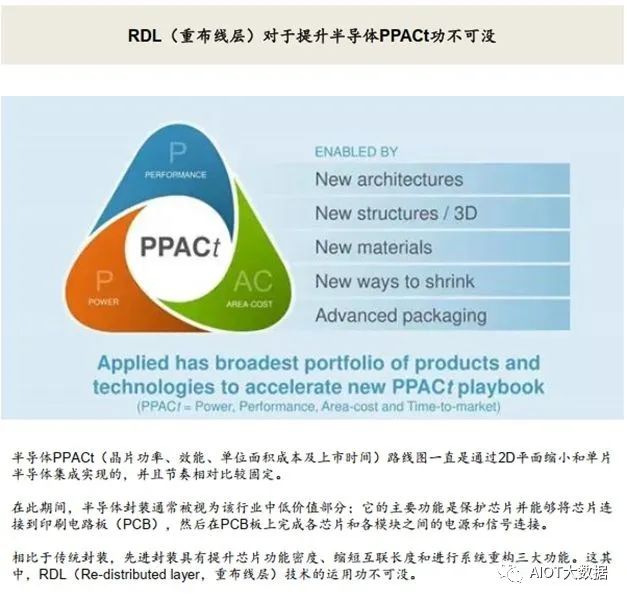

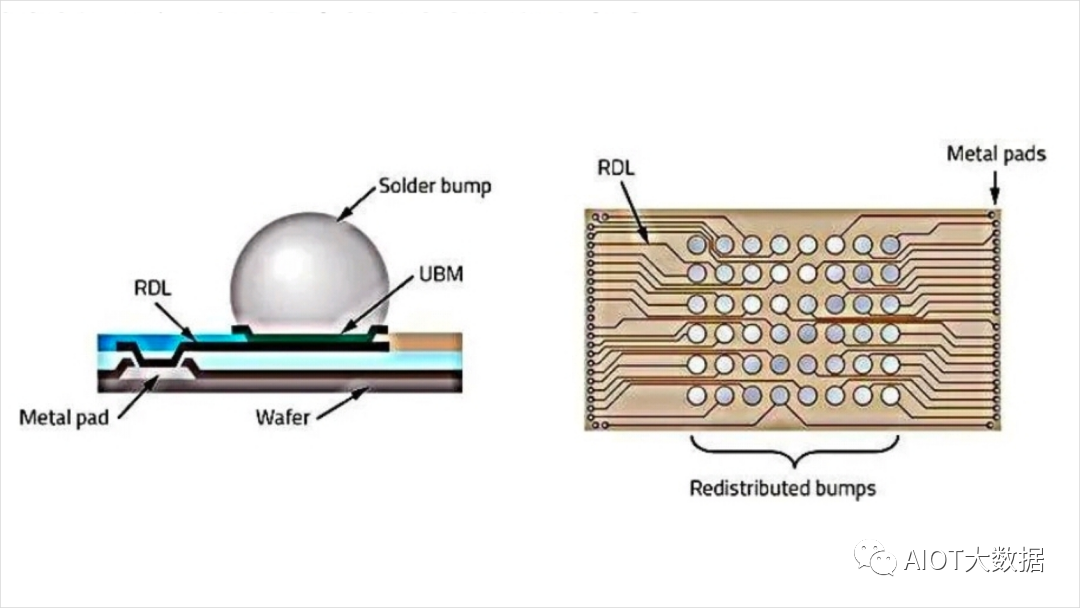

扇出型封裝一般是指,晶圓級/面板級封裝情境下,封裝面積與die不一樣,且不需要基板的封裝,也就是我們常說的FOWLP/FOPLP。扇出型封裝的核心要素就是芯片上的RDL重布線層(可參考下面圖表說明),通過RDL替代了傳統封裝下基板傳輸信號的作用,使得扇出型封裝可以不需要基板而且芯片成品的高度會更低,所以扇出型封裝的發明初衷其實是降低成本,而且由于扇出型封裝在封裝面積上沒有扇入那么多限制,整個封裝設計也會變得更加靈活和“自由”。因此扇出封裝最先在一些小面積、低性能的領域被推廣開來。

隨著扇出型封裝技術自身的發展,越來越多人認識到這個技術不應該只用于低成本低性能領域,它有巨大的潛力,在行業公司不斷努力的推動下,扇出型封裝今天已經成為了先進封裝技術的代表之一,已經可以被廣泛用于高性能領域。

經過多年的發展和沉淀,半導體芯片IC封裝技術已經越來越成熟,如今已有數百種封裝類型。而在這數百種封裝類型中,扇出型封裝日益火熱起來,其更被認為是延續和超越摩爾定律的關鍵技術方案。

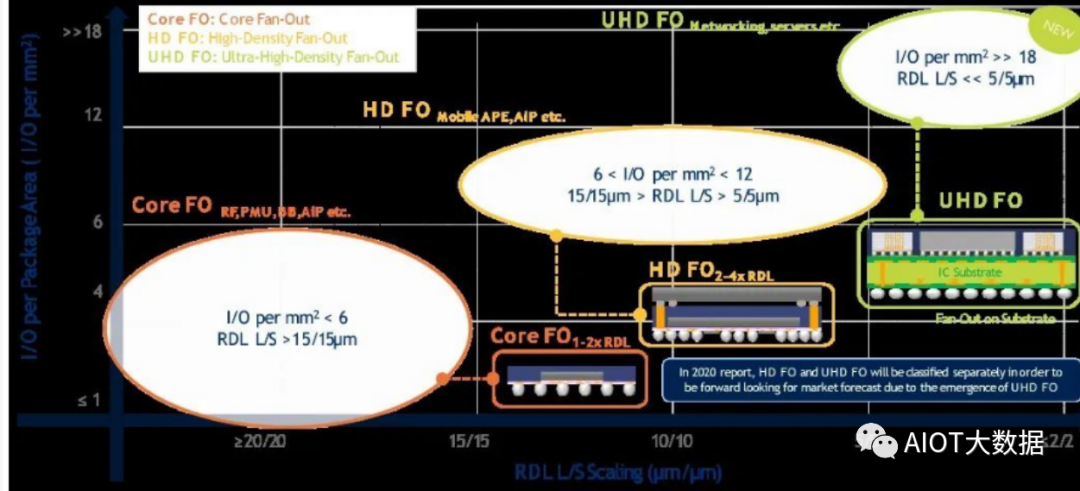

CoreFO,HDFO,UHDFO在I/O以及RDLL/S對比

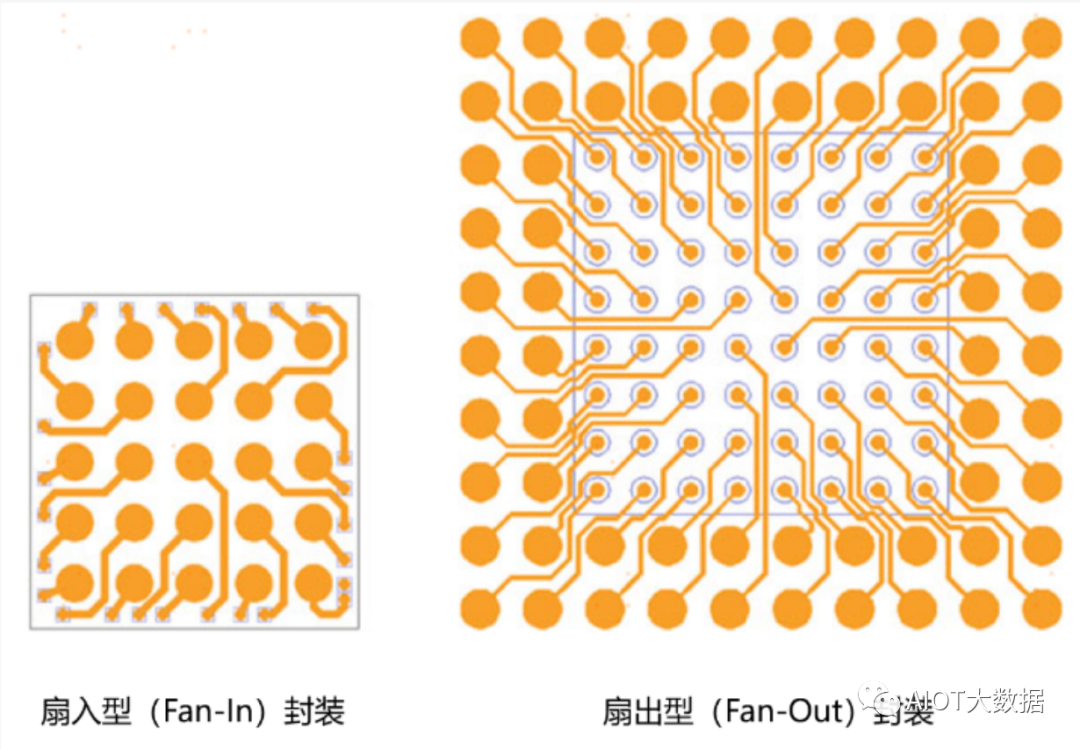

扇入型封裝和扇出型封裝區別

談到扇出型(Fan-Out)封裝,必然會聯系到扇入型(Fan-In)封裝。扇入型(Fan-In)封裝工藝流程大致描述為,整片晶圓芯片進行封裝測試,之后再切割成單顆芯片,封裝尺寸與芯片尺寸大小相同。

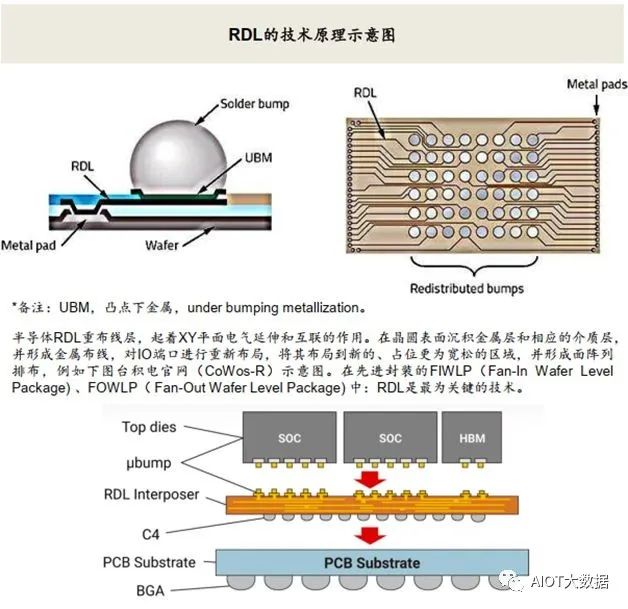

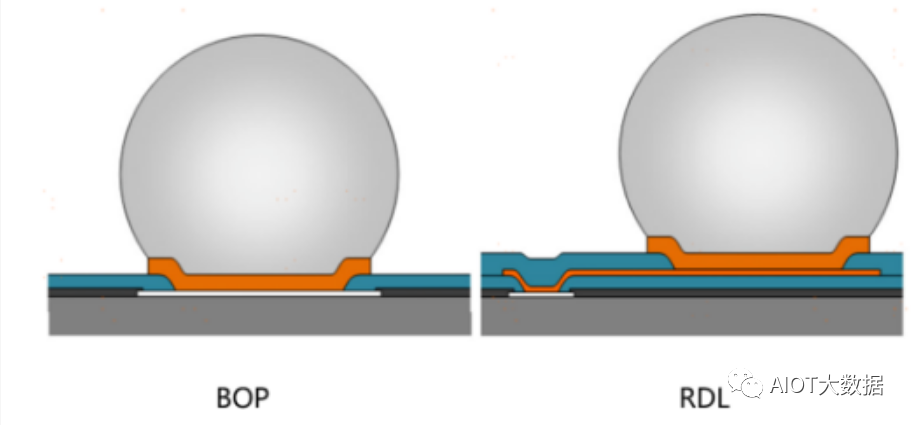

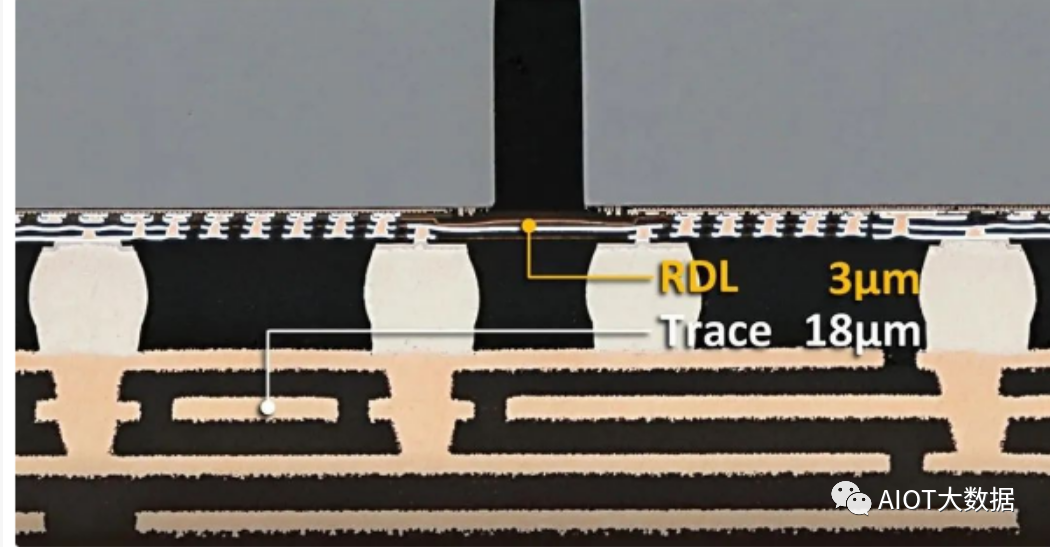

常見的Fan-In(WLCSP)通常可以分為BOP(BumpOnPad)和RDL(RedistribuTIonLayer)。BOP封裝結構簡單,Bump直接生長在Alpad上;如果Bump位置遠離Alpad,則需要通過RDL將Alpad與Bump相連。

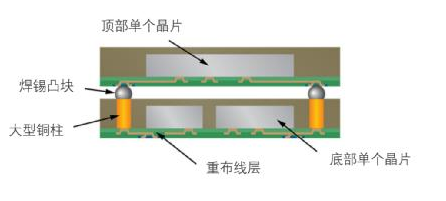

隨著I/O數量的增加,芯片尺寸無法容納所有I/O時,扇出型封裝由此衍生而來。扇出型封裝基于重組技術,芯片被切割完畢后,將芯片重新嵌埋到重組載板(8寸,12寸wafercarrier或者600mmX580mm等大尺寸面板),按照與扇入型封裝工藝類似的步驟進行封裝測試,然后將重組載板切割為單顆芯片,芯片外的區域為Fan-Out區域,允許將球放在芯片區域外。

扇入型封裝和扇出型封裝區別兩者最大的差異為RDL布線,在扇入型封裝中,RDL向內布線,而在扇出型封裝中,RDL既可向內又可向外布線,所以扇出型封裝可以實現更多的I/O。

扇出型封裝細解

扇出型封裝目前存在兩大技術分支,即扇出型晶圓級封裝(FOWLP)以及扇出型面板級封裝(FOPLP)。

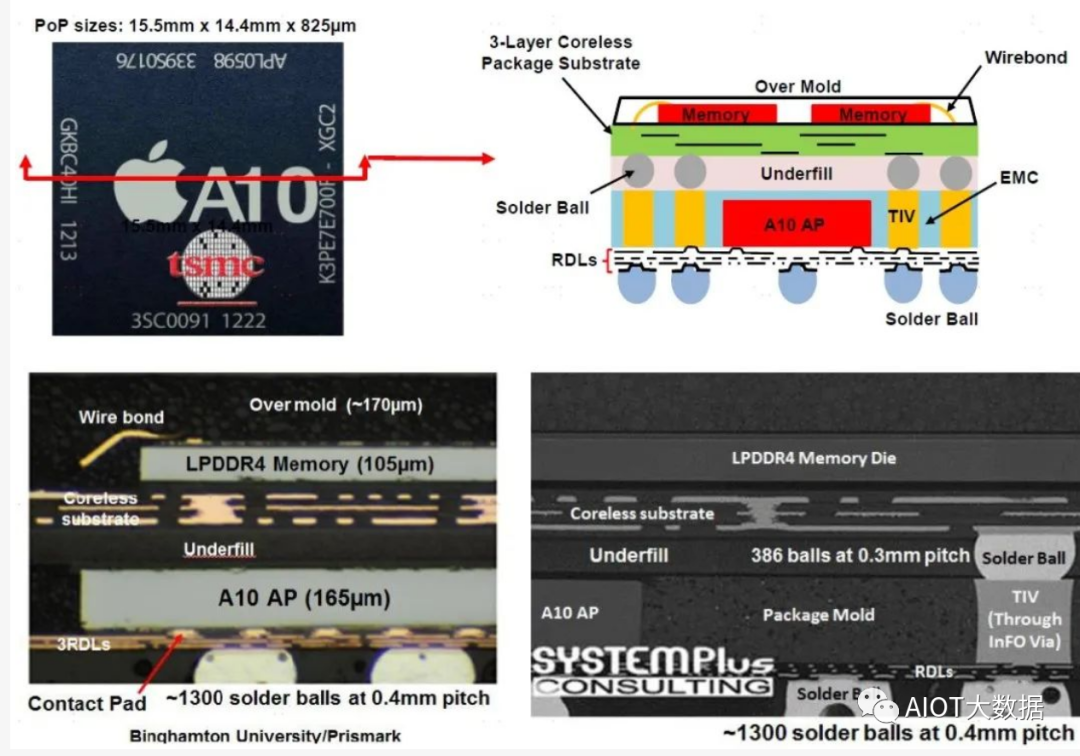

FOWLP封裝2009年量產,但彼時只應用于手機基帶芯片。真正轉折點是2016年,iPhone7系列A10處理器采用TSMC基于FOWLP開發的集成扇出型芯片堆疊(IntegratedFan-OutPackageonPackage,InFO-PoP)封裝,此后扇出型(Fan-Out)封裝成為熱點,各大手機OEM廠商爭相追求HDFO(High-DensityFan-Out)封裝。

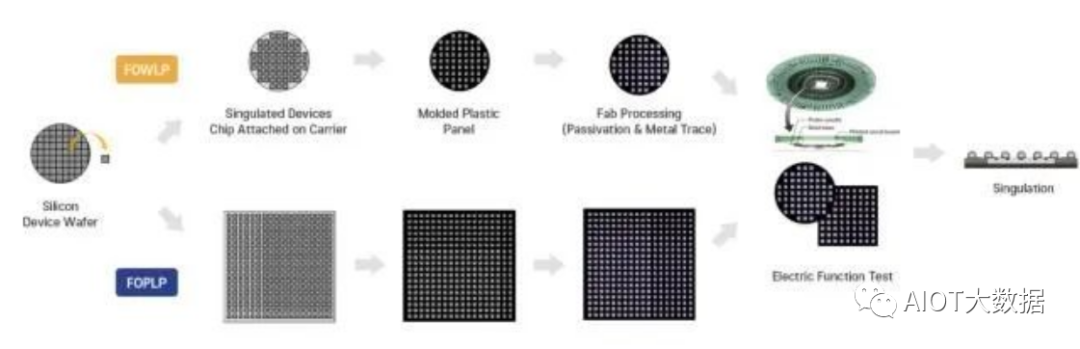

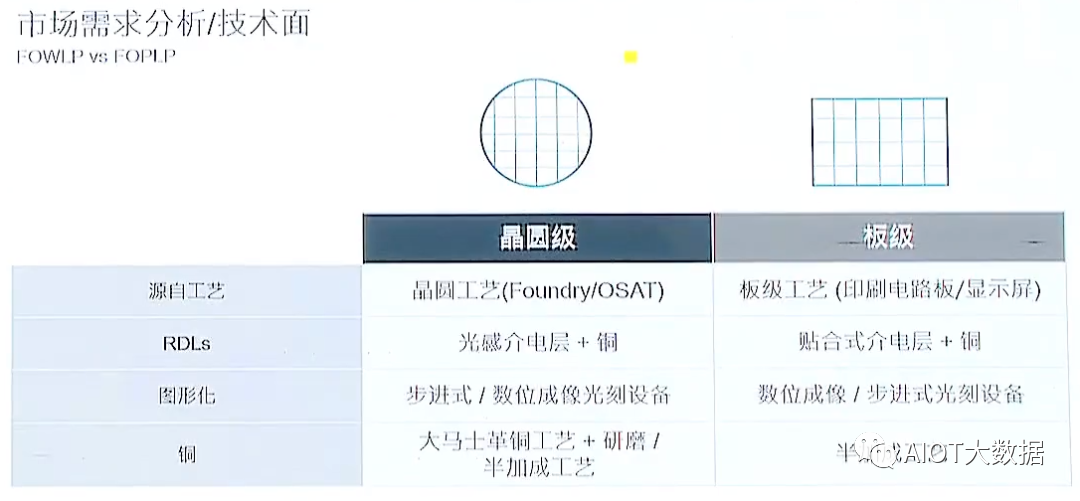

FOWLP與FOPLP工藝對比

iPhone7系列A10處理器InFO-PoP

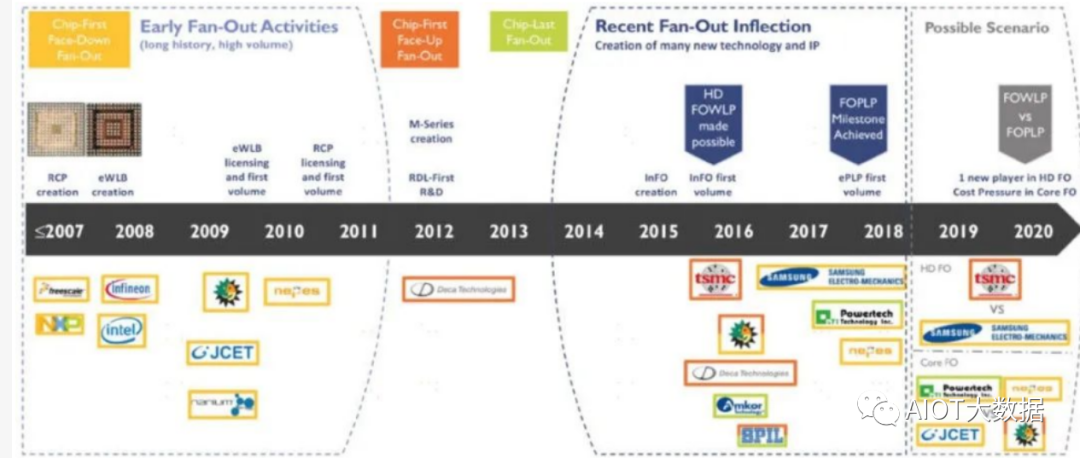

扇出型封裝技術演進

FOWLP封裝技術

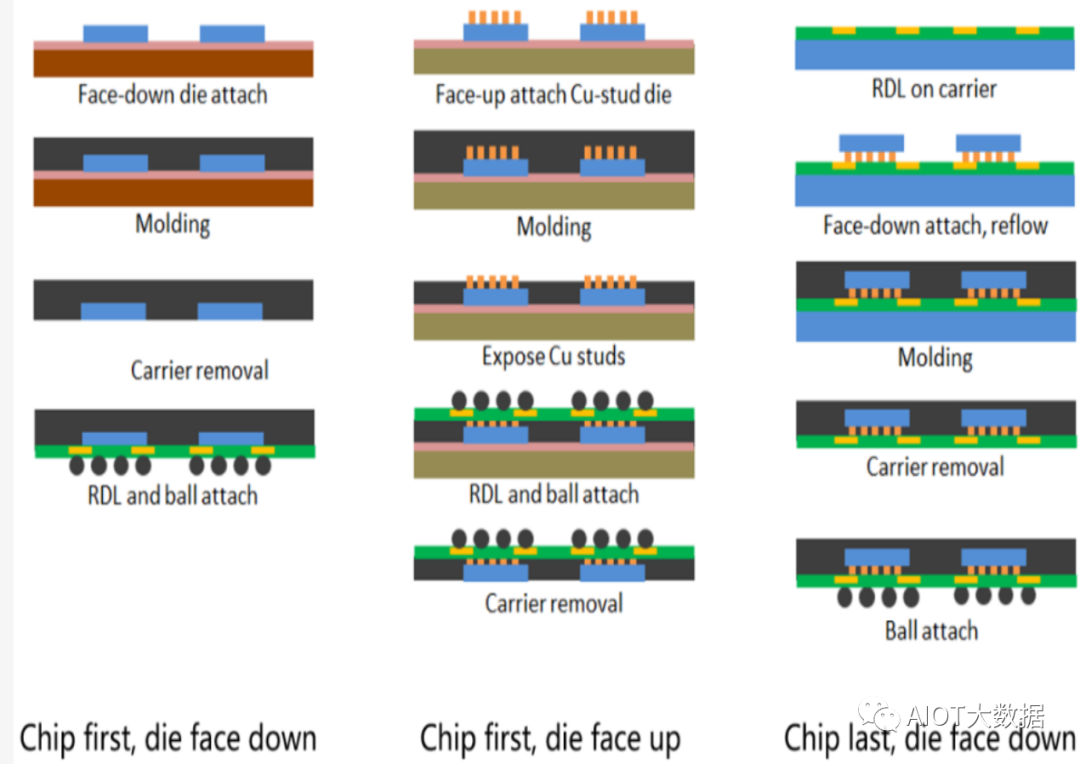

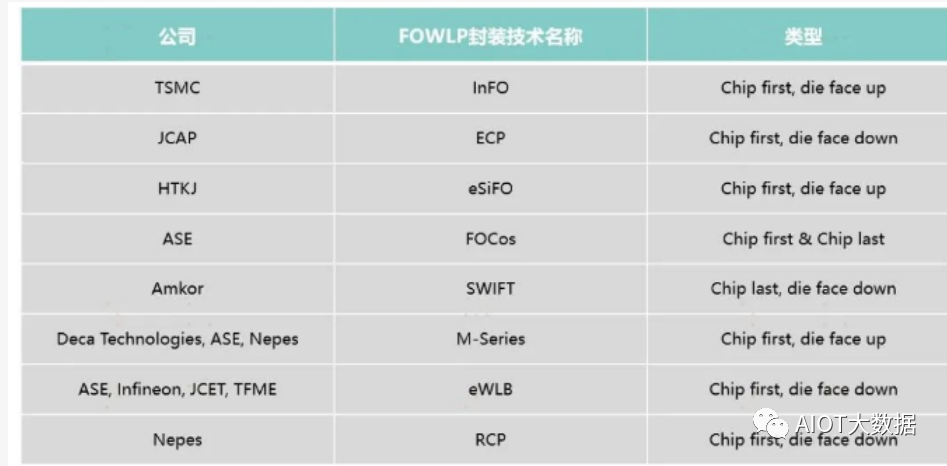

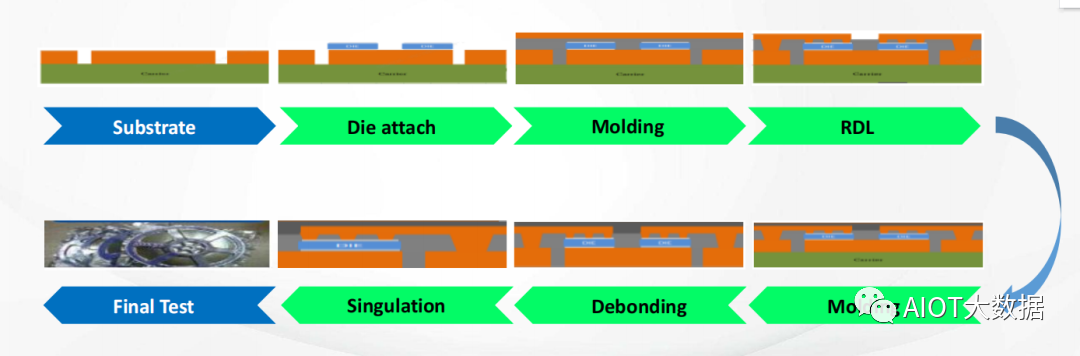

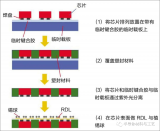

FOWLP封裝技術主要分為Chipfirst以及Chiplast,而Chipfirst可再分為Diefaceup(如DecaTechnologiesM-Series封裝)以及Diefacedown(RCP以及eWLB封裝等),Chiplast形式又被稱為RDLfirst,大致封裝流程可參考下圖:

☆Chipfirst,diefacedown封裝技術

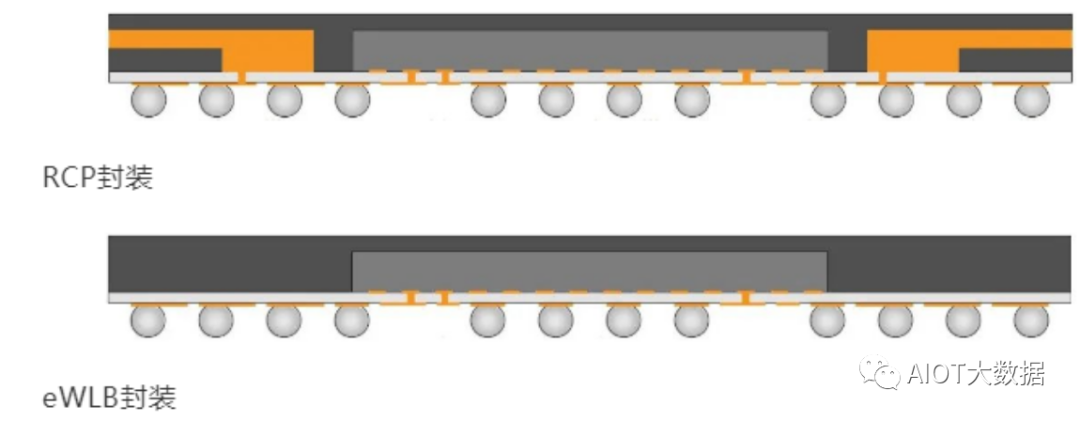

飛思卡爾于2006年左右推出重分布封裝(ReconsTItutedChipPackage:RCP),英飛凌于2007年左右推出嵌入式晶圓級BGA(EmbeddedWaferLevelBGA:eWLB)。

RCP與eWLB均為Chipfirst,diefacedown封裝,工藝流程類似,與eWLB不同的是,RCP包括一個銅框架層,有助于改善wafermolding過程中芯片偏移,另外可提供電磁屏蔽和散熱。

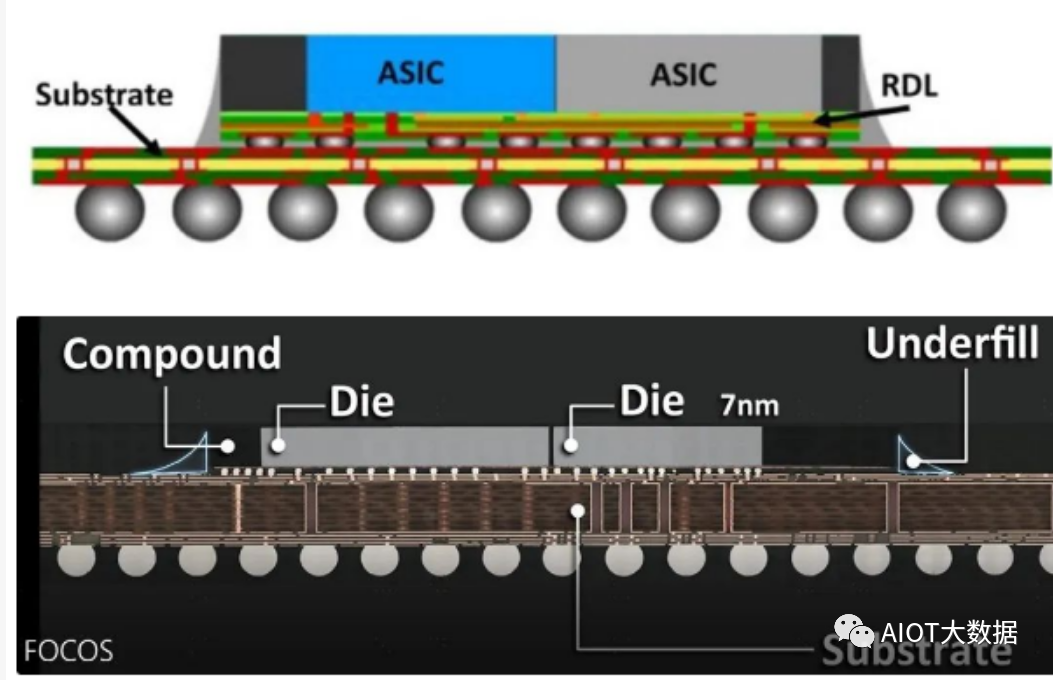

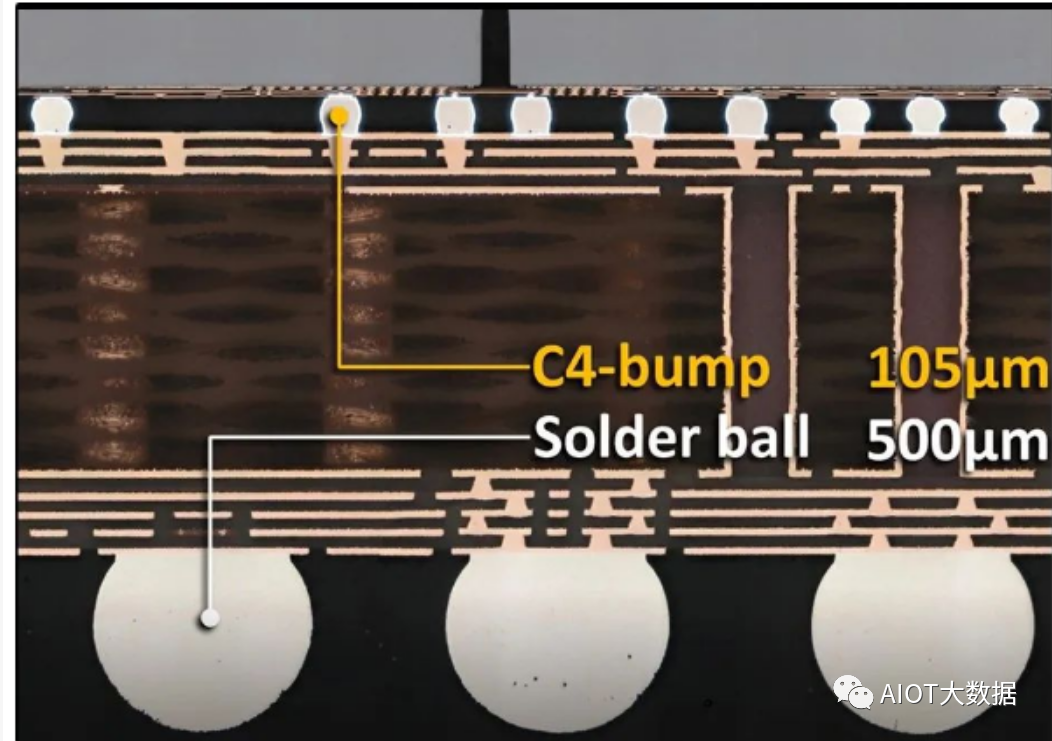

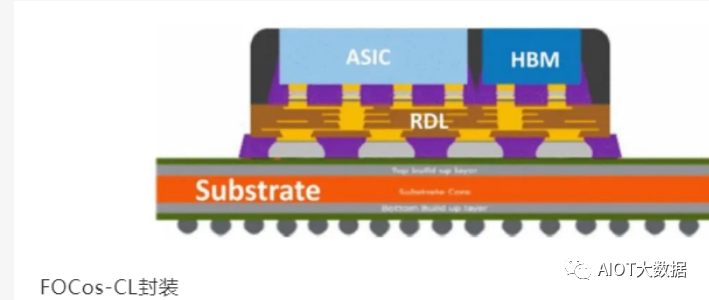

日月光自研的FOCos(Fan-OutChiponSubstrate)封裝同樣支持Chipfirst,diefacedown封裝技術。

FOCos-CF封裝

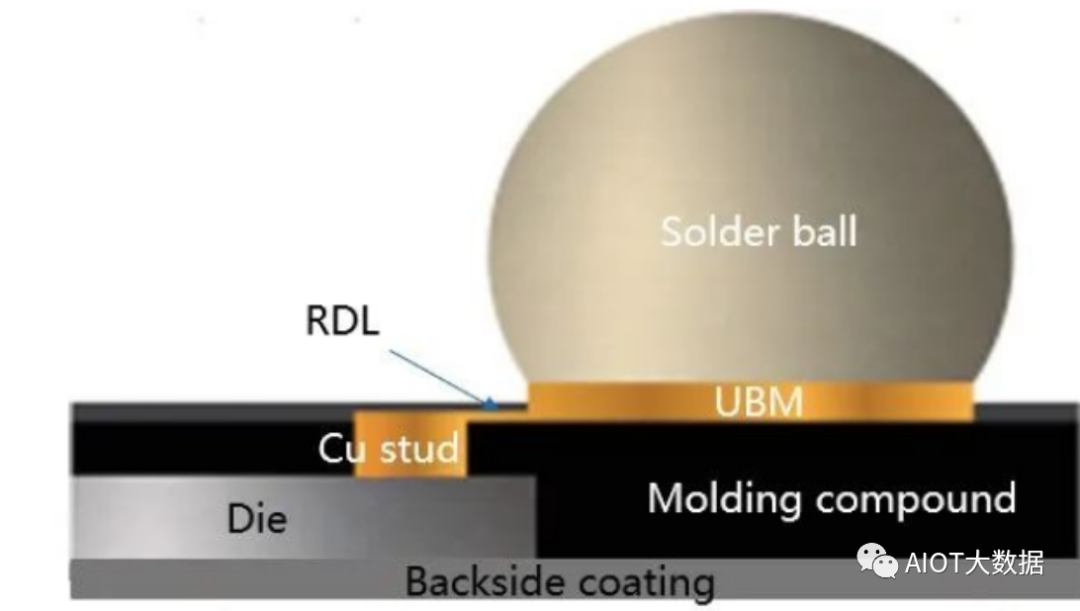

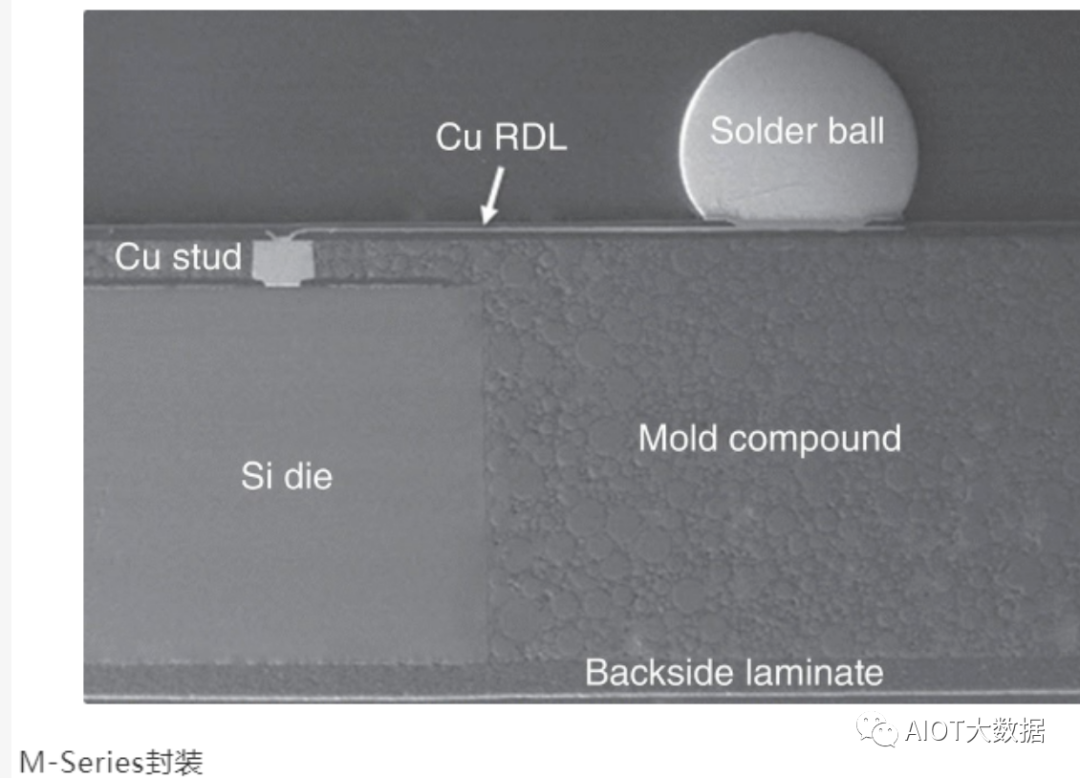

☆Chipfirst,diefaceup封裝技術

M-Series封裝技術由DecaTechnologies提出,TSMC于2016年推出的InFO封裝,同樣采用Chipfirst,diefaceup封裝技術。

Chipfirst,diefaceup主要優點:

(1)芯片背面貼DAF重組,貼裝后偏移較小;

(2)芯片背面貼裝,避免了Chipfirst,facedown情況下芯片邊緣由切割引入的不平整貼裝問題;

(3)更加平坦化,Wafermolding后進行Grinding研磨動作,消除了從芯片表面到Moldingcompound表面的不平整性。

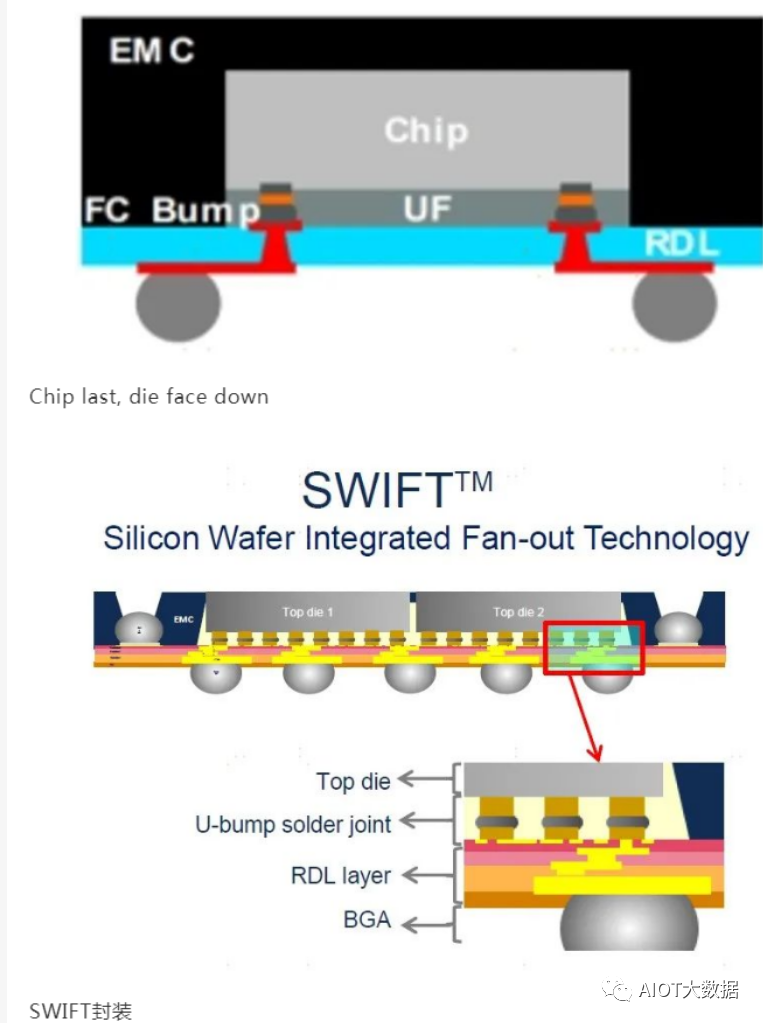

☆Chiplast(orRDLfirst),diefacedown封裝形式

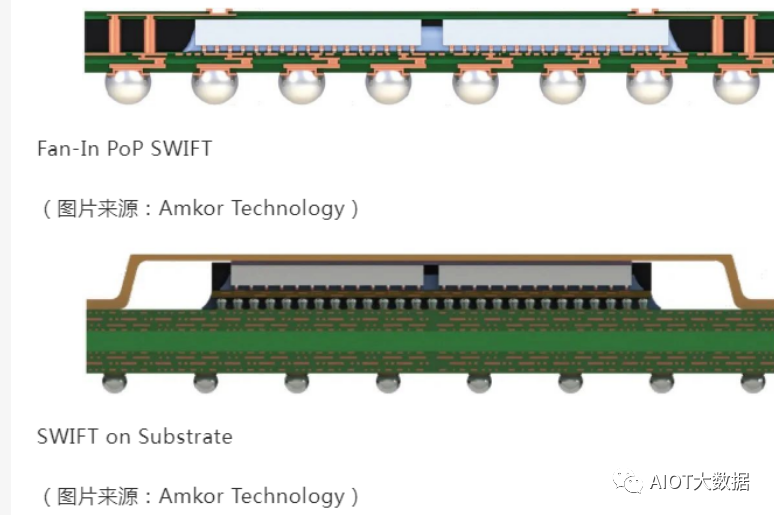

2006年左右由NECElectronicsCorporaTIon提出,Amkor于2015年推出的SWIFT(SiliconWaferIntegratedFan-OutTechnology)封裝采用RDLfirst技術,RDL線寬線距能力≤2um,μbumppitch40um,SWIFT封裝可實現多芯片集成的3DPOP封裝以及無需TSV(TSV-Less)具有成本優勢的HDFO高密度扇出型封裝,適用于高性能CPU/GPU,FPGA,MobileAP以及MobileBB等。

日月光自研的FOCos(Fan-OutChiponSubstrate)封裝同樣支持Chiplast,diefacedown封裝技術。

Chiplast(orRDLfirst),diefacedown主要優點:

(1)芯片只會在合格的RDL上倒裝芯片,可避免芯片損失,適用于高價格的高端芯片;

(2)芯片通過倒裝方式直接與RDL連接,消除了芯片偏移問題;

(3)超細RDL線寬線距實現HDFO,RDL線寬線距能力≤2um。

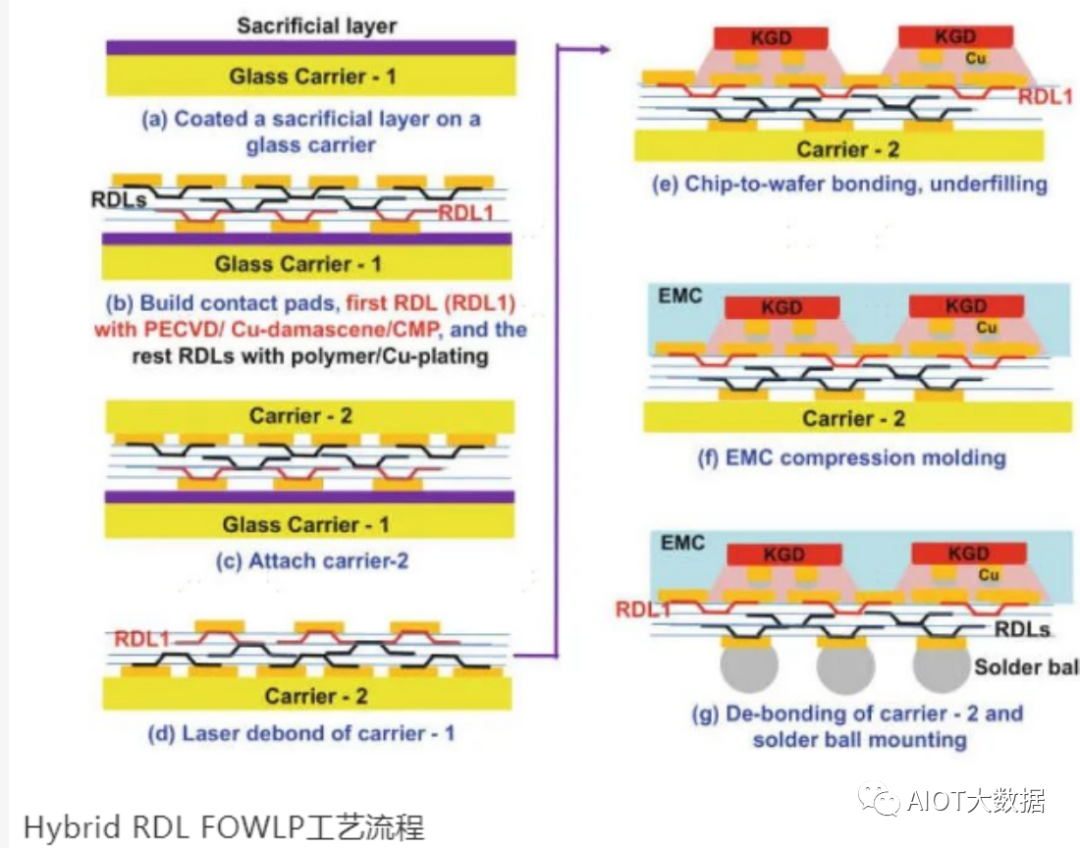

RDL制作方式可分為3種:第一種方式是通過PECVD制作SiO2或者SiN介電層以及Cu大馬士革方法制作RDL,RDL線寬線距能力≤2um;第二種方式是通過Polyimide制作介電層以及電鍍銅制作RDL,RDL線寬線距能力>2um;第三種方式結合了前兩種方式,又稱為HybridRDL。

☆支持FOWLP封裝技術主流公司

目前業內主流封裝廠以及TSMC都基于不同的技術特點開發出各自的FOWLP技術,如下圖所示。艾為基于自身產品的特點以及封裝廠的技術優勢,很早就已經開始關注FOWLP技術,并已經開始在一些產品上采用部分封裝廠的FOWLP技術,艾為目前采用FOWLP封裝技術的產品主要應用在電壓轉換器、音頻功率放大器、負載開關等。

FOPLP封裝技術

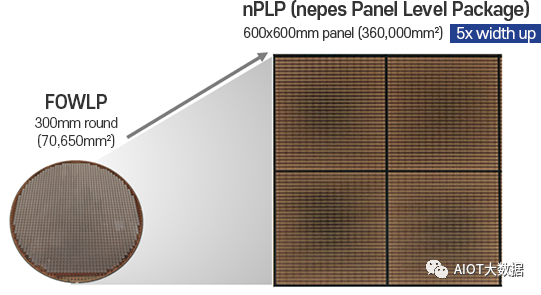

FOPLP封裝流程與FOWLP類似,IC載板由8寸/12寸wafercarrier轉換為大尺寸面板,以610mmX457mm尺寸面板為例,面積為12寸wafercarrier的3.9倍,單片產出數量為FOWLP的3.9倍,成本優勢較大。

FOPLP封裝技術的發展保持著高度的關注,目前也已經開始在部分產品上嘗試FOPLP技術,在不久的將來也會推出基于FOPLP封裝技術的產品。

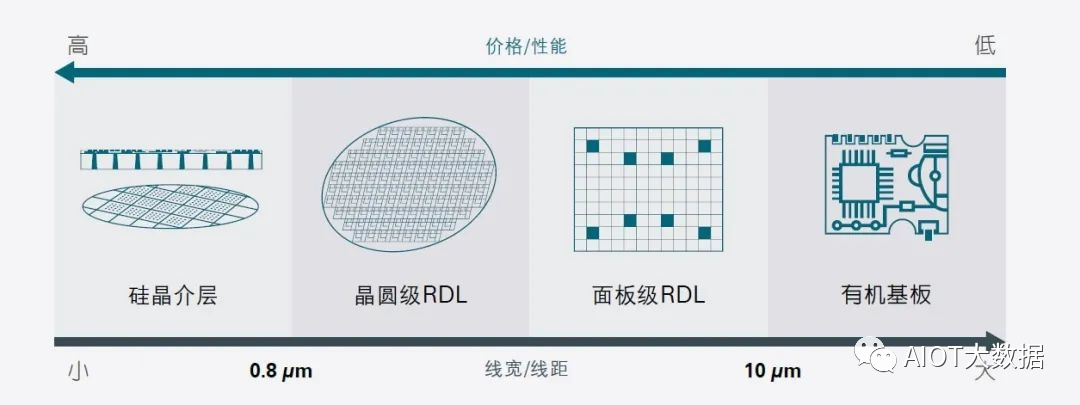

扇出型(Fan-Out)封裝等先進封裝成為延續摩爾定律的關鍵封裝技術,也為Chiplet技術提供了很好的基礎,可實現芯片體積微小化以及多芯片高密度集成,扇出型(Fan-Out)封裝關鍵挑戰點在于更小的微凸塊間距(μbumppitch:40um-30um-20um-10um),新型鍵合方式(TCB&NCP,TCB&NCF,HybridBonding等),以及更大的互連密度(RDLL/S:2/2um-1/1um-0.5/0.5um)。

新突破

隨著全球范圍內的芯片短缺問題日益嚴重和地緣政治局勢日益緊張,先進封裝技術在集成電路封裝市場中的地位變得越來越重要。2022年,先進封裝市場已經占據了整個集成電路封裝市場的48%,并且這個市場份額還在穩步增長。作為后摩爾時代提升芯片性能的關鍵,先進封裝技術的格局正在發生深刻的變化,這可能會給長久以來形成的封裝價值鏈帶來一定的風險和挑戰。

根據封裝技術的不同,Sowotech可以將先進封裝主要分為兩大類:基于XY平面延伸的先進封裝技術和基于Z軸延伸的先進封裝技術。在Chiplet級封裝中還將其細分為晶圓級封裝(WLP)和面板級封裝(PLP)。

FOPLP技術是FOWLP技術的延伸,它在更大的方形載板上進行Fan-Out制程,因此被稱為FOPLP封裝技術。與FOWLP工藝類似,FOPLP技術可以將封裝的前后段制程整合在一起,使其成為一次封裝制程,從而可以大幅度降低生產和材料的各項成本。

在新興應用場景的消費支撐下,FOPLP技術因兼具大產能及成本優勢,是功率半導體、傳感器、通信等車規級/芯片生產的最佳解決方案。電動車持續帶動國產車規級芯片市場需求,將促進板級封裝技術同步發展。

消費者對電子產品的高便攜性和多功能化追求,以及市場對AIoT、5G和智能駕駛IC結構緊湊、性能更好且更具成本效益的需要,導致了先進封裝技術的繁榮。過去數年,扇出型封裝是成長最為快速的先進封裝技術,扇出面板級封裝(FOPLP)是晶圓級扇出封裝的延伸,正在成為占領有具體需求的新興市場。

扇出面板級封裝(FOPLP)是指將半導體芯片重新分布在大面板上而不是使用單獨封裝的先進封裝技術。FOPLP能夠將多個芯片、無源元件和互連集成在一個封裝內,與傳統封裝方法相比,該技術提供了更大的靈活性、可擴展性和成本效益。

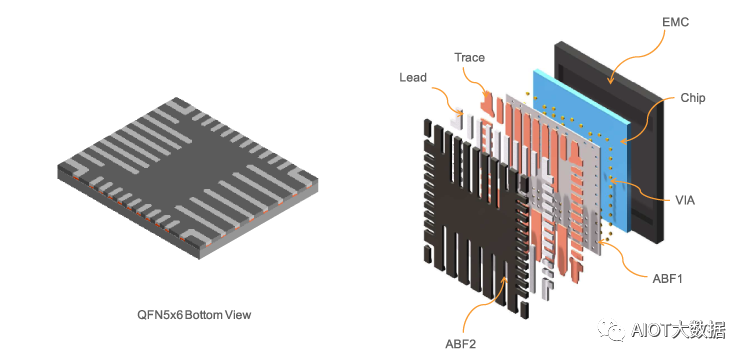

圖源:Nepes

圖源:Manz

對于FOPLP而言,采用方形面板作為封裝載板來代替采用晶圓作為載板封裝。這些方形載板的材質可以選擇金屬、玻璃和高分子聚合物材料。同時FOPLP利用了較大的基板尺寸。

提供具有成本效益的大尺寸互連,面板級有更高的產出效率、更少的物料損耗和更大的有效曝光面積。

就面積利用率而言,FOPLP高達95%,而FOWLP低于85%;

以主流12"/300mm晶圓與300mm正方形玻璃為載具做扇出型封裝,方型載具產量為晶圓的1.4倍。再以主流12”晶圓與主流方形載具尺寸約600mm相比,方形載具產量為晶圓的5.7倍;

Yole數據顯示,從200mm過渡到300mm大約能節省25%的成本,從300mm過渡到板級,則能節約66%的成本。

現階段不需要最先進制程和設備,也不需要太細的線寬/線距;

FOPLP還具有多種性能優勢,例如更高的器件密度、改進的電氣性能和增強的熱管理。

板級封裝相比傳統封裝在提升性能的同時,能夠大幅降低成本,因此板級封裝會代替傳統封裝成為Sensor、功率IC、射頻、鏈接模塊、PMIC等的最佳解決方案,如汽車中約66%的芯片價值可以使用FOPLP技術生產,是車規級芯片生產的出色解決方案。FOPLP技術具備巨大的成長潛力,預計未來幾年將出現顯著擴張,Yole數據顯示,2022年FOPLP的市場空間大約是11.8億美元,預計到2026年將增長到43.6億美元。

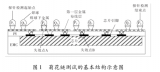

面板封裝產品結構圖源:華潤微

面板封裝扇出簡要工藝流程圖源:中科四合

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27290瀏覽量

218091 -

晶圓

+關注

關注

52文章

4890瀏覽量

127933 -

封裝

+關注

關注

126文章

7873瀏覽量

142894 -

封裝技術

+關注

關注

12文章

548瀏覽量

67981 -

扇出型封裝

+關注

關注

0文章

8瀏覽量

2743

原文標題:技術前沿:面板級封裝FOPLP

文章出處:【微信號:AIOT大數據,微信公眾號:AIOT大數據】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解扇出型晶圓級封裝技術

基于扇出型封裝結構的芯片失效位置定位方法

令人驚訝!Deca的扇出式封裝技術的新商業化

a型u***插座封裝_a型u***插座封裝尺寸

用于扇出型晶圓級封裝的銅電沉積

Mentor Graphics 提供對 TSMC 集成扇出型封裝技術的支持

扇出型封裝技術的發展歷史及其優勢詳解

FPGA Fanout-Fanin(扇入扇出)資料解析

日月光扇出型封裝結構有效提升計算性能

扇出型晶圓級封裝技術的優勢分析

解析扇入型封裝和扇出型封裝的區別

解析扇入型封裝和扇出型封裝的區別

評論