1 簡介

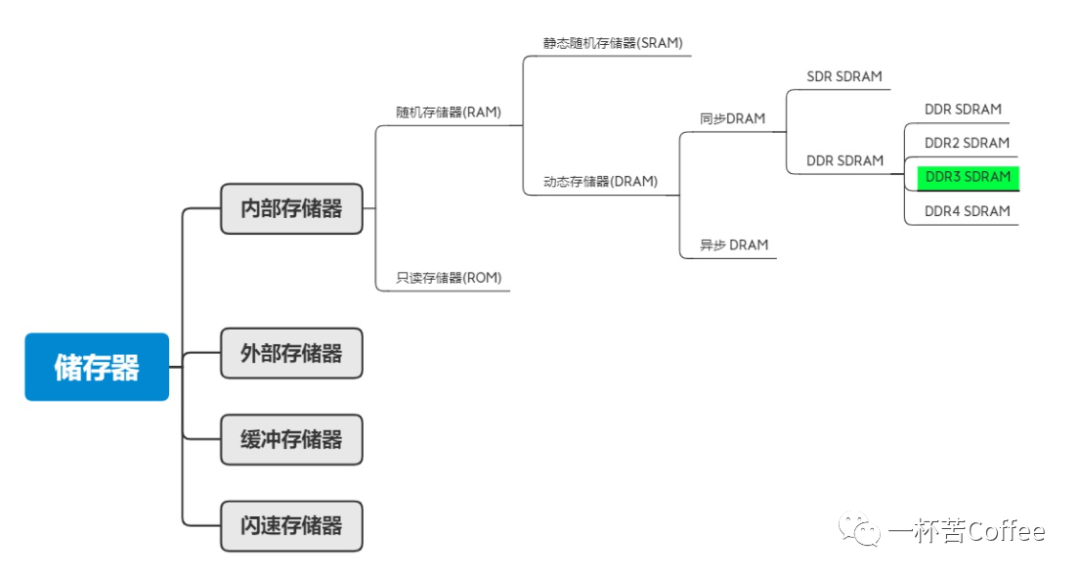

本文主要講述一下DDR從0到1設計的整個設計的全過程,有需要的朋友可先安排收藏。內容涵蓋以下部分:

DDR4級聯

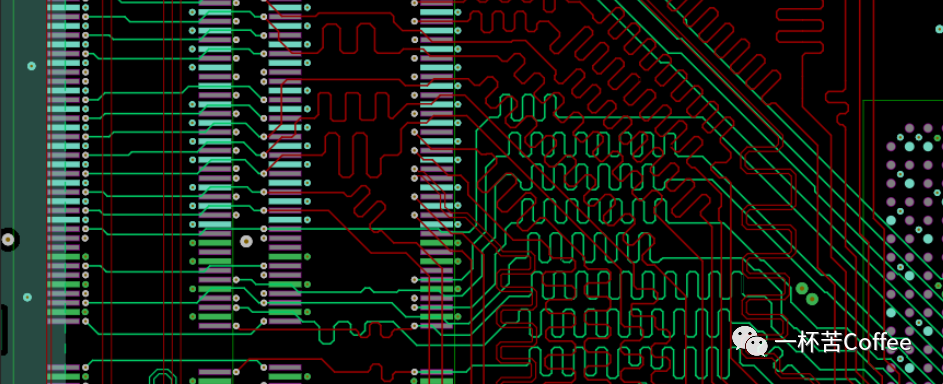

DDR4 Layout注意事項(內容太多,可能下一章節分享)

2 DDR4的級聯

本節主要講述DDR的級聯,主要分為三個實戰案例進行講解,分別是2片16位DDR4級聯、4片16位DDR4+1片8位DDR4級聯、兩組5片16位DDR4級聯。相信通過本章節的講解,大部分朋友都會對DDR的級聯有一個深刻的認識。

2.1 2片16位DDR4級聯

選用的DDR芯片是鎂光的MT40A256M16GE-083E,2片16位DDR4級聯,每個顆粒的位寬位16bit,級聯的示意圖見下:

16位DDR4顆粒1電路圖如下:

16位DDR4顆粒1電路圖如下:

總結:

兩個16位DDR4顆粒級聯時,地址線完全復用,具體包括地址線A[13:0]、BA[1:0]和BG0,地址線需要39.2Ω,精度1%電阻上拉至VTT,每個上拉電阻附近需要放置一個0.1uF電容,且VTT需要有uF級別大電容。

兩個16位DDR4顆粒級聯時,控制線完全復用,具體包括寫保護(WE_B)、行選通信號(RAS_B)、列選通信號(CAS_B)、復位信號(RESET_B)、片內短接信號(ODT)、片選引腳(CS)、激活信號(ACT_B)、警告信號(ALERT_B)、奇偶檢驗信號(PAR),另外測試信號分別連接499Ω電阻至GND,警告信號(ALERT_B)需要上拉至1.2V。

兩個16位DDR4顆粒級聯時,時鐘線完全復用,具體包括CK_T、CK_C、CKE,特別地,時鐘信號需要連接36R,精度1%的電阻,然后串接0.01uF電容值1.2V;

注意:

這是一種末端短接匹配的一種方式(串始并末:串聯端接一般放置在信號源端,并連端接一般放置在信號接收端)

直接上拉至主電源即可。

兩個16位DDR4顆粒級聯時,電源可以復用,具體包括VDD、VDDQ、VPP、REFCA,兩個顆粒的ZQ信號需要分別連接240Ω電阻至GND。此處REFCA使用專用芯片產生:

所有的數據線均不復用,具體見下:

注意:HP BANK中LVDS的供電要求為1.8V;HR BANK中LVDS的供電要求為2.5V。

2.2 4片16位DDR4+1片8位DDR4級聯

選用的DDR芯片是鎂光的MT40A512M16LY-075E,其中4片16位DDR4+1片8位DDR4,總數據位寬高達72bit,級聯的示意圖見下:

16位DDR4顆粒1電路圖如下:

16位DDR4顆粒2電路圖如下:

16位DDR4顆粒3電路圖如下:

16位DDR4顆粒4電路圖如下:

8位DDR4顆粒5電路圖如下:

總結:

兩個16位DDR4顆粒級聯時,地址線完全復用,具體包括地址線A[13:0]、BA[1:0]和BG0,地址線需要39.2Ω,精度1%電阻上拉至VTT,每個上拉電阻附近需要放置一個0.1uF電容,且VTT需要有uF級別大電容。

* 兩個16位DDR4顆粒級聯時,控制線完全復用,具體包括寫保護(WE_B)、行選通信號(RAS_B)、列選通信號(CAS_B)、復位信號(RESET_B)、片內短接信號(ODT)、片選引腳(CS)、激活信號(ACT_B)、警告信號(ALERT_B)、奇偶檢驗信號(PAR),另外測試信號分別連接499Ω電阻至GND,警告信號(ALERT_B)需要上拉至1.2V。

* 兩個16位DDR4顆粒級聯時,控制線完全復用,具體包括寫保護(WE_B)、行選通信號(RAS_B)、列選通信號(CAS_B)、復位信號(RESET_B)、片內短接信號(ODT)、片選引腳(CS)、激活信號(ACT_B)、警告信號(ALERT_B)、奇偶檢驗信號(PAR),另外測試信號分別連接499Ω電阻至GND,警告信號(ALERT_B)需要上拉至1.2V。

兩個16位DDR4顆粒級聯時,時鐘線完全復用,具體包括CK_T、CK_C、CKE,特別地,時鐘信號需要連接36R,精度1%的電阻,然后串接0.01uF電容值1.2V;

注意:

這是一種末端短接匹配的一種方式(串始并末:串聯端接一般放置在信號源端,并連端接一般放置在信號接收端)

直接上拉至主電源即可。

兩個16位DDR4顆粒級聯時,電源可以復用,具體包括VDD、VDDQ、VPP、REFCA,兩個顆粒的ZQ信號需要分別連接240Ω電阻至GND。此處REFCA使用電阻分壓方式產生,這種放置最明顯的優勢是在布局時比較靈活:

- 所有的數據線均不復用,具體見下:

注意:

HP BANK中LVDS的供電要求為1.8V;HR BANK中LVDS的供電要求為2.5V。

最后一個顆粒的高8位數據線未使用,需要特別注意。

2.3 兩組5片16位DDR4級聯

這種級聯方式與前面的有所不同,前面的級聯方式不管多少顆粒都是同一組DDR,但是這種級聯方式采用的是兩組DDR設計,這種設計的方式看似比較復雜,其實兩組DDR可以分開來進行分析,兩組DDR完全獨立,不存在復用的引腳。我們在進行電路分析時,只需要分析其中一組DDR電路即可。

16位顆粒1和顆粒2電路圖見下:

16位顆粒3和顆粒4電路圖見下:

16位DDR顆粒5電路圖見下:

總結:

兩個16位DDR4顆粒級聯時,地址線完全復用,具體包括地址線A[13:0]、BA[1:0]和BG0,地址線需要39.2Ω,精度1%電阻上拉至VTT,每個上拉電阻附近需要放置一個0.1uF電容,且VTT需要有uF級別大電容。

兩個16位DDR4顆粒級聯時,控制線完全復用,具體包括寫保護(WE_B)、行選通信號(RAS_B)、列選通信號(CAS_B)、復位信號(RESET_B)、片內短接信號(ODT)、片選引腳(CS)、激活信號(ACT_B)、警告信號(ALERT_B)、奇偶檢驗信號(PAR),另外測試信號分別連接499Ω電阻至GND,警告信號(ALERT_B)需要上拉至1.2V。

兩個16位DDR4顆粒級聯時,時鐘線完全復用,具體包括CK_T、CK_C、CKE,特別地,時鐘信號需要連接36R,精度1%的電阻,然后串接0.01uF電容值1.2V;

注意:

這是一種末端短接匹配的一種方式(串始并末:串聯端接一般放置在信號源端,并連端接一般放置在信號接收端)

直接上拉至主電源即可。

兩個16位DDR4顆粒級聯時,電源可以復用,具體包括VDD、VDDQ、VPP、REFCA,兩個顆粒的ZQ信號需要分別連接240Ω電阻至GND。此處REFCA使用電阻分壓方式產生,這種放置最明顯的優勢是在布局時比較靈活:

所有的數據線均不復用。

注意:

HP BANK中LVDS的供電要求為1.8V;HR BANK中LVDS的供電要求為2.5V。

-

電路圖

+關注

關注

10403文章

10732瀏覽量

541019 -

電路設計

+關注

關注

6700文章

2524瀏覽量

212272 -

DDR

+關注

關注

11文章

731瀏覽量

66423 -

DDR4

+關注

關注

12文章

329瀏覽量

41548 -

DDR芯片

+關注

關注

0文章

5瀏覽量

1855

發布評論請先 登錄

怎么成為硬件電路設計高手?

【高手問答】第3期——走進硬件電路設計

硬件電路設計的思路分享

硬件電路設計之“磁珠”的應用資料下載

評論