不論數字信號的上升沿是抖還是慢,在信號跳變時,總會有一段過渡時間處于邏輯判斷閾值的上限和下限之間,從而造成邏輯的不確定狀態,更糟糕的是,通常的數字信號都不止一路,可能是多路信號一起傳輸來代表一些邏輯和功能狀態,這些多路信號由于電氣特性的不完全一致,以及PCB走線路徑的長短不同,在到達其接收端時還會存在不同的延時,延時的不同會進一步增加邏輯狀態的不確定性。

1、同步電路

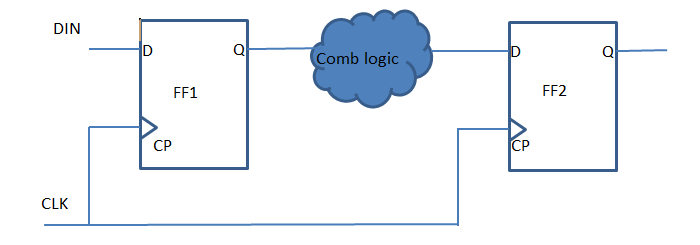

同步電路示意圖

由于我們感興趣的邏輯狀態通常是信號電平平穩以后的狀態,而不是跳變時刻的狀態,所以現在大部分數字電路都采用同步電路,即系統中有一個統一的工作時鐘對信號進行采樣,雖然信號在跳變過程中可能有不確定的邏輯狀態,但是如果只在時鐘的上升沿對進行進行判決采樣,則得到的就是穩定的邏輯狀態。

采用同步時鐘的電路減少了出現邏輯狀態不確定的可能性,而且可以減小電路和信號布線延時的累積效應,所以在現代的數字系統和設備中廣泛采用,在采用同步電路以后,數字電路以一定的時鐘節拍來工作,我們把數字信號以每秒鐘跳變的最大速率叫做信號的數據速率(單位通常是bps或者bit/s),大部分并行總線的數據速率和系統中時鐘的工作頻率一致,也有一些特殊場合采用DDR方式(Double Data rate ),即數據速率是時鐘工作頻率的2倍。

2、建立/保持時間

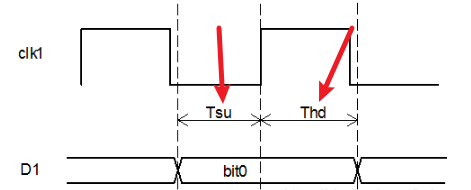

建立時間/保持時間示意圖

在同步電路中,如果要得到穩定的邏輯狀態,對于采樣時鐘和信號間的時序關系是有要求的,如果時鐘信號的有效邊沿正好對應數據的跳變區域附近,可能會采樣到不可靠的邏輯狀態,數字電路要得到穩定的邏輯狀態,通常都要求在采樣時鐘有效邊沿到來時被采信號已經提前建立一個新的邏輯狀態,這個提前的時間通常被稱為 建立時間(setup time) ,同樣的,在采樣的時鐘的有效邊沿到來后,被采的信號還需要保持在這個邏輯狀態一定時間以保證采樣數據的穩定,這個時間通常被稱為保持時間(hold time)。

3、建立/保持時間對數字電路的影響

建立時間和保持時間相加起來的時間叫做建立/保持時間窗口,是接收端對于信號要保持在同一個邏輯狀態的最小時間要求,數字信號的比特寬度如果窄于建立/保持時間窗口就無法同時滿足建立時間/保持時間的要求,所以接收端對于建立保持時間窗口的要求實際上決定了這個電路能夠工作的最高數據速率,通常工作速率高一些的芯片,很短的建立時間、保持時間就可以保證電路可靠工作,而工作速率低一些的芯片則會要求比較長的建立時間/保持時間。

建立時間和保持時間是數字電路非常重要的概念,是接收端對于可靠信號接收的最基本要求,也是數字電路可靠工作的基礎,可以說,大部分數字信號的測量項目(數據速率、眼圖、抖動)的測量都是為了間接保證信號滿足接收端對建立時間和保持時間的要求。

-

數字信號

+關注

關注

2文章

998瀏覽量

48391 -

數字電路

+關注

關注

193文章

1641瀏覽量

81977 -

建立時間

+關注

關注

0文章

10瀏覽量

6681 -

保持時間

+關注

關注

0文章

10瀏覽量

5794

發布評論請先 登錄

芯片設計進階之路—從CMOS到建立時間和保持時間

數字電路中,建立時間和保持時間對于觸發器的時鐘信號有

建立時間和保持時間討論

保持時間與建立時間

為什么觸發器要滿足建立時間和保持時間

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

關于建立時間和保持時間的測量方法

評論