增加3D(三維)NAND閃存密度的方法正在發生變化。這是因為支持傳統高密度技術的基本技術預計將在不久的將來達到其極限。2025 年至 2030 年間,新的基礎技術的引入和轉化很可能會變得更加普遍。

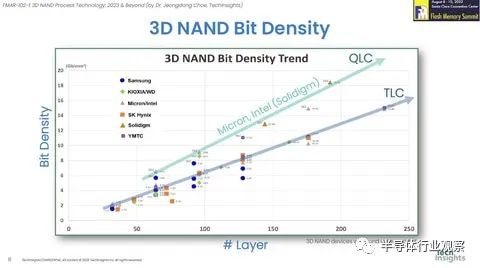

自2013年3D NAND閃存開始商業化生產以來,存儲密度以每年1.41倍左右的速度持續提升。從國際會議 ISSCC 上展示的原型硅芯片來看,2014 年存儲密度為每平方毫米 0.93 Gbit,但 2024 年將達到每平方毫米 28.5 Gbit。簡單對比一下,10年間存儲密度增加了30.6倍。

提高3D NAND閃存存儲密度的四項基本技術

迄今為止,3D NAND閃存的存儲密度主要通過采用四種基本技術(方法)來提高。它們是“高層建筑”、“多值轉換”、“布局改變(存儲單元陣列和CMOS外圍電路的單片堆疊)”和“小型化(縮短橫向尺寸)” 。

2013年宣布開發和商業化時,3D NAND的層數為24層,從今天的角度來看,這似乎很小。盡管如此,當時的制造極其困難,業內人士傳言,第二年決定開始商業化生產的三星電子的制造良率還不到一半。

之后,堆棧的數量迅速增加。四年后,即 2017 年,這個數字翻了兩番,達到 96 個。八年后,即2022年,達到了238層,大約增加了10倍,而次年,即2023年,則突破了300層。

由于增強型多級存儲器,存儲器密度是平面 NAND 的 1.5 至 2 倍

簡單對比一下,“高層”對存儲密度的貢獻“10年大約是10倍”。然而,正如已經提到的,實際上,這個數字在10年內增加了大約30倍。其余三倍的提升都是通過其他基礎技術實現的。

一個代表性的例子是“多值”。平面(2D)NAND閃存中開始引入的多級存儲一直以2位/單元(MLC)方法為主,而3位/單元(TLC)方法仍然處于邊緣地位。除了3D NAND閃存的第一個原型是MLC之外,TLC從一開始就成為主流。與平面NAND閃存相比,存儲密度提高了1.5倍。

3D NAND閃存進一步發展了多級存儲技術,并將4bit/cell(QLC)方法投入實際應用。這相當于平面 NAND 閃存 (MLC) 存儲密度的兩倍,是現有 3D NAND 閃存 (TLC) 存儲密度的 1.33 倍。

改變布局的巨大威力

我們能夠確認,通過“高層建筑”和“多值(強化)”,存儲密度將增加10倍×2倍(最大)或20倍。當您達到“30 倍”時,剩下的就是“1.5 倍”。這就是第三個基本技術“布局改變(存儲單元陣列和 CMOS 外圍電路的單片堆疊)”發揮作用的地方。

這個想法很簡單:在布局更改之前,存儲單元陣列和 CMOS 外圍電路并排布局在硅芯片上。存儲單元陣列的底部有一塊硅基板,但里面沒有內置任何電路。可以說,這里已經變成了一塊“空地”。

通過在該空余空間中形成CMOS外圍電路,將減少硅面積。當然,可以通過僅在存儲單元陣列下方形成一些而非全部CMOS外圍電路來增加存儲密度。換句話說,存儲密度的提高速度是由布局決定的。

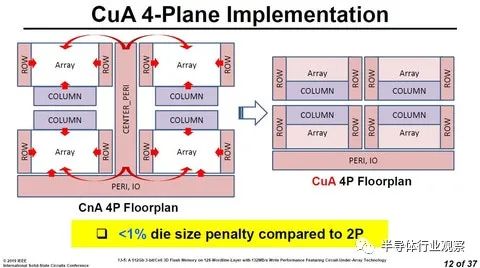

例如,東芝存儲器(現Kioxia)與西部數據(以下簡稱WD)聯合開發團隊在2019年國際會議ISSCC上公布的3D NAND閃存,其存儲單元陣列具有兩個平面(劃分數)除了將平面數量從1個增加到4個之外,大部分CMOS外圍電路都形成在存儲單元陣列正下方的硅襯底上。

注意,增加平面分割的數量的目的是為了提高操作速度或者緩解操作速度的下降。

增加平面劃分的數量會增加行(ROW)解碼器和列(COLUMN)解碼器的數量并增加硅面積。東芝內存-WD聯盟表示,從2個平面改為4個平面將使硅芯片面積增加15%。

如果將CMOS外圍電路直接布置在存儲單元陣列下方,則硅芯片面積的增加可以保持在僅1%。簡單計算一下,存儲密度提升了12%左右。

使用傳統技術的高密度限制

隨著存儲密度的增加,這些傳統技術在技術上變得更加困難。開發下一代 3D NAND 閃存就像攀登永無止境的斜坡,隨著進步,斜率也會越來越大。

各大NAND Flash公司自開發以來,經過反復的換代,目前的世代已經達到了第6代至第8代。斜坡已經變得相當陡峭,公司正在認真尋找替代路線(基本技術)。

讓我們簡要討論一下每項基本技術的問題。

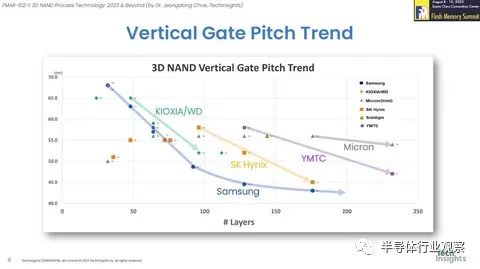

第一步是“高層建筑”。由于字線提取區域的擴大而導致效率降低,由于層數增加(垂直劃分存儲單元陣列的單元,也稱為甲板或插頭)而導致對準難度增加,工藝步驟數量增加以及字線變細。其中包括字線電阻的增加(一種緩解高層結構導致的存儲器通孔深寬比增加的方法)、上下相鄰單元之間的電干擾增加以及字線數量的減少。每個單元的電荷(電子)。

接下來我們來說說“多層次”的局限性。多級存儲技術有一個固有的弱點,即隨著位數的增加,效率下降,技術難度迅速增加。

從 1 位/單元 (SLC) 到 2 位/單元 (MLC) 的轉變原則上使存儲密度加倍。在隨后從 MLC 到 3 位/單元 (TLC) 的轉變中,存儲密度的增長率大幅降低至 1.5 倍。從TLC到4bit/cell(QLC)的過渡中,存儲密度的增加率更低,為1.33倍。

另一方面,閾值電壓階躍的數量每 1 位加倍。TLC 有 8 個步驟(7 個步驟,不包括擦除),QLC 有 16 個步驟(15 個步驟,不包括擦除)。如果寫入(編程)電壓范圍相同,則增加 1 位將使閾值電壓裕度減少一半。盡管QLC已經商業化生產,但PLC的實際應用仍不清楚。

接下來是“布局變更(存儲單元陣列和CMOS外圍電路的單片堆疊)”。這種方法有兩個主要缺點。一是一旦在一代引入,即使在下一代引入,效果也保持不變。其次,由于存儲單元陣列是在形成CMOS外圍電路之后制造的,所以在存儲單元陣列工藝期間施加的熱處理降低了CMOS外圍電路的性能。換句話說,存在運行速度降低的風險。

CMOS外圍電路的性能下降和存儲單元陣列的熱處理溫度之間存在折衷關系。外圍電路和單元陣列的性能很難同時優化。此外,更高結構的進步可能會進一步惡化由于存儲單元陣列的熱處理而導致的外圍電路的性能惡化。

最后一步是小型化。當垂直溝道(存儲器通孔)做得更薄時,溝道電阻會增加。這導致單元晶體管的性能下降。垂直通道的直徑只能減小到一定程度。

突破高密度極限的基礎技術候選組

解決上述限制和問題的基本技術已經被提出,并且研究和開發正在進行中。下面我們來介紹其中的一些。

將“超越高層建筑極限”的候選基礎技術包括將字線金屬從目前的鎢(W)改為電阻率較低的金屬(緩解字線電阻的增加),以及垂直溝道材料。由現在的多晶硅改為單晶硅(緩解溝道電阻的增加),將電荷俘獲柵極絕緣膜由現在的氮氧化物膜改為鐵電膜(不依賴于電子數量的介電膜) ). 除了目前存儲單元陣列各層(甲板、插頭)之間的單片連接外,還將引入混合(晶圓鍵合)(緩解工藝難度的增加)。

將“超越多值技術極限”的基本技術候選包括將單元晶體管的存儲方法從當前的電荷陷阱技術改為浮動柵極技術(緩解閾值電壓裕度降低)(增加將5-位/單元(PLC)系統投入實用)。

混合堆疊是一種候選基本技術,“超越了布局變化的限制(存儲單元陣列和CMOS外圍電路的單片堆疊)”。存儲單元陣列和CMOS外圍電路形成在不同的晶片上,并且將晶片接合在一起。這樣做的優點是可以優化存儲單元陣列和CMOS外圍電路工藝。隨著每個輸入/輸出引腳的傳輸速率超過 5 GT/s,引入混合堆疊的可能性就會增加。

擁有替代技術的候選者非常重要,即使它們不完整,以防當前技術達到其極限。3D NAND閃存的高密度尚未達到極限。通過改進新的基本技術,甚至可以達到 1,000 層。這完全取決于你能在多大程度上投入你的資源。

審核編輯:湯梓紅

-

芯片

+關注

關注

455文章

50714瀏覽量

423151 -

閃存

+關注

關注

16文章

1782瀏覽量

114895 -

NAND

+關注

關注

16文章

1681瀏覽量

136120 -

3D

+關注

關注

9文章

2875瀏覽量

107485 -

存儲器

+關注

關注

38文章

7484瀏覽量

163764

原文標題:3D NAND,如何發展?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

提高3D NAND閃存存儲密度的四項基本技術

提高3D NAND閃存存儲密度的四項基本技術

評論