結終端技術(Junction Termination Technology,JTT):

結終端技術是通過緩解或者避免電場集中效應而提高耐壓的技術。(器件耐壓一般由表面擊穿電壓決定)

橫向功率集成器件的結終端技術:

一類是在主結附近引入電荷,利用電荷產生的附加電場來調制電場,降低主結的電場峰值,并擴展耗盡區寬度,從而獲得優化的電場分布,此類技術通常用平面工藝,常見的包括場板及結終端擴展。

另一類是去除曲率大,電場集中的結面部分,如采用刻蝕去除電場集中的半導體區域,或者刻槽并填充絕緣介質,將高電場轉移至臨界擊穿電場更高的絕緣介質中,從而提高擊穿電壓,稱為溝槽終端技術。

設計與制造中常常將兩種以上的結終端技術組合使用,形成復合終端技術以提高耐壓并縮小終端面積,同時提高器件的可靠性。

.1場板技術(Field Plate,FP)

場板技術工藝相對簡單且工藝兼容性好,是目前最重要和最常用的結終端技術之一。

基本原理:引入電荷產生附加電場,減小原來的電場峰值,同時使耗盡層擴展。

廣義的場板可分為三類:

1.金屬場板,金屬覆蓋于半導體表面的絕緣介質上且一端接固定電位,如接源的源場板,接柵的柵場板,接漏的漏場板。

2.浮空場板,其未與電極相連,無固定電勢,處于浮空的狀態

3.阻性場板,也稱電阻場板,通常采用半絕緣多晶硅(Semi-Insulating Polycrystalline Silicon,SIPOS),其兩端分別與器件的兩個電極相連,因為場板本身不絕緣且兩端存在電勢差,在阻性場板兩端之間就有電流流過,從而在電流流過的方向形成壓降,調整器件表面電場分布。

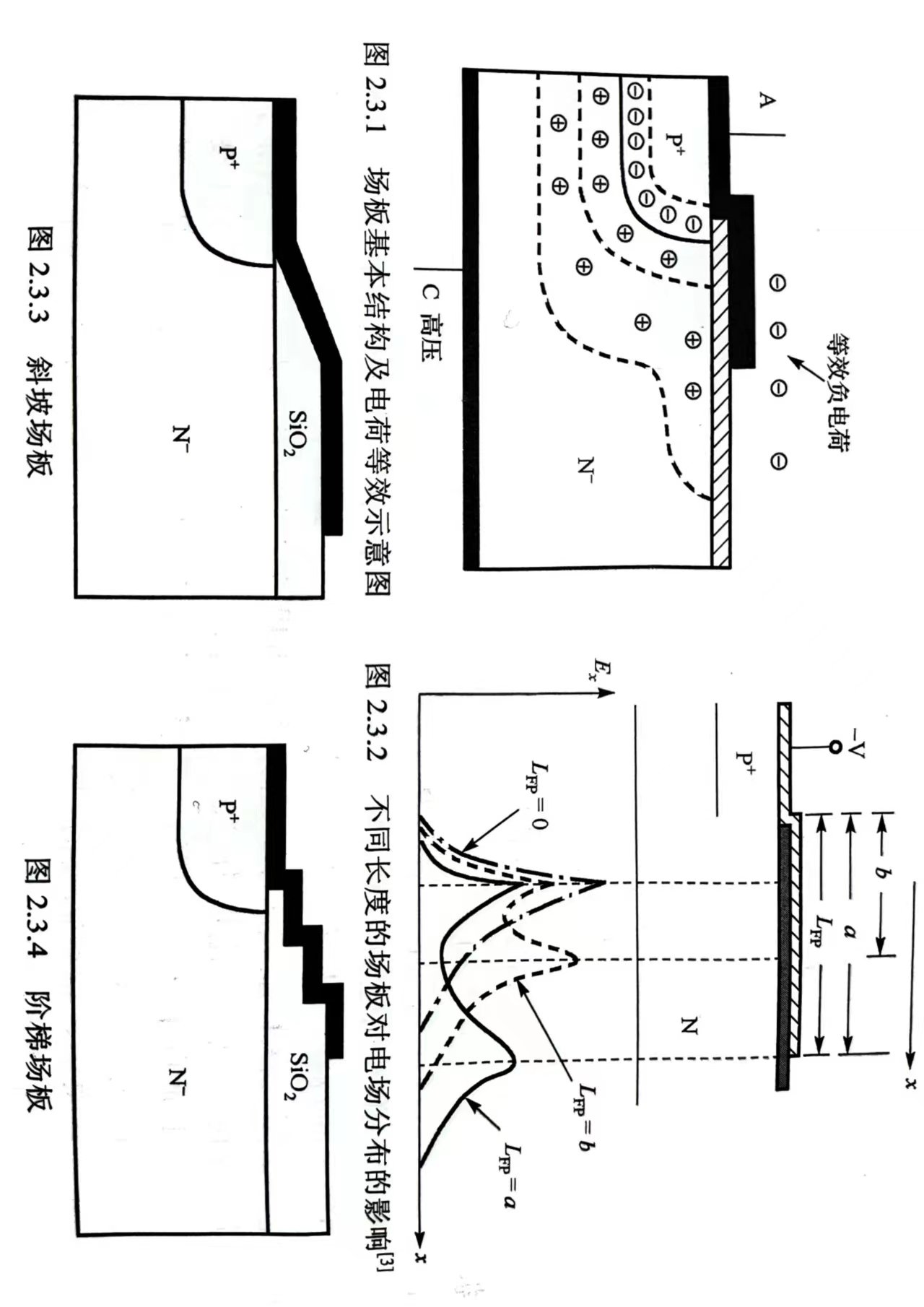

場板的作用是通過將一部分原本由N耗盡區正電荷指向表面出P+耗盡區負電荷的電場線轉向場板,從而降低主結處的電場峰值,緩解電場集中的現象,同時展寬耗盡區,如圖.1虛線所示。這種作用可以等效在半導體表面之上增加了一層負電荷,N區正電荷發出電力線部分終止于表面的負電荷,保證電通量不變。這些負電荷會產生垂直于硅層表面的電場以及平行于半導體表面兩個方向的電場。在場板下方多數區域內,這些負電荷產生的橫向電場相互抵消;在場板靠近主結的位置,該電場削弱原來的主結電場峰值。但在場板末端,橫向電場于來源于主結的電場相互加強,產生一個額外的電場峰。

場板的作用通常由場氧厚度和場板的長度決定。厚則削弱其降低主結峰場作用;薄則因場板末端新的電場尖峰而發生擊穿。

圖.2給出在相同的反偏電壓下,具有不同場板長度的PN結的表面電場分布,場板越場,峰值越小。實際應用,需要合理設計。

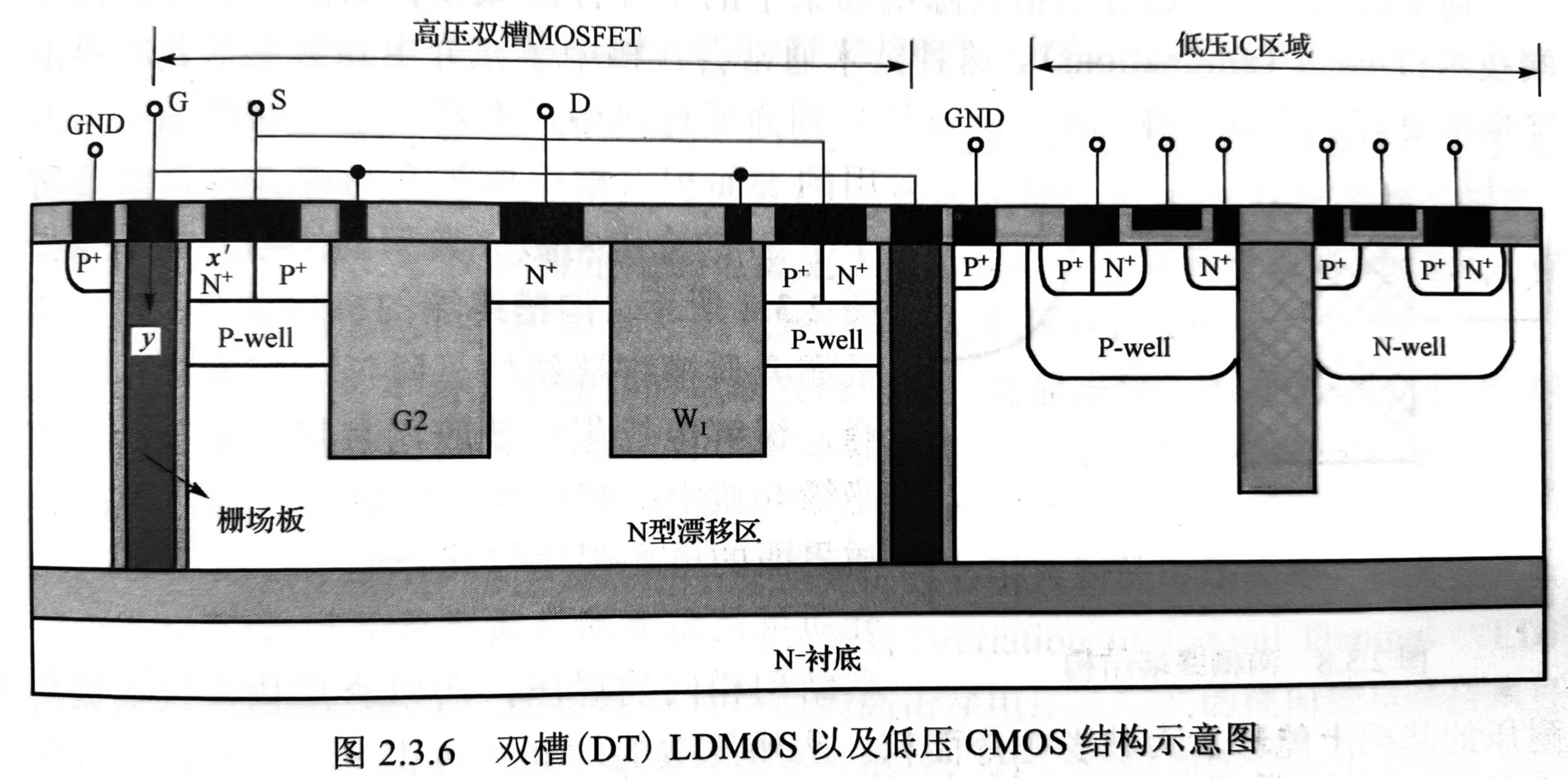

場板下橫向電場分量隨距離按如下指數規律下降:Ex∝exp(-0.6x/tfox),其中tfox是場氧化層厚度,x軸的原點在主結面,其正方向為沿表面遠離主結的方向。如果tfox隨x的增加而增加,場板上的橫向電場分布會更趨于均勻,這種場板稱為斜坡場板,如圖.3所示。

斜坡場板或能花費更小的終端面積獲得緩解表面的尖峰電場。然斜坡場板的工藝實現相對困難,折中方案是圖.4所示的階梯場板。

在常規平面LDMOS中,阻斷狀態下只有處于低電位的柵場板或者源場板才具有對N型漂移區的輔助耗盡作用。

漏場板由于連接最高電位,不具有對N型漂移區的輔助耗盡作用。平面結構中,場板只能產生局部耗盡作用。

若要擴展場板的耗盡區域,只能水平延申場板長度,然而縮短柵場板與漏場板的距離對器件的耐壓有較大影響。

采用縱向場板結構,使場板成為從表面延伸至體內的負電荷中心,在漂移區內產生橫向附加電場,使得部分電力線橫向終止于場板。

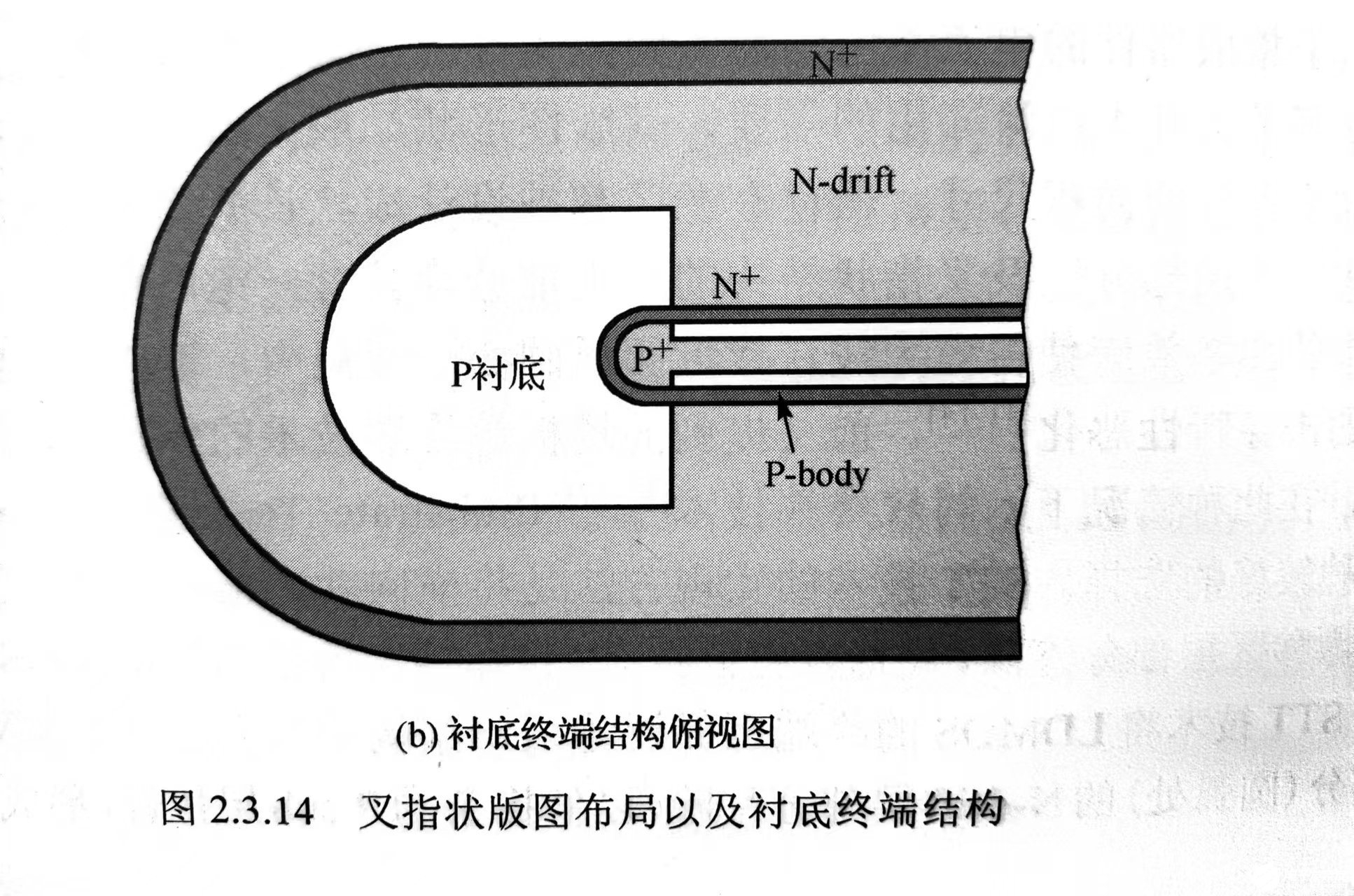

圖.6給出一種帶有雙槽的橫向功率MOSFET器件,其采用了隔離型縱向場板技術。

槽柵從表面延伸至埋氧層,形成縱向的MIS結構,在阻斷狀態下相當于縱向場板,緩解了P-well處的電場集中,且形成多維度輔助耗盡,提高漂移區的優化濃度。通過在漂移區內引入介質槽,等效折疊漂移區,相同尺寸下提高擊穿電壓。

此外,縱向柵場板在阻斷狀態能有效屏蔽來自高壓區的電力線,起到隔離的效果。

.2溝槽終端技術(Trench Terminations)

(上文提及的介質槽)刻槽能去除電場集中的半導體區域以提高耐壓,即溝槽終端技術。這種技術通常會在槽中填充介電系數更低且臨界擊穿電場更高的介質材料。(所填介質的介電常數通常小于Si的介電常數。)

將高電場轉移到介質材料中,有利于縮小結終端結構占用的表面積。

溝槽終端機理:

1.主結緊靠介質槽終端結構,降低了結面處電場尖峰,緩解電場集中效應,將高電場轉移到絕緣介質中。

2.根據高斯定理,垂直于硅介質界面的電場強度與其介電系數成正比,低K介質可使更窄的介質槽承受于較寬Si平面終端結構相同的耐壓,所以介質槽終端在提高耐壓的基礎上能大大節省芯片面積。(性能由槽寬、槽深、及介質k值決定,也就是說耐高壓的配置是槽窄,槽深,高k值)。

.3結終端擴展技術(Junction Termination Extension,JTE)

結終端擴展技術是在主結邊緣的輕摻雜側再摻雜,即引入附加電荷。其機理在于通過優化漂移區的表面電場分布,從而提高器件擊穿電壓。

.4襯底終端技術(Substrate Termination Technology,STT)

集成器件的電流流向均為橫向,器件的電流能力和面積息息相關。

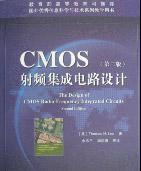

基于橫向功率開關器件大電流應用的需要,版圖一般為跑道形或叉指狀結構;為了縮小器件的面積尺寸,器件有源區都被設計成狹長的細條形結構,因此再跑道結構的彎道部分以及叉指狀結構的指尖部分都具有一定曲率半徑。

圓弧形結構帶來的曲率效應使得電力線在接近圓弧圓心一端集中,造成極大的峰值電場,使得器件的擊穿特性惡化。(前面提到的技術不能有效解決此問題)

STT技術可以,其實現方法是將橫向功率器件的終端區靠近曲率圓心處的漂移區層部分移除,代替以更低摻雜的異質層。

就橫向功率MOSFET器件而言,通過STT技術將LDMOS的終端區靠近跑道結構的彎道部分以及叉指狀結構的指尖部分(圓弧處)的N-drift層部分移除,代替以低摻雜的P-sub層代替,形成了一個由P-sub層和N-drift漂移區組成的耐壓結構。

該變化使得高摻雜的P-body/N-drift結的曲率半徑增加,從而改善器件的擊穿電壓。從工藝角度來看,這種方法不需要增加額外的掩膜版次,也不占用大面積區域。不過引入之后,一定程度犧牲了正向電流能力。

審核編輯:黃飛

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361643 -

MOSFET

+關注

關注

147文章

7156瀏覽量

213149 -

功率器件

+關注

關注

41文章

1758瀏覽量

90416 -

LDMOS

+關注

關注

2文章

77瀏覽量

25261 -

開關器件

+關注

關注

1文章

191瀏覽量

16889

發布評論請先 登錄

相關推薦

功率集成電路設計之結終端技術

功率集成電路設計之結終端技術

評論