引言

GaN作為寬禁帶III-V族化合物半導體最近被深入研究。為了實現GaN基器件的良好性能,GaN的處理技術至關重要。目前英思特已經嘗試了許多GaN蝕刻方法,大部分GaN刻蝕是通過等離子體刻蝕來完成的,等離子體刻蝕的缺點是容易產生離子誘導損傷,難以獲得光滑的刻蝕側壁。為了更好地控制表面粗糙度,英思特采用了一種稱為數字蝕刻的技術來進行研究。

實驗與討論

我們通過選擇PEC二元GaN刻蝕方法來進行實驗。利用二元蝕刻不需要復雜的設備,可實現更好的控制和精度。同時利用二元蝕刻不需要外部刺激以及任何的電極,可以在室溫或更高的溫度下進行實驗。

所有的GaN膜通過LED掩模圖案化,然后使用電子束沉積在GaN膜上沉積200 nm的Ni層,在Ni剝離之后,圖案化的GaN膜留下Ni和GaN膜。

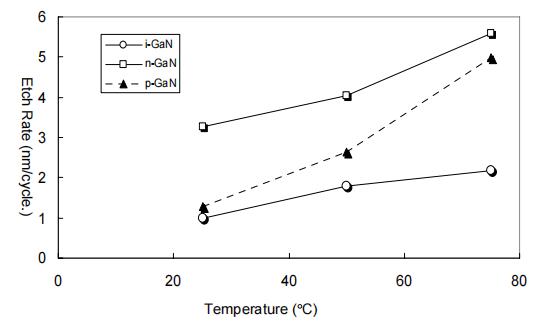

圖1顯示了本征GaN、n-GaN和p- GaN膜的蝕刻速率(單位為nm/周期)與從室溫25℃到75℃的溫度的關系。循環總共需要大約2分鐘(30秒的5% K2S2O8,30秒的KOH和60秒的去離子水)。我們通過數字化的方式完成了實驗,并且沒有使用可以明顯提高化學反應速率的紫外線光源,因此,基本上我們有意降低GaN蝕刻速率,以實現更好的表面粗糙度控制。

圖1:氮化鎵K2S2O8/KOH二元蝕刻速率與溫度的關系

圖1:氮化鎵K2S2O8/KOH二元蝕刻速率與溫度的關系

在75℃下,由于更高的摻雜濃度和更多的缺陷,這使得初始蝕刻更容易開始,因此n-GaN具有最高的蝕刻速。

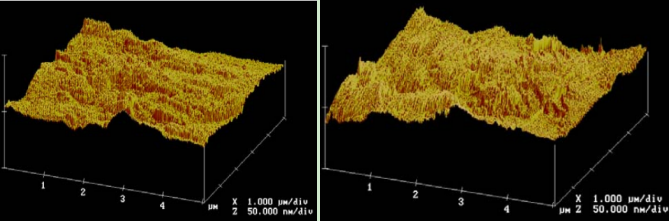

我們還使用AFM進行表面拓撲和粗糙度測量。GaN二元蝕刻前后的GaN表面的AFM圖像如圖2所示。

圖2

圖2

上面的AFM圖像是通過接觸式AFM掃描拍攝的,X和Y方向是掃描區域,Z方向顯示表面粗糙度。AFM圖像顯示在GaN蝕刻之前GaN表面是光滑的,這證明了我們的MOCVD生長技術。

結論

英思特分別在室溫和高溫下,通過藍寶石上的本征GaN、n摻雜GaN和p摻雜GaN膜上成功地進行了K2S2O8/KOH二元蝕刻。我們通過實驗發現蝕刻速率相對較低,但是可以高精度地控制表面粗糙度。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27290瀏覽量

218091 -

晶圓

+關注

關注

52文章

4890瀏覽量

127933 -

氮化鎵

+關注

關注

59文章

1628瀏覽量

116304 -

GaN

+關注

關注

19文章

1933瀏覽量

73287 -

蝕刻工藝

+關注

關注

3文章

51瀏覽量

11736

發布評論請先 登錄

相關推薦

MACOM:硅基氮化鎵器件成本優勢

什么是氮化鎵技術

什么是氮化鎵(GaN)?

為什么氮化鎵(GaN)很重要?

有關氮化鎵半導體的常見錯誤觀念

關于氮化鎵的晶體學濕式化學蝕刻的研究

氮化鎵的大面積光電化學蝕刻的實驗報告

不同氮化鎵蝕刻技術的比較

不同氮化鎵蝕刻技術的比較

評論