在電子系統中,數模轉換器芯片(DAC)的功能是將數字編碼轉換成一系列離散的階梯電壓或者電流,是模擬量輸出和控制的核心器件。雖然基本功能簡單,但市場上的DAC芯片型號繁多,了解其具體參數和內部結構對于DAC芯片的選型、系統的優化是很有必要的。通用型的DAC芯片大多用來輸出直流信號,精度較高(12~16bit),速度較低(<10MHz),一般稱之為精密DAC。下面我們就結合DAC的指標,內部結構和應用需求,一點點揭開精密DAC的真面目。

一、DAC的指標

用戶選擇器件時,可能最關心精度、速度等有限幾個性能。但這些籠統的性能并非簡單的用DAC標稱位數和更新速度就可以表示。我們必須把系統的需求“翻譯”成正確的DAC指標,才能做出合理的選型。

DAC的“精度”,一般指DAC的靜態指標(噪聲歸在動態指標中)。而“速度”則對應DAC的動態指標。下面將分別介紹。

1.1DAC的靜態指標

靜態指標均基于實際DAC與相同位數的理想DAC之間的輸出曲線的比較。

首先我們來看DAC的輸出是不是足夠“直”,也就是線性度如何。DAC的線性度一般受芯片內部的半導體器件匹配度限制,比如電阻串的匹配,極限在10~12位左右,再高的話需要各種校準技術來處理。不同的DAC內部結構也對線性度有限制,R2R結構的DAC線性度極限能比R-string的更好(第二部分會涉及)。

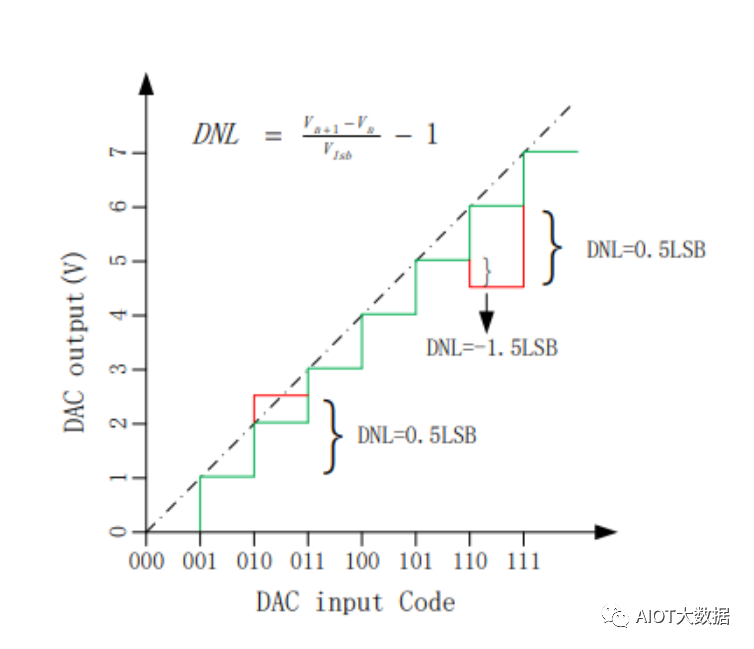

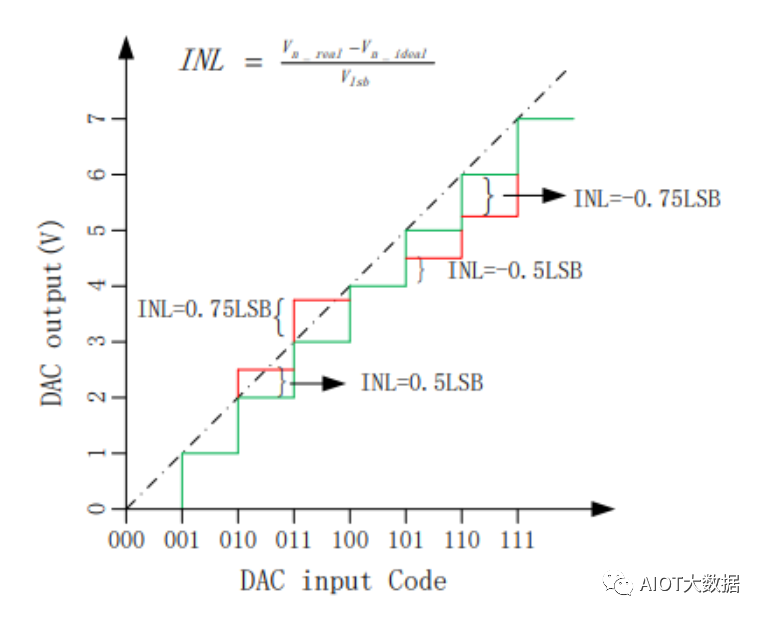

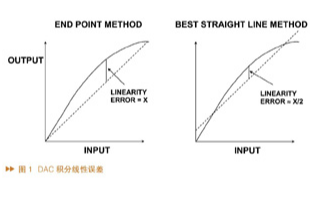

下面這兩張圖,表現出實際的三位DAC與理想的三位DAC輸出波形在線性度方面的差異(紅色為實際輸出曲線):

?? ? ? ?

?? ? ? ?

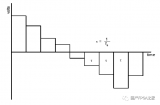

DNL是微分線性度,指相鄰兩個輸出電平的差相對于理想值(1LSB)的偏差。datasheet中的DNL代表所有臺階中最大的偏差值。由上圖可以看到,如果出現DNL<-1LSB的現象,則DAC的輸出肯定是非單調的,也就是說數字編碼增加1,輸出不增加反而會下降。這一點在很多閉環系統應用中是不能接受的,如果DAC出現非單調的情況,則控制環路無法收斂。這時一般會選擇DNL<±1LSB的器件。

INL是積分線性度,指實際的輸出相對理想DAC的輸出之間的差異,所以也叫relativeaccuracy,用滿量程的百分比或者LSB來表示。理論上,某個編碼對應輸出的INL就是從第一個編碼到這個編碼所有的DNL的積分,也印證了“積分”這個名稱的含義。Datasheet中的INL(或者relativeaccuracy)代表所有輸出值最大的INL。這個指標用來衡量DAC輸出的準確度如何,應用比較廣。特別是在開環應用中,應當關注INL的指標。

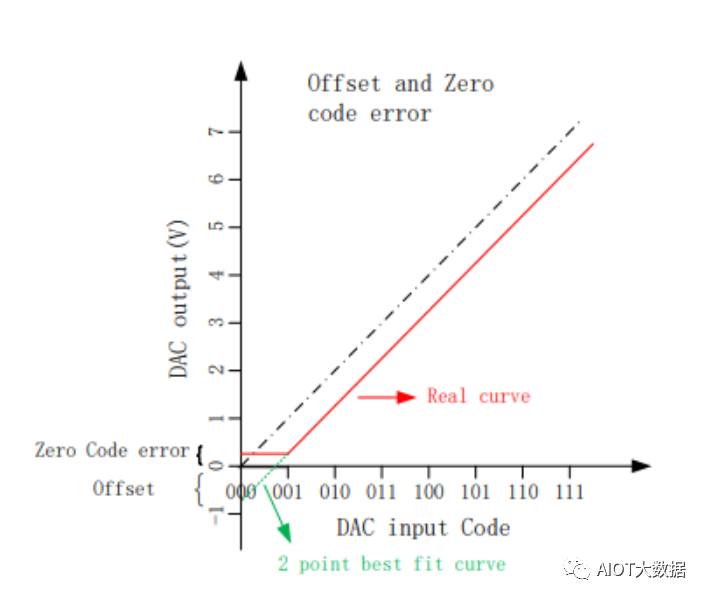

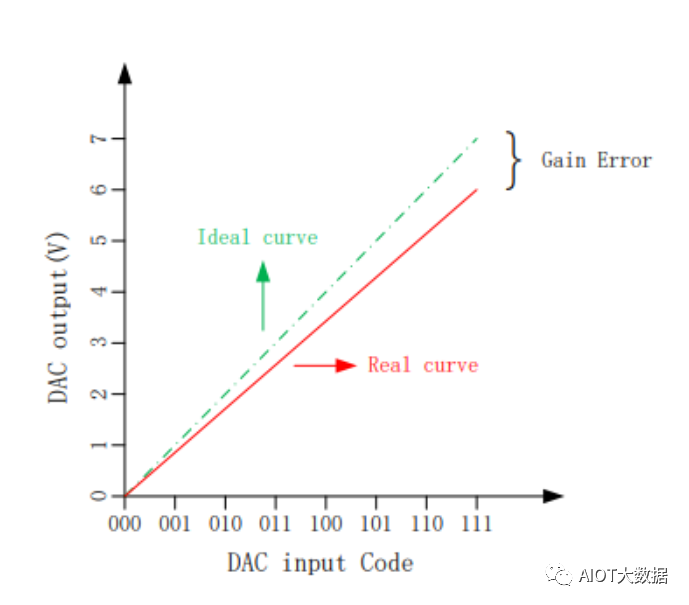

除了上面兩個線性度的參數,DAC的實際輸出曲線還存在其它幾種非理想特性,如下面兩圖所示:

?? ? ? ?

?? ? ? ?

一個無限分辨率的理想DAC輸出特性應該是通過原點的一條直線,y=x(這里我們把DAC增益相對理想值歸一化成1),但實際的DAC輸出特性,用靠近首尾兩端的兩點擬合一條直線,特性一般是y=ax+b。其中,a代表DAC實際的輸出增益,即gain。其相對理想增益的偏差,即gainerror。b代表這條直線整體相對原點向上或者向下偏移的幅度,即offseterror

但實際DAC在code為0附近,輸出電壓也很低時,由于內部電路接近飽和(特別是帶輸出buffer的DAC),會出現一定的非線性。所以DAC會有一個額外的參數來標定code為0時輸出的偏差,叫zerocodeerror.

另外gain,offset在不同溫度下也會產生變化,即gainshift,offseterrorshift。如果客戶對溫度特性很敏感,要特別關注這兩個指標。

特別要提醒的是,由于上面這幾項因素的影響,我們不能直接用DAC輸出曲線來計算DNL或INL,而必須將gainerror,offseterror計算出來并補償掉之后,再去計算DNL和INL。如果客戶要驗證芯片指標,還必須注意數據手冊中每一項指標的測試條件。大部分情況下,INL/DNL基于兩點法擬合直線的基礎上來測量。具體是哪兩點,一般在datasheet中都會注明。

1.2DAC的動態指標

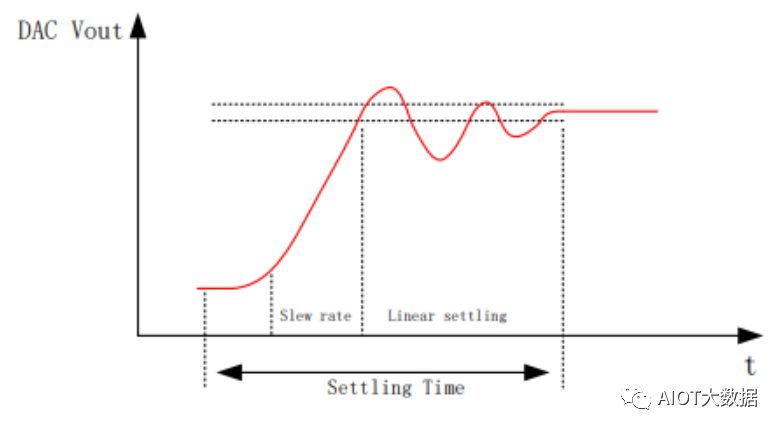

下圖是一個典型的DAC輸出從0附近跳到滿擺幅的輸出波形:

輸出從0到滿擺幅變化(或者特定的兩個差異較大的值)的總時間,稱為settlingtime。輸出主要經歷兩個階段,一是slewrate,二是linearsettling。slewrate反映了輸出大擺幅下的極限驅動能力,一般決定了輸出10%~90%變化的時間,。而linearsettling則主要取決于輸出節點的RC常數或者輸出buffer的帶寬。Settlingtime是用戶考慮精密DAC速度的重點參數。

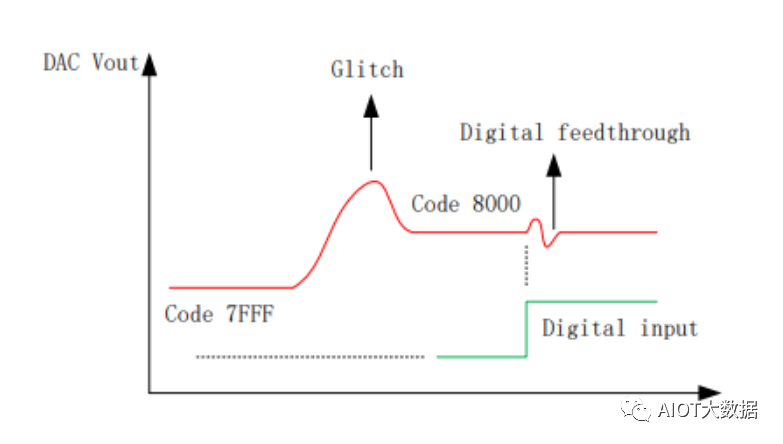

如果用戶對DAC輸出變化要求平穩不能有毛刺的話,則需要關注Glitch和Digitalfeedthrough兩個指標。

Glitch主要與DAC核心部分的開關有關。當內部開關從一個點切換到另一個點時,會受到寄生電荷以及開關切換不能理想同步的影響,從而造成輸出跳動。跳動的幅度和時間都是我們關注的對象,所以Glitch用nV*S這個二者相乘的單位來表示其能量大小。從其產生原理可見,glitch與具體切換的開關位置有關。Code的高位MSB變化時一般會產生較大的glitch,所以datasheet中普遍定義majorcarry處的glitch。Glitch也和結構有關,R-string的glitch一般比R2R結構的glitch小,原因在第二部分有解釋。

Digitalfeedthrough則代表了模擬輸出與數字輸入的隔離程度。即使DAC沒有被選中進行通信,總線上的數字IO信號或時鐘跳動通過內部信號通路或者電源地的耦合也會造成DAC輸出的跳動,即為digitalfeedthrough。良好的設計可以保證這個值很小。

另外,DAC輸出noisedensity也是關注的一部分。DAC的噪聲來源可以分幾部分:VREF(如果有內部基準源的話,flicknoise+熱噪聲),內部電阻串(電阻熱噪聲),輸出buffer(flicknoise+熱噪聲)。用戶需要計算不同帶寬下輸出噪聲帶來的影響。系統設計時需要限制DAC輸出信號的帶寬來抑制不必要的噪聲。一般來說,不希望帶內噪聲限制DAC的輸出精度。

二、DAC的結構

DAC的數據手冊中一般會注明內部是何種結構。下面我們會結合DAC的指標,討論下常見結構DAC的優缺點,可以幫助理解為何不同結構的DAC有不同的指標,在系統上應該注意哪些重點。

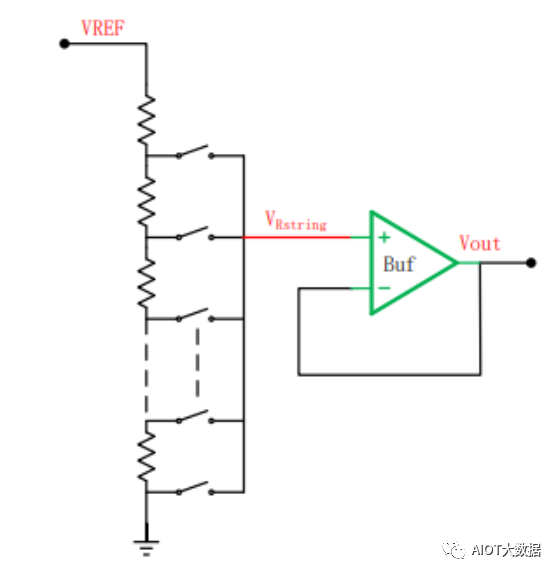

2.1R-string結構

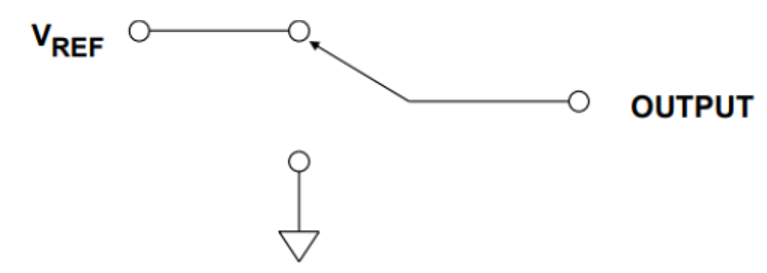

它采用了一串相等的電阻(即R-string的字面含義),從而獲得與參考電壓成比例的值。典型結構如下圖。

這種結構的優點顯而易見:

1.當電阻串輸出點從下邊的開關切換到上邊的開關時,輸出電壓肯定是增加的。所以這種結構天然決定了其良好的單調特性(DNL不會小于-1),這對系統閉環應用是一個很大的好處。

2.一次code變化僅對應兩個開關之間的切換,glitch很小,而且與code無關。所以這是一種低glitch結構。缺點是,消耗了大量的電阻和開關器件,受限于半導體電阻器件的匹配度,很難做到高位數。由此可以延伸出分段等改進的方式來減少電阻數量,但校準代價仍然較大,所以有效精度相對較低。

另外,電阻串總值較大,輸出阻抗高,限制了其工作速度。并且電阻串輸出阻抗隨code在不停變化,需要buffer來提供穩定的輸出能力。所以在應用上需要注意輸出buffer的驅動能力和穩定性,尤其是負載的電容大小。由于上面的特點,這種結構現在被普遍用于12~16位,DNL<+-1LSB(保證單調性)但對INL要求不是非常高(INL大多在12~14位精度)的DAC中。? ?

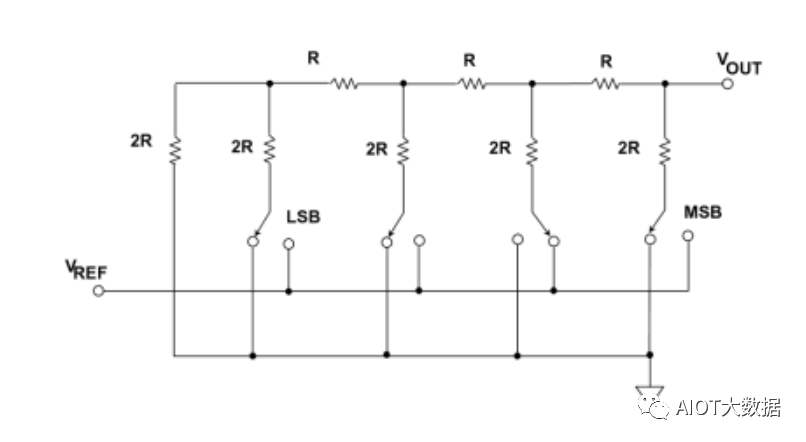

2.2R-2R結構

? ?

? ?

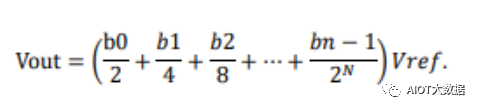

如圖所示,R-2RDAC只使用兩種阻值R和2R的電阻。這種結構的關鍵在于從任何一個2R電阻的右側往左看,等效阻抗都是R。可以看到,

原理上,N位DAC只需要2*N個電阻,因為電阻數量少,生產時可以校準到很高的線性度。

這種結構一般是電壓輸出。而且其輸出阻抗恒定為R,這使得連接到輸出節點的放大器很容易穩定。在使用外部高速buffer時,這種DAC可以達到更高的速度。當然,也有些R-2RDAC自帶輸出buffer,這種情況下,速度主要由內部的buffer來決定。

但另一方面,圖中的開關必須在寬電壓范圍(VREF至地)內工作,這給設計和制造都帶來難題。在不同code切換時,高低位的多個開關會經歷同時導通或者關斷的狀態,加上開關寄生電荷的影響,輸出會出現較大的glitch。

要特別注意的時,基準電壓VREF端的輸入阻抗會隨著代碼而大幅改變。因此使用這種DAC時,基準電壓輸入必須有較強的驅動能力,有時需要增加buffer,如果芯片內部沒有基準電壓buffer的話。

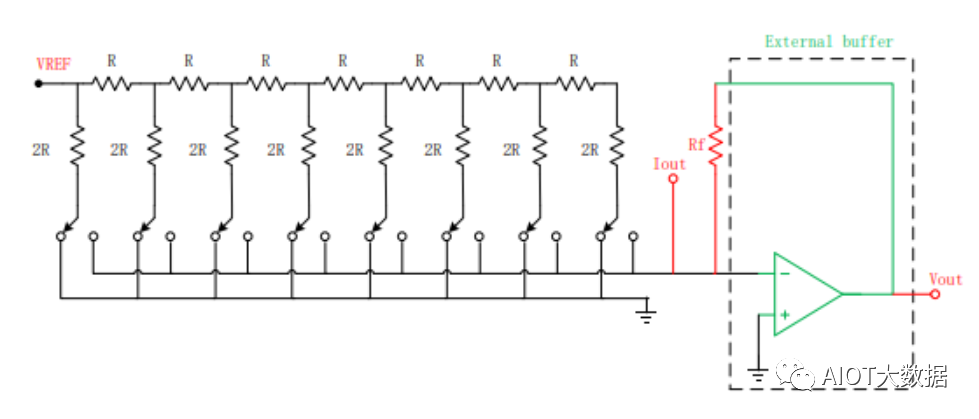

2.3MDAC結構

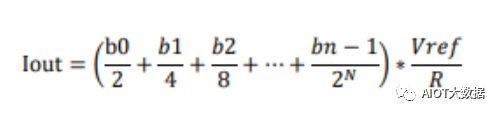

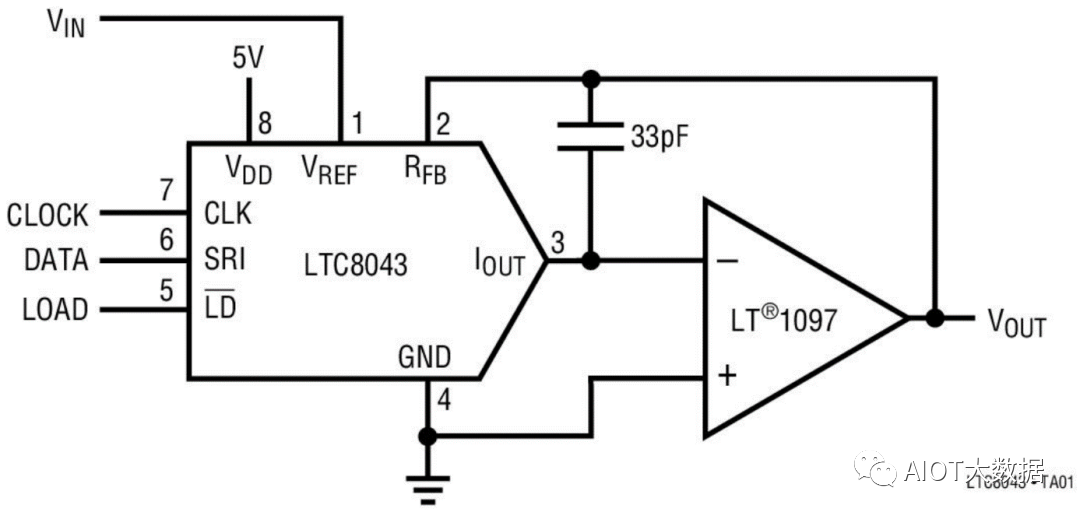

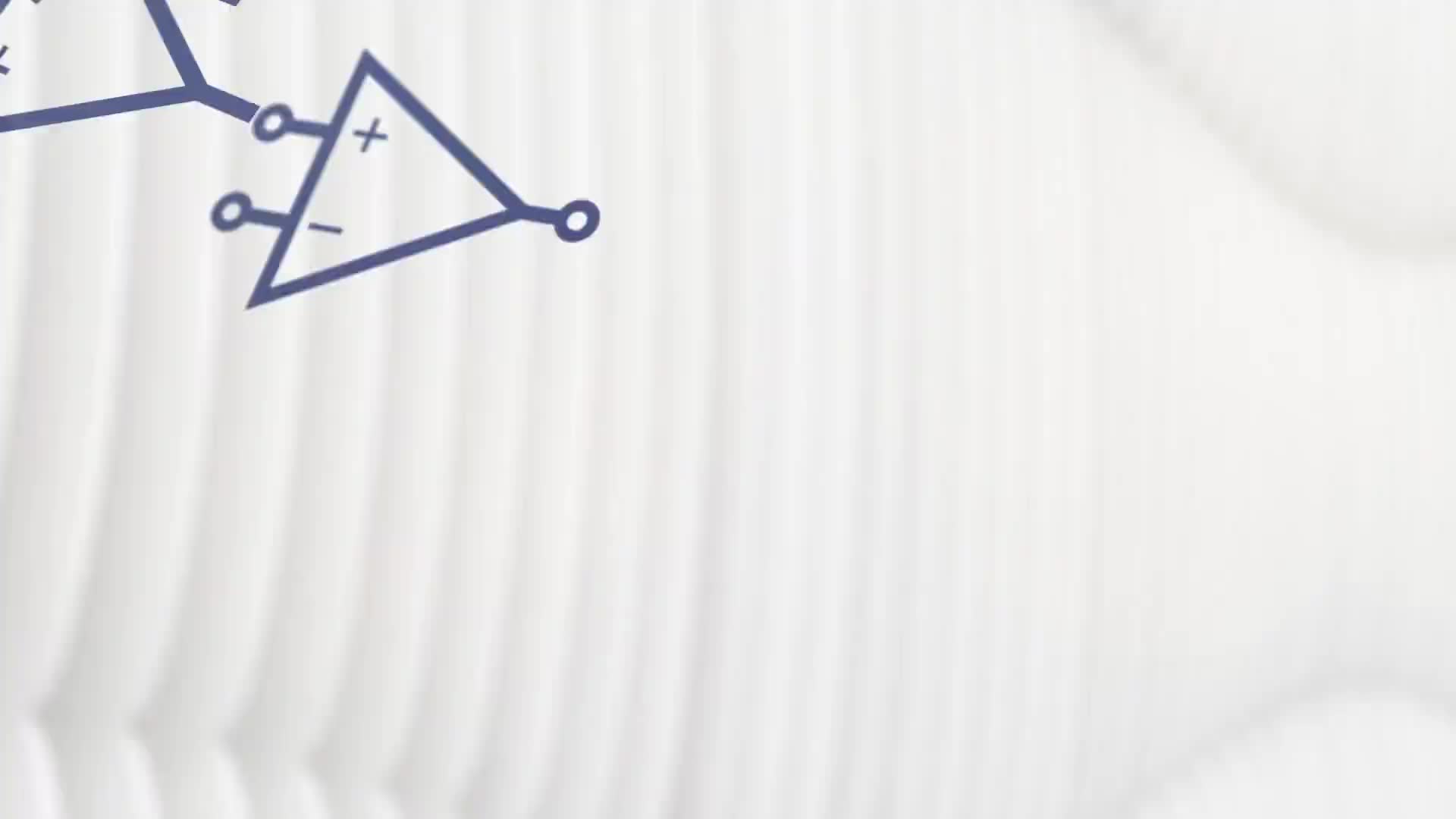

上圖即為MDAC(乘法DAC)。這種DAC其實是一種電流型的R-2RDAC。其與電壓型R-2RDAC的區別在于,VREF連到電阻串的末端,開關則直接連到輸出虛地點。每一級電阻支路均將前級流入的電流減半,所以最終輸出的總電流為

從傳遞特性上看,所有的DAC嚴格意義上說都是乘法DAC,但MDAC這種結構,基準電壓由于不連接內部開關,所以可以在很寬的范圍內變化,甚至是雙極性、交流電壓或者比電源高很多的電壓。所以“乘法”DAC特指有這種特性的DAC。MDAC通過內部反饋電阻和外接運放,可實現與Vref成比例的電壓輸出。由于電阻網絡的開關始終處于虛地低電位,因此對開關的設計要求較低。另外,切換開關時可以通過先導通再關斷的方式,將其引入的glitch降到最低。另外,與R2RDAC相反,MDAC輸出阻抗隨code而變化,這對外部運放的環路穩定性有一定的要求。

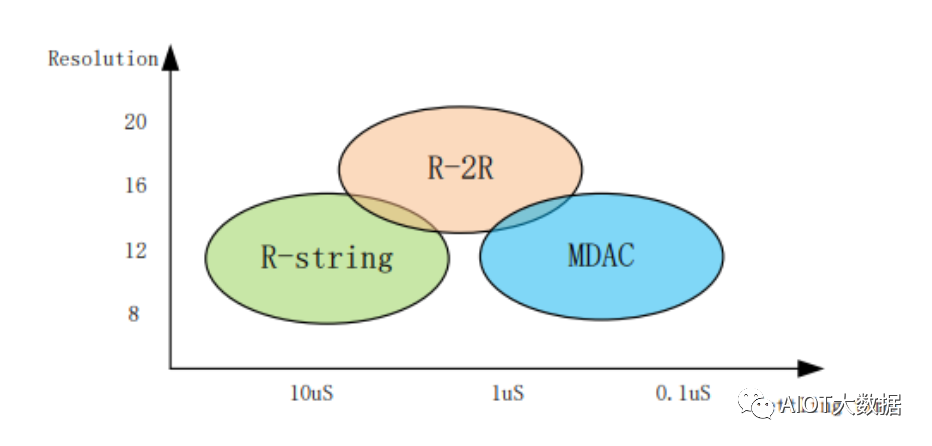

2.4不同結構的DAC比較

三、DAC芯片的原理和分類:

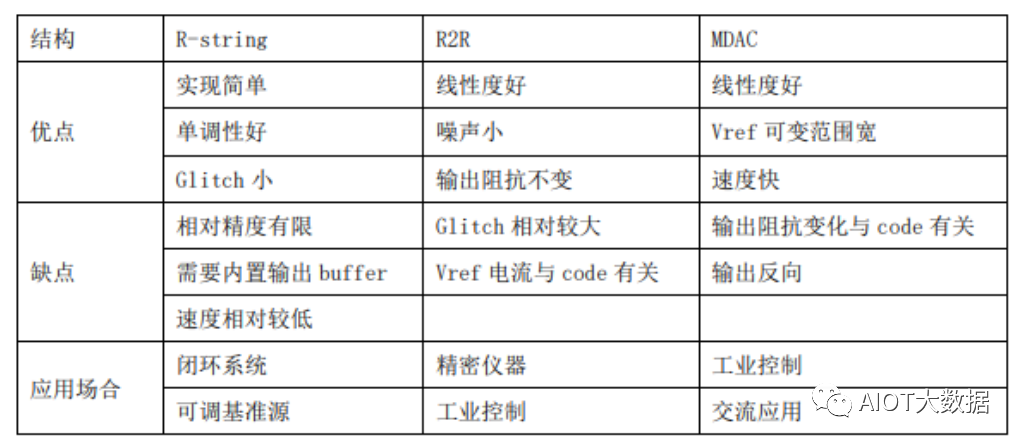

DAC芯片的原理是將數字信號轉換成電壓或電流等模擬信號。數字信號首先經過處理器的處理,然后輸入到DAC芯片的數字輸入端口。DAC芯片內的轉換器將數字信號轉換為模擬信號,然后經過放大器和輸出濾波器進行放大和濾波,最終輸出為模擬信號。

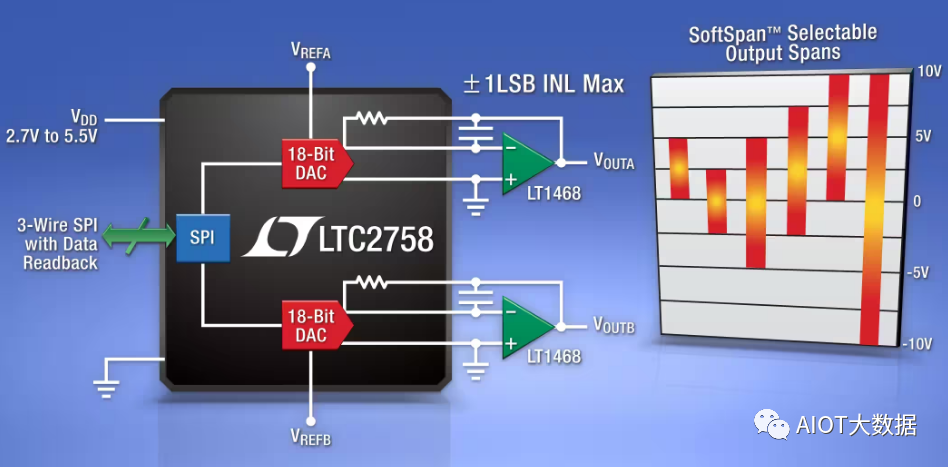

DAC芯片的分類有很多方式根據DAC芯片的輸出類型,DAC芯片可以分為電壓型(VoltageDAC)和電流型(CurrentDAC)兩種類型。

根據數字輸入類型的不同,DAC芯片可以分為并行式和串行式兩種類型。

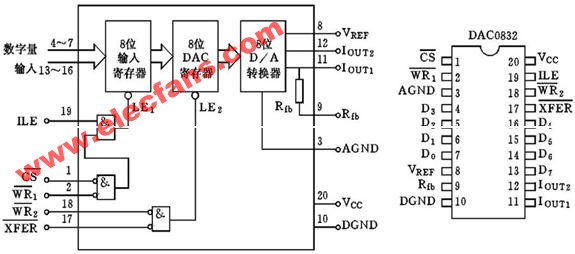

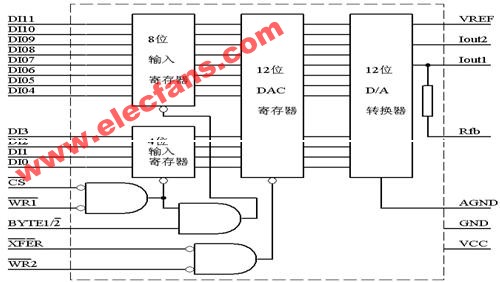

(上面的2張圖片是并行)

(上面的2張圖片是串行)

四、關于DAC的性能有幾個重要的參數:

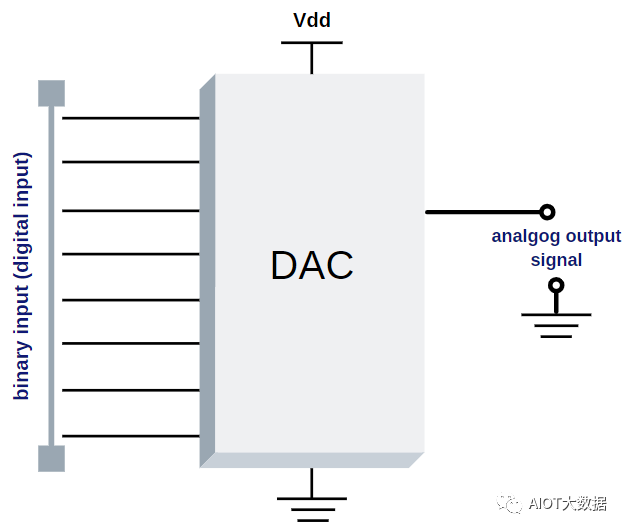

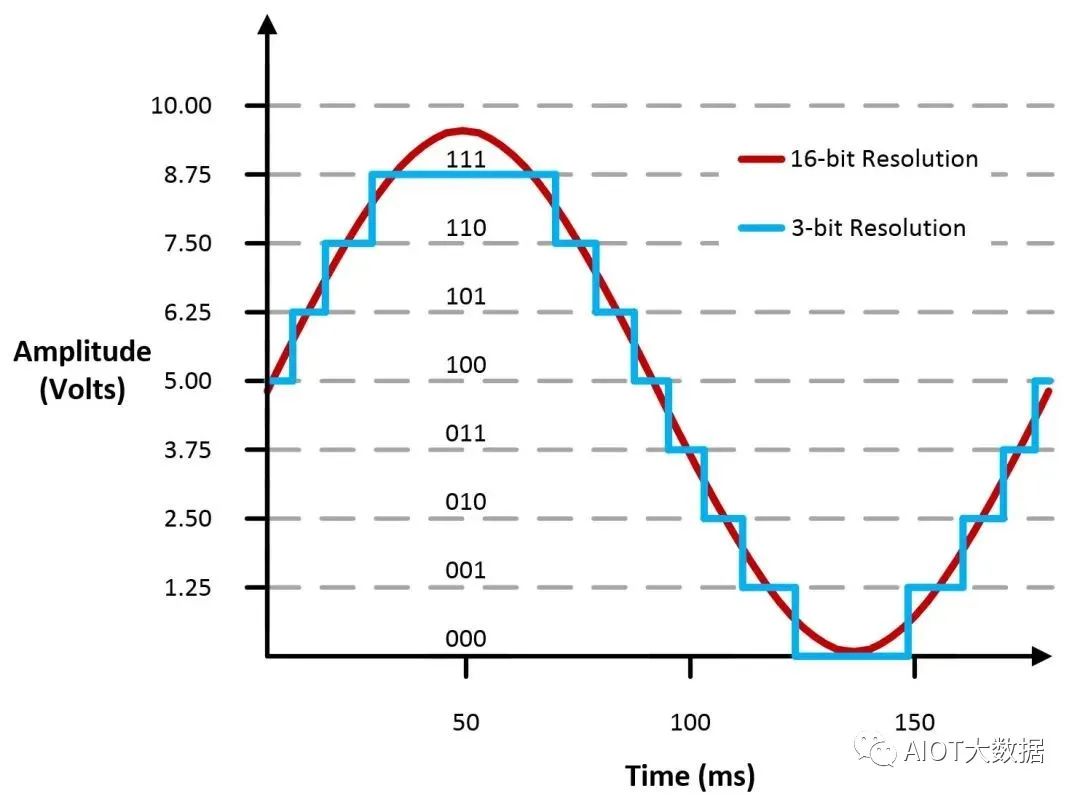

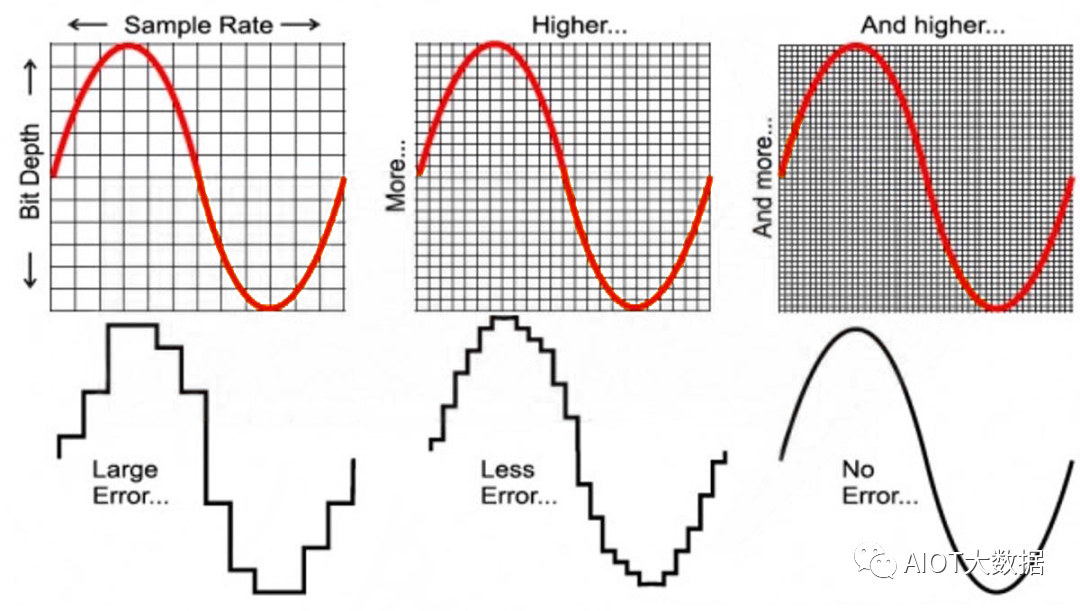

1.分辨率:分辨率是指DAC芯片的數字輸入值和模擬輸出值之間的最小差異。

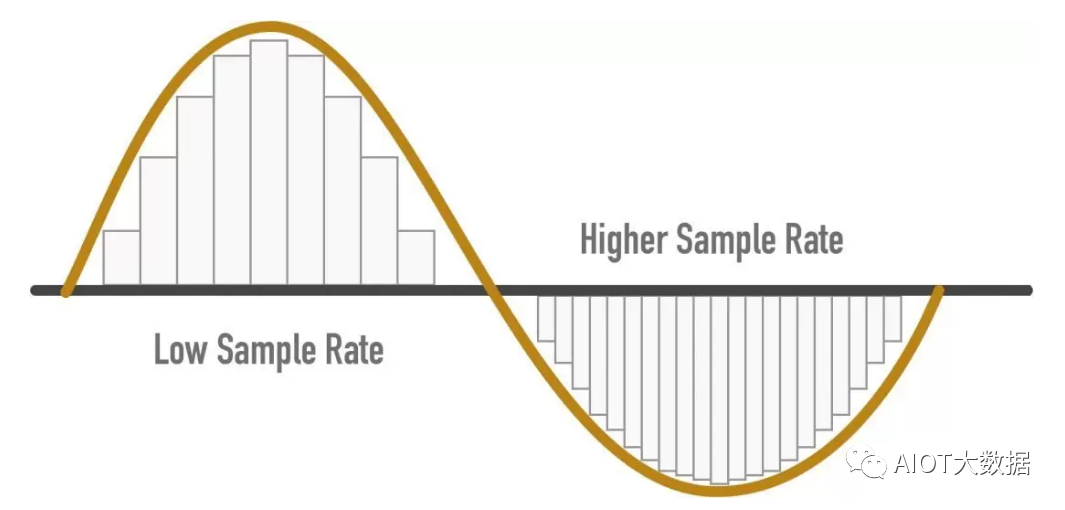

2.采樣速率:采樣速率是指DAC芯片輸入的數字信號的采樣速率,通常以每秒采樣次數(samplespersecond,SPS)來表示。

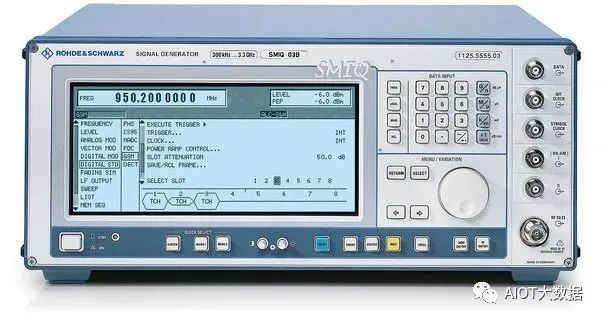

(上方的圖是采樣率)

(上方的圖是采樣率和分辨率)

3.電壓輸出范圍:DAC芯片的電壓輸出范圍通常是固定的,可以是單電源輸出或雙電源輸出。單電源輸出范圍通常是0V到Vref,雙電源輸出范圍通常是±Vref/2或±Vref。

DAC芯片的電壓輸出范圍和分辨率決定了轉換后的模擬信號的精度和范圍,而采樣速率則決定了DAC芯片的輸出速度和驅動能力。開發者在選擇DAC芯片時需要綜合考慮各種參數和特性,并根據自己的應用需求來選擇合適的DAC芯片。

五、PEAKDAC介紹

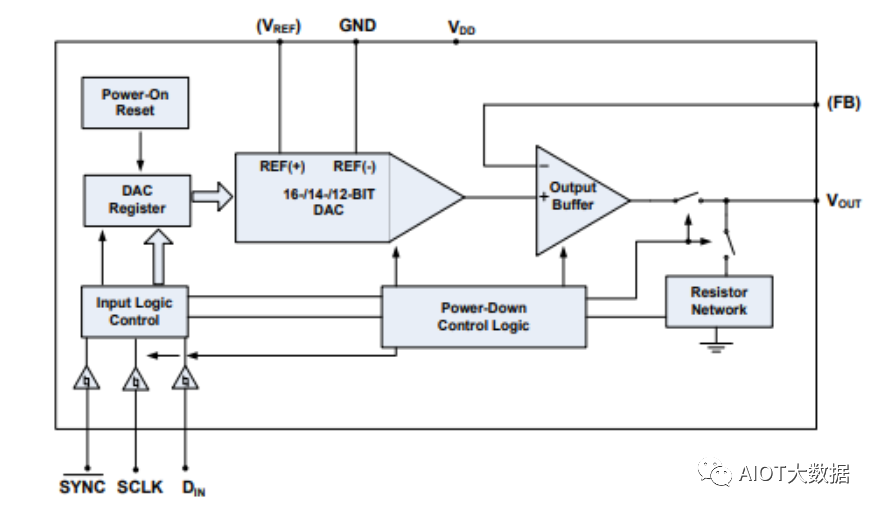

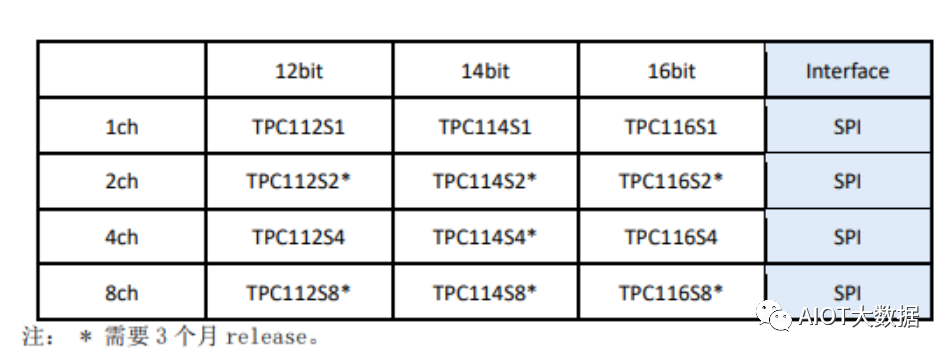

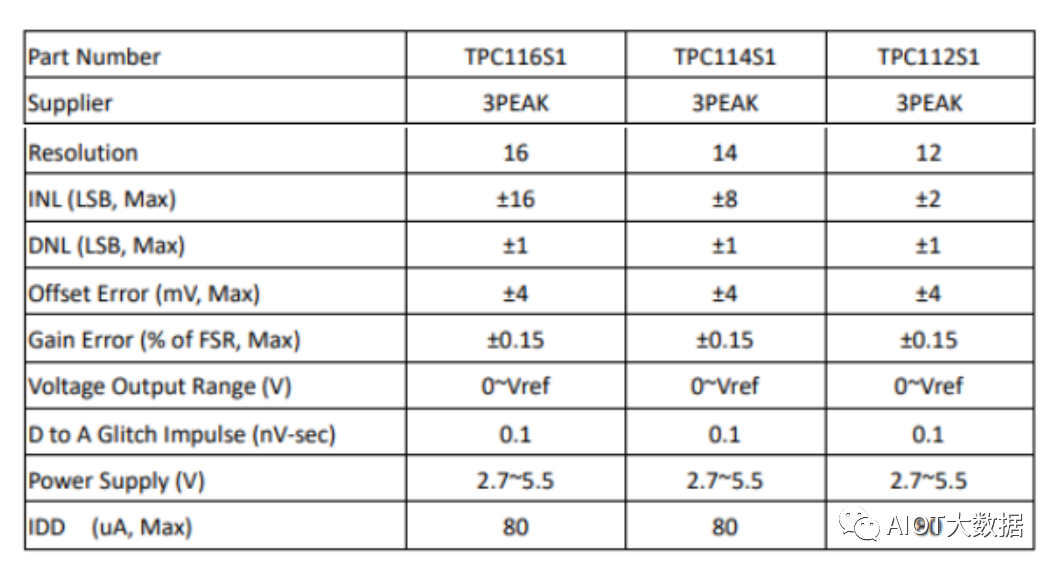

3PEAK推出了12~16bit,1~8通道的一系列精密DAC產品。內部結構則為上面所述R-string結構,內置輸出buffer。具有最高16位的單調性(DNL<+-1LSB),12位的相對精度。采用工業級制造工藝和封裝,工作溫度達-40°~125°。適合在PLC/DCS、伺服控制、模擬量輸出、4~20mA變送等領域使用。3PEAKDAC產品經過在工業級領域的數年量產,性能和可靠性已經得到充分證明,是代替傳統PWM方式或者價格昂貴的DAC產品的高性價比選擇。 ? ?

5.1、3PEAKDAC功能框圖:

5.2、3PEAKDAC產品系列

5.3、3PEAKDAC產品性能列表:

六、DAC應用實例

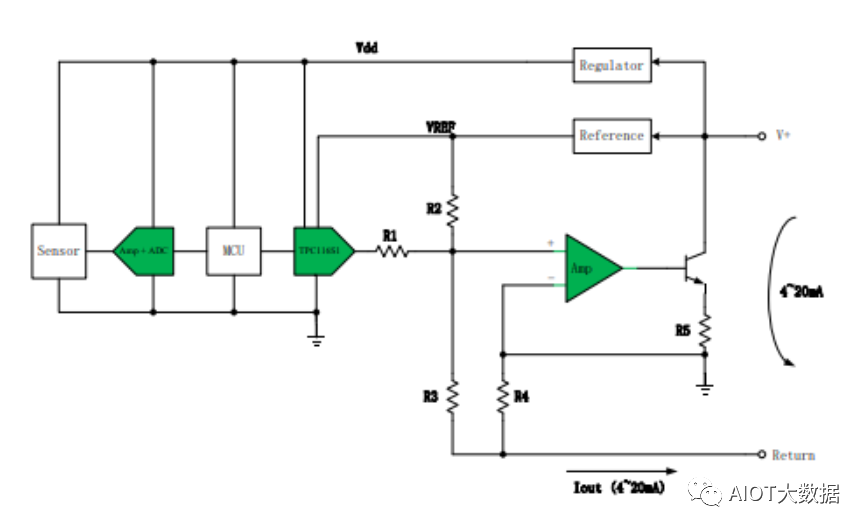

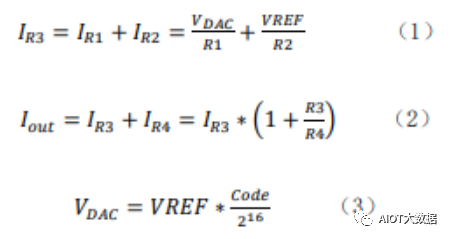

在工業領域,4~20mA是最常見的模擬信號傳輸方式之一,可靠性高,抗干擾能力強,傳輸距離遠。在下面這個傳感器變送器的應用實例中,采用分立的3PEAK的運放和DAC芯片,來放大傳感器信號,并轉化成4~20mA輸出。(綠色為3PEAK可提供的器件種類)

簡單計算可知:

由(1),(2),(3)可得環路輸出電流:

? ?

? ?

如果用傳統低成本的PWM方式得到高分辨率的模擬輸出信號,必然要求MCU的主頻很高,而且長時間的濾波導致系統響應速度慢。由于電源的紋波很大,有時需要采用VREF開關方波來代替電源方波的方式來提升精度,設計更加復雜,外圍器件成本高。使用合適的外置DAC,在成本增加很少的情況下,可獲得性能上的明顯提升,并顯著降低系統設計難度。有些MCU也會內置DAC,但其DAC一般精度有限,且增加了MCU成本。使用外置DAC可以降低對MCU的功能要求,選擇更加靈活,而且可以達到更高的精度,免去在速度和精度上的困難折衷,方便更優化的系統設計。

1.DAC在音頻處理器中可以將數字音頻信號轉換成模擬音頻信號,以便輸出到揚聲器、耳機等音頻設備中。

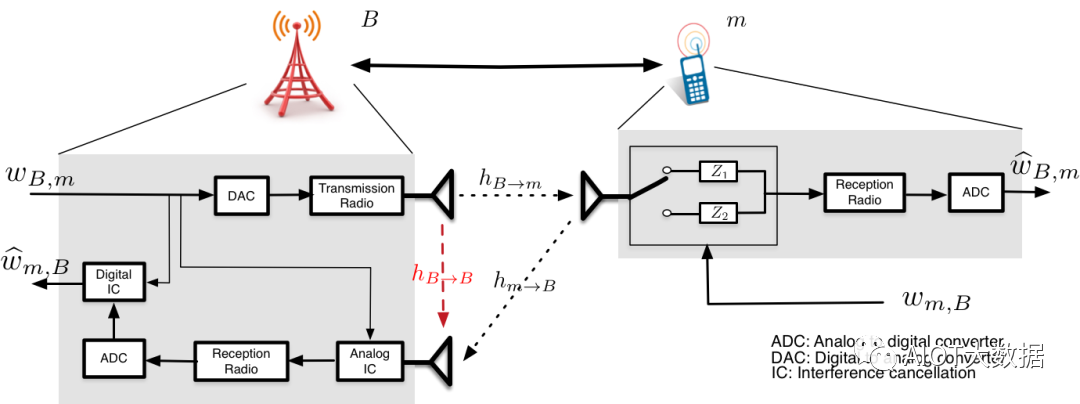

2.DAC在無線電通信中,DAC芯片可以將數字調制的信號轉換成模擬信號,再經放大后發送。

3.測試儀器領域也是DAC的重要應用領域之一,包括信號發生器、數字示波器、頻譜分析儀等。在這些應用中,DAC被用于生成測試信號,可以實現高精度、高穩定性的測試結果。

4.DAC也在醫療設備領域得到了廣泛的應用,主要包括醫療圖像、心電圖、超聲波等方面。高質量的DAC可以實現精確的信號轉換和處理,提供更準確、可靠的診斷結果。

AIOT大數據

-

dac

+關注

關注

44文章

2412瀏覽量

193956 -

模擬信號

+關注

關注

8文章

1161瀏覽量

53543 -

數字信號

+關注

關注

2文章

997瀏覽量

48389 -

數模轉換器

+關注

關注

14文章

1070瀏覽量

84219 -

DAC芯片

+關注

關注

1文章

34瀏覽量

14984

原文標題:技術前沿:卡脖子的DAC芯片詳解

文章出處:【微信號:AIOT大數據,微信公眾號:AIOT大數據】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基本DAC架構:電阻串結構

立體聲DAC芯片與普通DAC芯片的使用區別是什么?

如何通過I/O進行DAC芯片的控制及使用

DAC908芯片資料

高速/高精度視頻DAC芯片 CS7123

DAC的架構、技術指標和應用分析

MCU簡單控制DAC芯片應用(以DAC8550為例)

dac芯片的認知和調試經驗是什么

DAC63204.DAC53204.DAC43204數模轉換器(DAC)數據表

評論