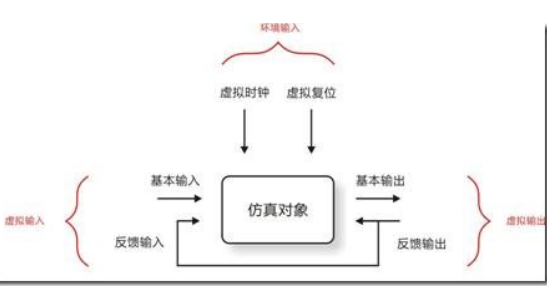

直接在modelsim軟件內執行.do文件進行仿真,不通過vivado調用modelsim,vivado僅用于生成IP核。

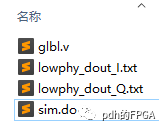

1.需要vivado軟件安裝路徑下的glbl.v文件

路徑舉例:D:XilinxVivado2017.4dataverilogsrcglbl.v

2.需要編寫sim.do文件

(1). sim.do文件包含了testbench.v文件.

(2).其他源代碼.v/.sv文件.

(3).IP simnetlist.v文件,仿真IP核需要.

3.用一個文件夾,將該兩個文件放同一目錄下,如:

4.文件sim.do編寫如下舉例:

vlib work; vlog glbl.v Vlog ../../../duc_in_sel_module_5g/dds.v Vlog ../../../duc_in_sel_module_5g/duc_in_sel_module_5g.v Vlog ../../../duc_in_sel_module_5g/ip/complex_multiplier_sim_netlist.v Vlog ../../../duc_in_sel_module_5g/ip/IF_DDS_sim_netlist.v vlog -sv ../cpri_ctrl_nr/cpri_ctrl_nr_decomp_regroup.sv vlog -sv ../cpri_ctrl_nr/cpri_ctrl_nr_tx_data_regroup.sv vlog -sv ../cpri_ctrl_nr/cpri_ctrl_nr_tx_data_sel.sv vlog -sv ../testbench/tb_xxxx.sv vsim -t ps -novopt work.tb_xxxx glbl -L secureip -L simprims_ver -L unifast_ver -L unimacro_ver -L unisims_ver -L xpm log -r /*

以上編寫完成

其中 ../ 為sim.do文件當前目錄的上一級文件夾,../../ 則為上兩級文件夾

IF_DDS_sim_netlist.v 就是vivado IP核生成以后,出來的仿真用.v文件

vlib work; 在sim.do文件夾目錄下在創建一個work文件夾

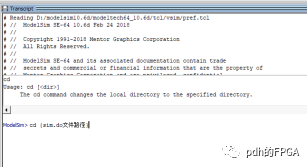

5.打開modelsim窗口

在gui界面輸入

cd {sim.do文件路徑}

{}中的內容就是sim.do文件的路徑,絕對路徑。

例如

cd {E:cpri_ctrl_topsim}

輸入完成以后,直接輸入 do sim.do 指令

即可

審核編輯:劉清

-

Xilinx

+關注

關注

71文章

2167瀏覽量

121301 -

Vivado

+關注

關注

19文章

812瀏覽量

66470 -

MODELSIM仿真

+關注

關注

0文章

15瀏覽量

7283

原文標題:單獨使用modelsim仿真xilinx

文章出處:【微信號:pdh的FPGA,微信公眾號:pdh的FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何在ModelSim中添加Xilinx仿真庫

安富利GSM給您說說ModelSim仿真XILINX庫添加

Xilinx ISE 12.2 調用Modelsim進行行為仿真詳解

減少Xilinx Ise與Modelsim聯合仿真的錯誤方法

Xilinx ISE是如何調用ModelSim進行仿真的

仿真軟件ModelSim及其應用,ModelSim的仿真流程

Modelsim仿真教程Modelsim的基礎入門基礎教程免費下載

怎樣單獨使用modelsim仿真xilinx呢?

怎樣單獨使用modelsim仿真xilinx呢?

評論