本文來自“集成芯片與芯粒技術白皮書”,本文重點介紹了發展集成芯片和芯粒的重要意義。

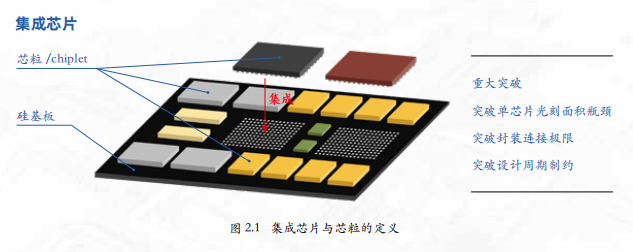

集成芯片是指先將晶體管集成制造為特定功能的芯粒(Chiplet),再按照應用需求將芯粒通過半導體技術集成制造為芯片。其中,芯粒(Chiplet)是指預先制造好、具有特定功能、可組合集成的晶片(Die),也有稱為“小芯片”,其功能可包括通用處理器、存儲器、圖形處理器、加密引擎、網絡接口等。硅基板(Silicon Interposer),是指在集成芯片中位于芯粒和封裝基板(Substrate)之間連接多個芯粒且基于硅工藝制造的載體,也有稱為“硅轉接板”、“中介層”。硅基板通常包含多層、高密度互連線網絡、硅通孔 (Through Silicon Via, TSV) 和微凸點 (Micro Bump),保證了電源、數據信號在芯粒之間和封裝內外的傳輸,而且可以集成電容、電感等無源元件和晶體管等有源電路。

集成芯片的概念源于 2010 年臺積電的蔣尚義博士提出的“先進封裝”概念,他提出可以通過半導體互連技術連接兩顆芯片,從而解決單芯片制造的面積上限,解決板級連接的帶寬極限問題。而后,時任美國美滿電子公司總裁的周秀文博士(Sehat Sutrardja)將“模塊化”設計思想與方法進一步融入。

經過多年學術界和企業的發展,“先進封裝”已無法涵蓋多芯粒集成后所形成的新系統的科學與技術,于是在 2022 年自然科學基金委召開的雙清論壇上,孫凝暉院士、劉明院士以及蔣尚義先生等我國學者在凝練相關基礎技術后提出“集成芯片(Integrated Chips)”這一概念替代“先進封裝”、“芯粒”等稱謂,用于表達其在體系結構、設計方法學、數理基礎理論、工程材料制造等領域中更豐富的含義。

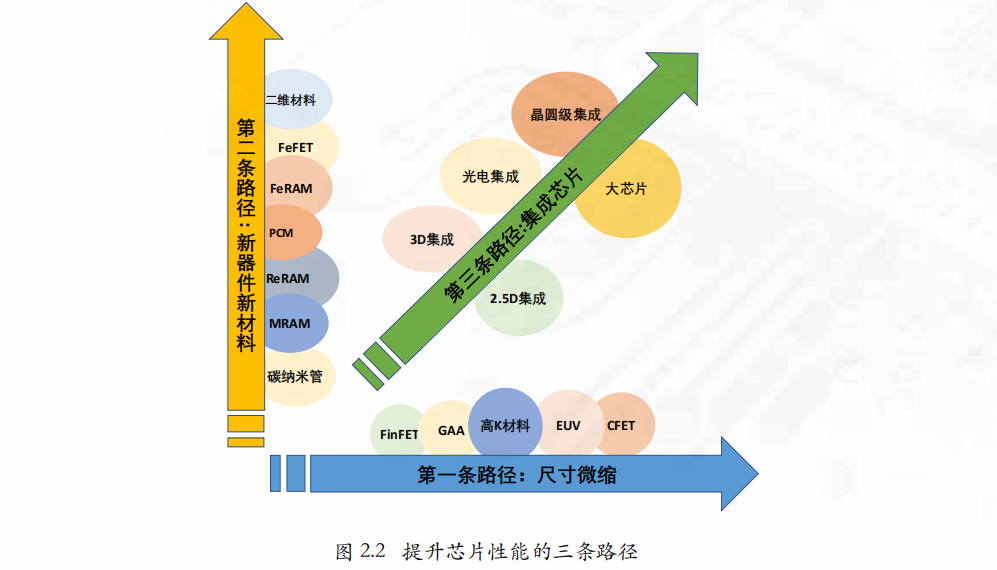

從技術上看,目前主要有三條提升芯片性能的發展路徑,如圖 2.2 所示,三條技術路徑從不同維度共同推動集成電路的發展。

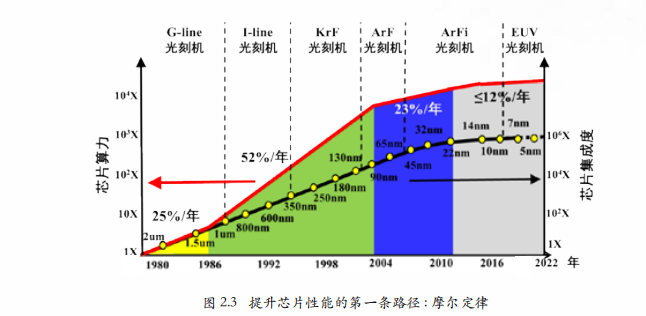

第一條路徑是通過將晶體管的尺寸不斷微縮實現集成密度和性能的指數式提升,也被稱為遵循“摩爾定律”的發展路徑。1965 年戈登·摩爾指出,集成電路的晶體管數目大約每 18-24 個月增加一倍。摩爾定律、登納德縮放定律、以及同時期的體系架構創新,包括指令級并行、多核架構等,共同推動了芯片性能隨工藝尺寸微縮的指數式提升。

隨著集成電路工藝進入 5nm 以下,尺寸微縮接近物理極限,單純依靠縮小晶體管尺寸提高芯片性能的空間變小,同時帶來了成本與復雜度的快速提高。芯片散熱能力、傳輸帶寬、制造良率等多種因素共同影響,形成了芯片功耗墻、存儲墻、面積墻等瓶頸,限制了單顆芯片的性能提升。可以說,摩爾定律的放緩已成為國際和我國集成電路發展的重大挑戰。

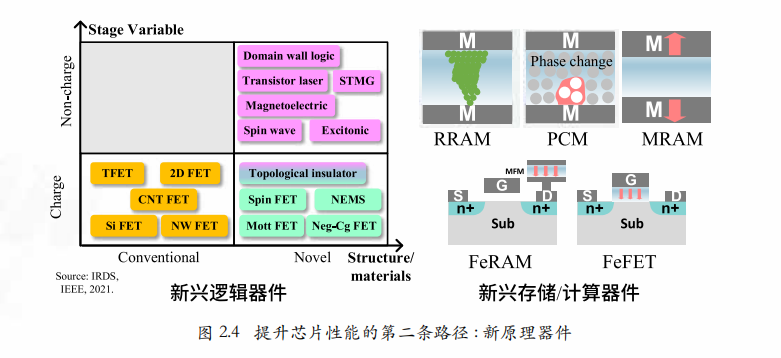

第二條路徑是通過發展新原理器件,研發新材料,實現單個晶體管器件的性能提升。隨著鐵電存儲器 FeRAM、阻變存儲器 RRAM、磁存儲器 MRAM、相變存儲器 PCM、鐵電晶體管 FeFET 等多種新原理器件的發展,結合寬禁帶半導體、二維材料、碳納米管等新材料的研究,探索超越傳統CMOS 器件性能 / 能效的新型器件和突破馮諾依曼架構的新型計算范式成為一個重要的研究領域。然而,新原理器件是面向未來的芯片性能提升發展路徑,從科學研究到實際應用的周期通常較長,難以在短時間內解決當前高性能集成電路芯片受限的挑戰。

隨著技術體系和產業生態逐漸構建,集成芯片將發展為芯片性能提升的第三條主路徑。芯片的性能主要取決于芯片集成的晶體管規模,而晶體管規模又取決于芯片制造面積。集成芯片路徑能夠有效突破芯片制造的面積墻瓶頸。芯片的“面積墻”,是指單顆芯片的制造面積受限于***可處理的極限尺寸和良率。一方面,最先進的高性能芯片(如 NVIDIA H100 GPU 等)面積正在接近光刻面積極限。同時,單芯片良率隨面積增長快速下降,在高成本的先進工藝下,該問題更加具有挑戰性。集成芯片能夠通過多顆芯粒與基板的 2.5D/3D 集成,突破單芯片光刻面積的限制和成品率隨面積下降的問題,成為進一步提升芯片性能的可行路徑。另外一方面,集成芯片技術是一條不單純依賴尺寸微縮路線提升芯片性能的重要途徑,在短期內難以突破自主 EUV ***和先進節點制造工藝的情況下,可以提供一條利用自主低世代集成電路工藝實現跨越 1-2 個工藝節點的高端芯片性能的技術路線。

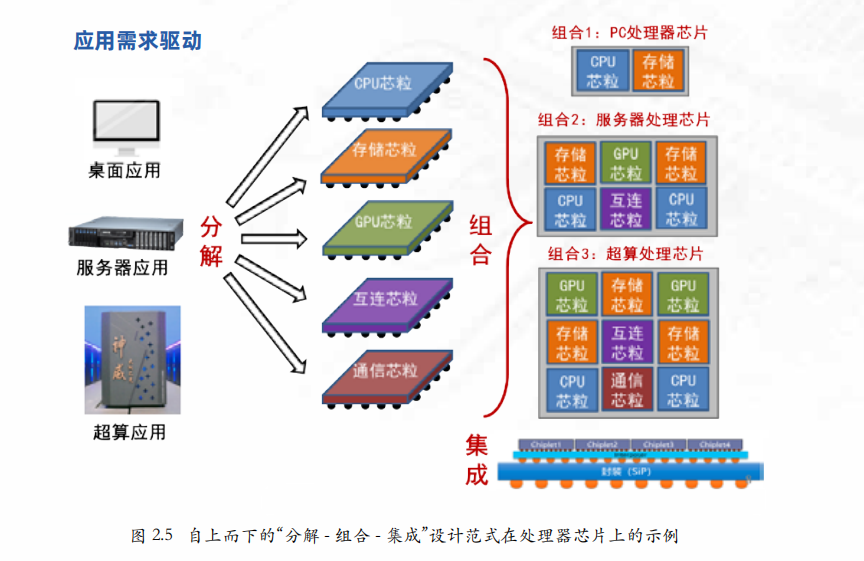

集成芯片采用系統工程學的原理,發展自上而下構造法的集成電路設計新范式。自上而下意味著芯片結構適配應用特征,自上而下采用“分解 - 組合 - 集成”的方法。根據應用特征,抽象分解成若干標準的芯粒預制件,將眾多芯粒預制件,按照結構組合成不同應用領域的芯片,將芯片制造分解為芯粒預制件的制造和多芯粒集成。下例展示了處理器芯片采用集成芯片范式后的新流程:

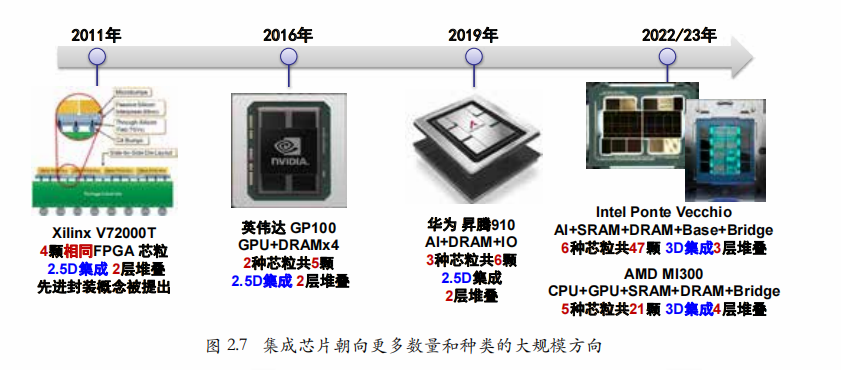

最早的集成芯片原型是由臺積電與美國賽靈思(Xilinx)公司共同完成的一款大容量 FPGA 芯片V7200T,它將四個大規模的 FPGA 芯粒在一塊硅基板(Interposer)上連接在一起,形成一個超過2000 個可編程邏輯門的系統。借助這一芯片的開發,臺積電也完成了基于半導體工藝的芯片互連封裝技術,稱為 Chip-on-Wafer-on-Substrate(CoWoS)。目前這一技術作為 2.5D 集成芯片的代表性工藝,廣泛的應用于高性能處理器芯片產品中。第一個采用 CoWoS 技術的處理器集成芯片是英偉達公司的 GP100 GPU 芯片,它的結構是通過 CoWoS 工藝將 GPU 芯粒和多個 HBM 芯粒在一個封裝體內集成,最大化處理器與存儲之間的通信帶寬,硅基板尺寸超過 1 個光罩(858mm2)。我國華為海思公司設計的昇騰 910 芯片,也是基于這一技術將 3 種、6 個芯粒的集成,實現了高算力的人工智能處理器。

近年來,隨著 TSV、銅 - 銅混合鍵合等工藝的成熟,3D 集成芯片成為了高性能處理器領域新的發展趨勢。美國 AMD 和 Intel 公司均基于 3D 集成芯片技術,設計了面向超算的高性能超算處理器芯片。上述產品將將 6-8 種,超過 20 個芯粒的芯粒集成在一個系統中,最終實現了更大規模(千億以上規模數量級晶體管)、更復雜的集成。在 2.5D 集成上,基于重分布層(Re-Distribution Layer)的扇出工藝(FanOut)可以實現更大規模的芯粒集成,美國 Tesla 公司基于 FanOut 工藝開發面向人工智能的訓練處理器集成芯片 DOJO,RDL 基板的總面積達到 20000mm2,包含 25 個 D1 多核處理器芯粒和光電融合的通信芯粒。

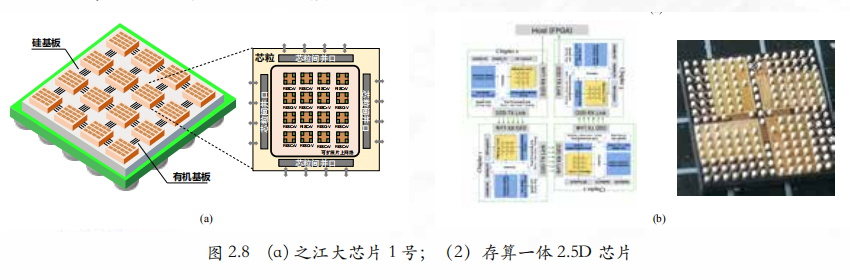

我國研發機構在高集成度上取得了進展。比較有代表性的包含,2022 年中科院計算所智能計算機中心和之江實驗室聯合開發了“之江大芯片一號”,該芯片成果集成了 16 個芯粒,每個芯粒含 16個 CPU 核,無論是集成的芯粒數和體系結構上的計算核心數,都實現了突破,從體系架構和設計方法學上,驗證了利用集成芯片突破單處理器芯片的算力極限技術途徑。目前,正在開展“之江大芯片二號”的工作,集成度和性能將進一步提升。

2022 年,復旦大學集成芯片與系統全國重點實驗室基于集成扇出封裝工藝實現了存算一體 2.5D 芯片,采用片間按層流水的可擴展架構實現了系統算力與存儲規模的按芯粒比例的線性增長,避免了“一系統一設計”的高復雜度問題。此外,阿里達摩院聯合紫光國芯研發基于 3D 混合鍵合工藝的智能加速器 -DRAM 堆疊集成芯片,豪威科技的采用三層堆疊工藝將圖像傳感器芯粒、模擬讀出電路芯粒、圖像信號處理與 AI 芯粒集成為一個組件,面向像素的不斷提升,最小化芯粒間的通信開銷。

集成芯片中,由于每個芯粒由不同的單位設計,因此接口的標準化是系統能夠高效率組合的關鍵因素。在 Intel 的主導下,2022 年 3 月,通用高速接口聯盟(UCIe)正式成立,旨在構建芯粒技術在芯片上的互聯標準。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27286瀏覽量

218074 -

存儲器

+關注

關注

38文章

7484瀏覽量

163762 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

集成芯片

+關注

關注

0文章

249瀏覽量

19695

原文標題:集成芯片與芯粒(Chiplet)技術白皮書

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EDA技術從何而來?EDA技術發展歷程

封裝天線技術發展歷程回顧分析

新興的半導體技術發展趨勢

什么是集成無源元件?對PCB技術發展產生了什么影響?

集成電源是電源技術發展的必由之路

集成無源元件對PCB技術發展有什么樣的影響

集成芯片的概念和技術發展路徑

集成芯片的概念和技術發展路徑

評論