power state由于aarch64架構有多種不用的電源狀態,不同電源狀態的功耗和喚醒延遲不同。

如standby狀態會關閉power domain的clock,但并不關閉電源。因此它雖然消除了門電路翻轉引起的動態功耗,但依然存在漏電流等引起的靜態功耗。故其功耗相對較大,但相應地喚醒延遲就比較低。

而對于power down狀態,會斷開對應power domain的電源,因此其不僅消除了動態功耗,還消除了靜態功耗,相應地其喚醒延遲就比較高了。

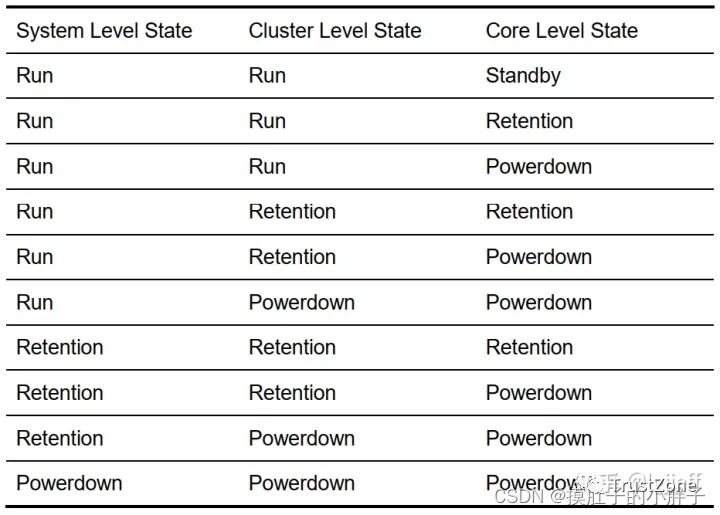

psci一共為power domain定義了四種power state:

(1)run:電源和時鐘都打開,該domain正常工作

(2)standby:關閉時鐘,但電源處于打開狀態。其寄存器狀態得到保存,打開時鐘后就可繼續運行。功耗相對較大,但喚醒延遲較低。arm執行wfi或wfe指令會進入該狀態。

(3)retention:它將core的狀態,包括調試設置都保存在低功耗結構中,并使其部分關閉。其狀態在從低功耗變為運行時能自動恢復。從操作系統角度看,除了進入方法、延遲等有區別外,其它都與standby相同。它的功耗和喚醒延遲都介于standby和power down之間。

(4)power down:關閉時鐘和電源。power domain掉電后,所有狀態都丟失,上電以后軟件必須重新恢復其狀態。它的功耗最低,但喚醒延遲也相應地最高。

(這里我很好奇怎么和linux的s3、s4對應的。當時測試s3的時候,對應的是suspend。這里的對于cpu的有off、on、suspend三種,我覺得這里應該就是對于的standby,因為有wfi或wfe這些指令。那s4就是CPU off了?可以看一下這個有點認識,突然想到psci里面的狀態是對于的cpu為對象,但是linux的電源管理應該是對整個設備。)

顯然,power state的睡眠程度從run到power down逐步加深。而高層級power domain的power

state不應低于低層級power domain。

如以上例子中core 0 – core 2都為power down狀態,而core 3為standby狀態,則cluster 0不能為retention或power down狀態。同樣若cluster 0為standby狀態,而cluster 1為run狀態,則整個系統必須為run狀態。

為了達到上述約束,不同power domain之間的power state具有以下關系:

這里解釋了psci那個源碼文檔里電源樹的概念。

psci實現了父leve與子level之間的電源關系協調,如cluster 0中最后一個core被設置為power

down狀態后,psci就會將該cluster也設置為power donw狀態。若其某一個core被設置為run狀態,則psci會先將其對應cluster的狀態設置為run,然后再設置對應core的電源狀態,這也是psci名字的由來(power state coordinate interface)

-

電源

+關注

關注

185文章

18384瀏覽量

256526 -

cpu

+關注

關注

68文章

11087瀏覽量

217288 -

Linux

+關注

關注

87文章

11518瀏覽量

213993 -

SMP

+關注

關注

0文章

78瀏覽量

20295

發布評論請先 登錄

評論