我們設計放大電路的初衷是放大前端微弱信號輸出,抑制前端干擾信號輸入;

關于普通運算放大器構成的差分放大固然可以抑制共模輸入,放大差分輸入,但是我們還有個器件能夠更好的抑制共模信號,放大差模信號;

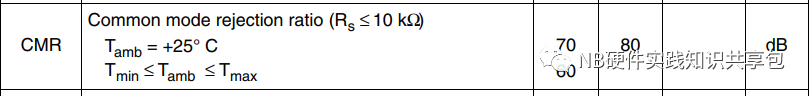

這個器件就是儀表放大器,我們可以從手冊中看出,關于共模抑制比CMRR參數比較,CMRR就是差模增益/共模增益,所以差模增益越大,共模增益越小,CMRR就越大;

這個是普通運放LM324的CMRR,最大80dB;

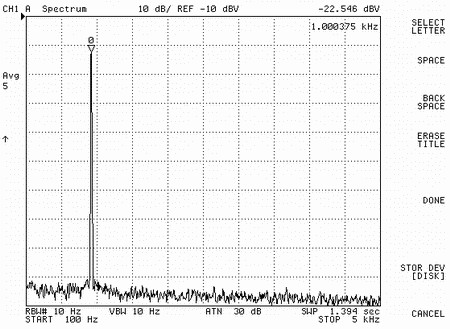

我們再看下儀表放大器的CMRR,在增益為1時,CMRR最小為80dB,增益越大,CMRR越高,抗干擾能力越強,這正是我們所需要的;

但是我們再看,價格極貴,這只是部分的;

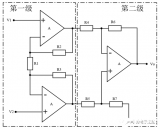

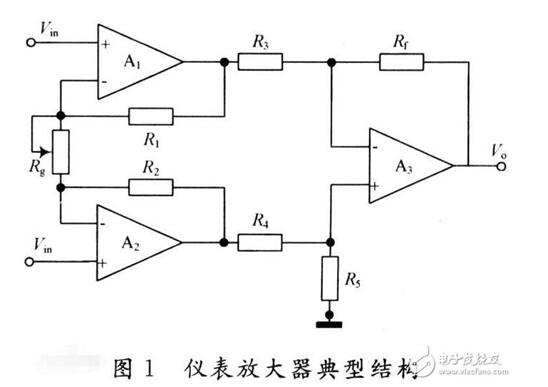

那么我們看下儀表放大器內部圖:

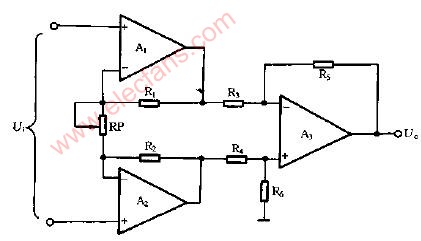

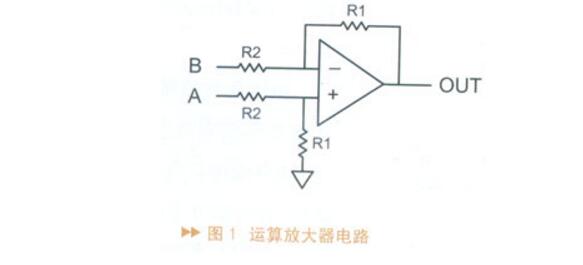

故,我們是否可以用普通運放替代,因為普通運放就幾毛錢;電路如下:

我們來分析下:

- 由虛短可得,V2 = VA,V1 = VB;

- 由虛斷可得,(VA - VB)/R0 = (V02 - V01)/(R1+R2+R0);

則:(V2 - V1)/R0 = (Vo2 - Vo1)/(R1+R2+R0);

對于后級電路,我們知道是差分放大電路,我們令R3 = R4,R5 = R6;

則:Vo = R6/R4*(Vo2 - Vo1);

我們令R1 = R2;

即Vo = (V2 -V1)(2R2+R0)R6/(R0R4);

當然用普通運放實現和用集成的儀表放大器各有優劣:

我們可以根據我們需要來考究;

今天就到這里,謝謝大家閱讀;

-

放大電路

+關注

關注

104文章

1787瀏覽量

106662 -

運算放大器

+關注

關注

215文章

4929瀏覽量

172839 -

運放

+關注

關注

47文章

1163瀏覽量

53062 -

儀表放大器

+關注

關注

17文章

409瀏覽量

71212 -

CMRR

+關注

關注

0文章

81瀏覽量

14800

發布評論請先 登錄

相關推薦

儀表放大器電路的設計

差分輸出儀表放大器電路分析

儀表放大器電路分析

儀表放大器電路分析

評論