Via pillar,又可以叫Via ladder。貌似Cadence家喜歡叫pillar,synopsis喜歡叫l(wèi)adder,我也不知道它們?yōu)樯恫荒芙y(tǒng)一一下名稱(chēng)。這應(yīng)該是這兩年新出的概念,主要應(yīng)用在5nm及以下先進(jìn)工藝制程中。我就以我個(gè)人的理解稍微介紹一下這種技術(shù)。

Pillar,柱子,ladder,梯子。它指的是這樣一種結(jié)構(gòu):當(dāng)需要把金屬?gòu)牡蛯舆B到高層時(shí),比如M1到M5,每一層都多添加一些shape,這些shape分別與上下層彼此通過(guò)VIA相連,最終連到M5再合并為一個(gè)shape出來(lái),中間的M2到M4就像一個(gè)個(gè)井字或者田字,就像我們玩的抽木塊的游戲一樣。

更具體一點(diǎn),比方說(shuō)一個(gè)clock cell M1出Z pin,我現(xiàn)在給他上了NDR,希望他能在M5層繞線。傳統(tǒng)的方法就是直接一摞via直接疊上去,電流路線只有一個(gè)。

現(xiàn)在用了via ladder,我可以pin上打三個(gè)via,然后M2接3個(gè)shape;然后M2上每個(gè)shape打兩個(gè)via,M3接兩個(gè)shape,每個(gè)shape都接到M2的三個(gè)shape上。

這2個(gè)還是3個(gè)還是更多都是可以指定的。如此一來(lái),每層金屬不再是單一的一個(gè)via,而是相當(dāng)于增加了多個(gè)shape,有多條電流通路,給人的感覺(jué)就像整個(gè)結(jié)構(gòu)的支撐更多了。

那么,這樣的設(shè)計(jì)意義何在?可能大家也能猜到了,最重要的意義就是減小了電路的電阻,并且分擔(dān)了電流,能有效改善EM(電遷移)的問(wèn)題。相對(duì)于傳統(tǒng)的方法:加redundant via來(lái)說(shuō),加via ladder的改善效率無(wú)疑更高一些。

另外,加redundant via還有諸多限制,好像在用到DPT時(shí)就比較難加,也不是想加就能加的。Via pillar除了有改善EM的好處外,還可以想到對(duì)timing肯定也會(huì)更好,對(duì)IR drop也會(huì)更好,對(duì)DFM(可制造性)更好,等等。

那么,既然有如此多好處,我們?yōu)槭裁床辉诓荒敲聪冗M(jìn)的工藝就用到呢?答案是沒(méi)必要。老的工藝線寬沒(méi)有到10nm以下,電阻率本身也不高,EM的I limit也會(huì)相對(duì)大,打幾層via疊在一起其實(shí)也并沒(méi)有影響太多,而使用via ladder卻有一個(gè)致命的缺點(diǎn):占用繞線資源。

相對(duì)來(lái)講,繞線資源可是寶貴許多呀!所以一直到現(xiàn)在的先進(jìn)工藝制程,才開(kāi)始用到via ladder這種技術(shù)。

Via ladder的缺點(diǎn)也挺明顯的,它會(huì)占用許多繞線資源。它不僅僅是各個(gè)金屬層都少了一點(diǎn)那么簡(jiǎn)單,要知道,在用傳統(tǒng)的via單堆疊的方式時(shí),他可以不完全直上直下地堆疊,在層間可以靈活地稍微偏離一點(diǎn),來(lái)給其他net讓位置。

但是對(duì)于via ladder來(lái)說(shuō),它的結(jié)構(gòu)就相對(duì)穩(wěn)定,tool也不好更改,感覺(jué)就如同在那個(gè)區(qū)域加上了routing blockage一樣。所以,via ladder的使用還是要相對(duì)謹(jǐn)慎的,一般會(huì)用在clock cell上,一般其他的cell用的不多。

-

DFM

+關(guān)注

關(guān)注

8文章

463瀏覽量

28199 -

Via

+關(guān)注

關(guān)注

0文章

44瀏覽量

19232 -

DPT

+關(guān)注

關(guān)注

0文章

12瀏覽量

6837

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

求助,用TXS0108E芯片有個(gè)疑問(wèn)想請(qǐng)教一下

想請(qǐng)教一下華芯拓遠(yuǎn)的工程師關(guān)于ASIC芯片調(diào)試軟件的問(wèn)題

請(qǐng)問(wèn)一下INA333這個(gè)芯片很容易壞嗎?

自感線圈斷電時(shí)燈泡為啥會(huì)閃亮一下

請(qǐng)問(wèn)一下LM2904輸入阻抗實(shí)際是多少?

請(qǐng)問(wèn)一下有無(wú)可以替代INA122UA的其他型號(hào)芯片?

做了個(gè)205W的快充!實(shí)測(cè)了一下,有點(diǎn)東西啊……

歡創(chuàng)播報(bào) 支付寶“碰一下”正式發(fā)布

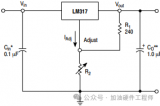

總結(jié)一下LM317的幾種經(jīng)典應(yīng)用電路

大神幫忙讓我理解一下該電路的原理?

聊一下常見(jiàn)的幾種無(wú)線遙控器及其可能使用的晶振頻率

求助一下

簡(jiǎn)單介紹一下電源紋波與電容嘯叫

請(qǐng)問(wèn)一下背面供電技術(shù)是如何降低芯片功耗的?

盤(pán)點(diǎn)一下高通CES 2024汽車(chē)創(chuàng)新技術(shù)

介紹一下芯片的VIA pillar

介紹一下芯片的VIA pillar

評(píng)論