共讀好書

魏紅軍 謝振民

摘要:

電化學(xué)沉積技術(shù),作為集成電路制造的關(guān)鍵工藝技術(shù)之一,它是實現(xiàn)電氣互連的基石,主要應(yīng)用于集成電路制造的大馬士革銅互連電鍍工藝和后道先進封裝 Bump、RDL、TSV 等電鍍工藝。受 WLP、2.5D、3D、SIP 等先進封裝技術(shù)的推動,未來 3 年市場空間可達 15~20 億美元。

0 引言

電 化 學(xué) 沉 積 技 術(shù), 簡 稱 ECD(Electrical Chemical Deposition)技術(shù),也是應(yīng)用于半導(dǎo)體相關(guān)技術(shù)行業(yè)的電鍍技術(shù),作為集成電路制造的關(guān)鍵工藝技術(shù)之一,它是實現(xiàn)電氣互連的基石。電化學(xué)沉積技術(shù)主要應(yīng)用于集成電路制造的大馬士革銅互連工藝制程和后道先進封裝 Bump、RDL、TSV 等工藝制程,也可應(yīng)用于化合物、MEMS 中深孔加工、金凸塊、金屬膜沉積等領(lǐng)域。

1 電化學(xué)沉積技術(shù)在銅互連中的應(yīng)用

隨著晶體管尺寸不斷縮小,進入 130 nm 制程以后,鋁互連工藝已經(jīng)不能滿足集成電路集成度、速度和可靠性持續(xù)提高的需求。與鋁相比,銅的電阻率只有鋁的一半左右,較低的電阻率可以減少金屬互連的 RC 延時,可以降低器件的功耗,并且銅的電遷移特性遠好于鋁,因此,銅已逐漸取代鋁成為金屬互連的主要材料。

由于銅很難進行干法刻蝕,因此傳統(tǒng)的金屬互連工藝已不再適用,擁有鑲嵌工藝的鍍銅技術(shù)成為銅互連的主要制備工藝,業(yè)界也稱為大馬士革銅互連工藝。

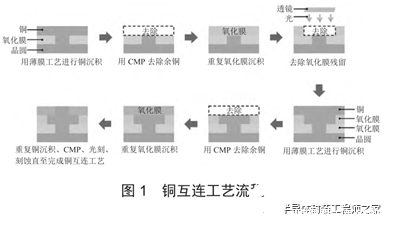

首先沉積阻擋層 TaN/Ta,防止銅原子向介質(zhì)層擴散,以免降低介質(zhì)層的絕緣屬性;之后在阻擋層上沉積銅種子層,然后進行電鍍填充,如圖 1 所示 ;填充后多余的銅可以用化學(xué)機械拋光(CMP)方法去除 ;完成后沉積氧化膜,多余的氧化膜采用光刻和刻蝕工藝去除;整個過程需要不斷重復(fù)直至完成銅互連布線為止。目前銅互連層最多可達 15層以上,據(jù)臺積電報道,在其最先進的 5 nm 芯片中,銅互連線長度可以達到 100 km。

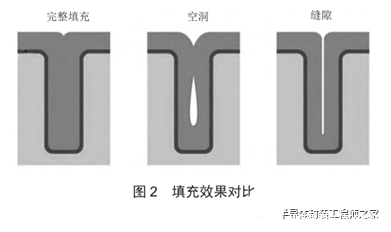

完全填充高深寬比的互連溝槽是大馬士革互連工藝最大的挑戰(zhàn),如圖 2 所示,如不能很好的控制電鍍工藝過程,則會形成空洞或縫隙,降低芯片的電性能和可靠性,并影響芯片制造工藝的產(chǎn)品良率。

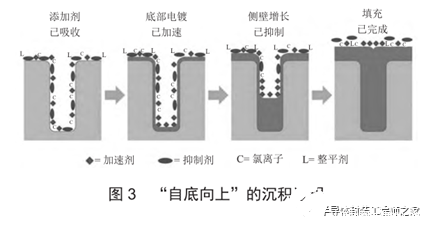

目前銅互連電鍍主要采用硫酸銅工藝體系,電鍍液成分主要包括硫酸、銅離子、氯離子、加速劑、抑制劑和整平劑等六種組分。如圖 3 所示,理想的填充過程是自底向上的沉積過程,這就需要鍍銅溶液中抑制劑、加速劑等不同添加劑的合理配比,達到“溝槽內(nèi)加速、溝槽口抑制”的效果,從而實現(xiàn)低電阻率、無空洞和高可靠性的銅布線結(jié)構(gòu)。

電鍍之后的銅晶粒很小,必須通過退火工藝來增加晶粒大小、降低電阻、增加電遷移可靠性以及增加 CMP 的穩(wěn)定性。但過度的退火會增加 CMP之后的缺陷,所以合適的退火方式將非常重要。

2 電化學(xué)沉積技術(shù)在先進封裝中的應(yīng)用

隨著集成電路工藝尺寸不斷縮小,即將接近物理極限,先進封裝技術(shù)被推向舞臺的正中央,WLP、2.5D、3D、SIP 等技術(shù)的發(fā)展成為延續(xù)摩爾定律的最佳選擇。實現(xiàn)芯片 Z 方向電氣連接的硅通孔技術(shù)(TSV),實現(xiàn)倒裝或堆疊芯片之間電氣連接和應(yīng)力緩沖的凸點技術(shù)(Bump),實現(xiàn)芯片 XY 平面電氣延伸和互連的金屬層重布線技術(shù)(RDL),這三者即是后摩爾時代集成電路先進封裝技術(shù)的關(guān)鍵要素。

2.1 硅通孔技術(shù)

TSV(through silicon via)技術(shù)是穿透硅通孔技術(shù)的英文縮寫,簡稱硅通孔技術(shù),是三維集成電路中堆疊芯片實現(xiàn)互連的一種技術(shù)解決方案。它是在芯片和芯片之間、晶圓和晶圓之間制作垂直導(dǎo)通,通過 Z 方向通孔實現(xiàn)芯片之間的互連。TSV 技術(shù)能夠使芯片在三維方向堆疊的密度最大,芯片之間的互連線最短,外形尺寸最小,大大改善芯片速度和低功耗的性能。

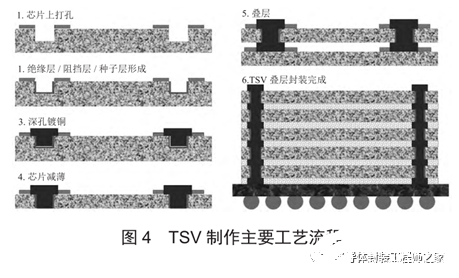

如圖 4 所示,TSV 主要工藝流程包括硅通孔的制作,絕緣層、阻擋層、種子層的沉積,銅的電鍍填充,通過 CMP 去除多余金屬,晶圓減薄,晶圓鍵合等;在整個 TSV 制造工藝中,硅通孔的鍍銅填充是目前的關(guān)鍵技術(shù)難點之一,與銅互連電鍍相似,同樣需要自底向上的沉積過程,但 TSV 電鍍的尺寸更大,通常需要更長的沉積時間,更高的電鍍速率以及多個工藝步驟。

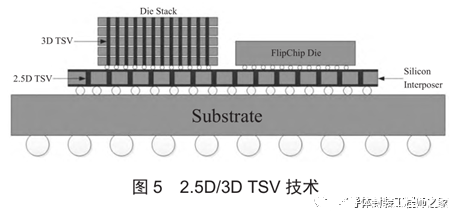

TSV 按照集成類型的不同分為 2.5D TSV 和3D TSV,2.5D TSV 指的是硅轉(zhuǎn)接板上的 TSV,3DTSV 是指芯片上制作硅通孔,連接上下層芯片,如圖 5 所示。

TSV 是 3D 系統(tǒng)集成的關(guān)鍵技術(shù)和發(fā)展趨勢,目前已經(jīng)可以實現(xiàn)深寬比為 10∶1 的 TSV 結(jié)構(gòu),且向著更高深寬比發(fā)展。隨著工藝的提升,硅通孔的孔徑越來越小,密度越來越大,目前最先進的TSV 工藝,可以在 1 mm 2 的芯片上制作高達 10 萬個以上硅通孔,從而支撐更高密度的芯片互連,同樣對 TSV 的電鍍填充也提出了更高的工藝要求。

2.2 凸點技術(shù)

作為金屬凸點,Bump 對芯片來說起著電氣互連和應(yīng)力緩沖的作用,從 Bondwire 工藝發(fā)展到FlipChip 工藝,再到 3D 堆疊芯片工藝,Bump 至關(guān)重要。

Bump 形狀有很多種,最常見的為球狀和柱狀,也有塊狀等其它形狀。材料一般為 Cu、Au、Ni、Ag-Sn 等,有單金屬的凸點,也有合金凸點,最常用的凸點材料是 Cu 和 Au。

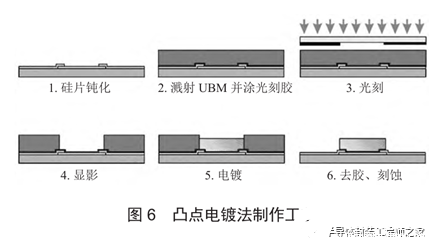

電鍍法制作凸點是目前最為普遍且工藝成熟的凸點制作方法,該方法不僅加工工序少,工藝簡便易行,適于大批量生產(chǎn),且可制作各類凸點,IC芯片上的 I/O 數(shù)、焊區(qū)尺寸大小及凸點節(jié)距均不受限。

凸點電鍍法制作工藝流程如圖 6 所示,先將硅片進行鈍化,然后蒸發(fā) / 濺射 UBM 凸點下金屬層,接下來進行光刻、顯影,就形成了所需的電鍍窗口,然后進行電鍍工藝,最后去除光刻膠、刻蝕 UBM金屬層。

2.3 重布線技術(shù)

重 布 線 技 術(shù), 簡 稱 RDL(Redistribution Layer),起著 XY 平面電氣延伸和互連的作用。RDL 技術(shù)的核心是在晶圓表面沉積金屬層和介質(zhì)層并形成相應(yīng)的金屬布線圖形,對芯片的 I/O 進行重新布局,根據(jù)后續(xù)封裝工藝需求,將其布局到新的、更為寬松的區(qū)域,并可形成面陳列排布。

在 2.5D IC 集成中,除了硅轉(zhuǎn)接板中的 TSV 技術(shù)外,RDL 技術(shù)同樣關(guān)鍵,通過 RDL 將電氣連接分布到不同的位置,從而將硅轉(zhuǎn)接板上方芯片的凸點和轉(zhuǎn)接板下方的凸點連接。

在 3D IC 集成中,對于同種芯片來說,上下堆疊直接通過 TSV 就可以完成電氣互連,對于異質(zhì)異構(gòu)芯片,則需 RDL 將芯片的 I/O 重新布局進行對準(zhǔn),從而完成芯片的互連。

在 FIWLP、FOWLP 先進封裝中,RDL 是最為關(guān)鍵的技術(shù),通過 RDL 將 I/O 進行 Fan-In 或者Fan-Out,形成不同類型的封裝形式。Fan-Out 扇出型封裝有兩大分支:扇出型晶圓級封裝和扇出型面板級封裝。對于板級封裝來說,由于面板的大尺寸和更高的載具使用率,帶來遠高于晶圓級封裝的規(guī)模經(jīng)濟效益,作為其核心的 RDL 技術(shù)也得到了業(yè)界更多的關(guān)注。

隨著工藝技術(shù)的發(fā)展,通過 RDL 形成的金屬布線的線寬和線間距也越來越小,從而提供更高的互連密度。目前重布線層 RDL 多采用電化學(xué)沉積的方式來完成。

3 電化學(xué)沉積工藝設(shè)備國內(nèi)外廠商情況及行業(yè)前景

國外廠商方面,前道銅互連電鍍設(shè)備主要被美國 Lam 壟斷 ;后道先進封裝電鍍設(shè)備廠商主要包括美國 AMAT、美國 Lam、日本 EEJA、新加坡ASM 等。

國內(nèi)廠商方面,主要供應(yīng)商上海盛美,科創(chuàng)板上市公司,電鍍設(shè)備營業(yè)收入從 2018 年 1200 萬增至 2021 年 2.74 億元,2021 年實現(xiàn)量產(chǎn),交付 20臺電鍍設(shè)備,2022 年截止 5 月獲得 31 臺批量訂單,其中前道銅互連電鍍設(shè)備最高可以用于 28 nm 工藝節(jié)點。

2021 年全球半導(dǎo)體設(shè)備銷售額突破 1 000 億美元;其中ECD設(shè)備市場約10億美元,受WLP、2.5D、3D、SIP 等先進封裝技術(shù)的推動,未來 3 年市場空間可達 15~20 億美元。

半導(dǎo)體產(chǎn)業(yè)發(fā)展的決定性因素在于其生產(chǎn)設(shè)備,其產(chǎn)業(yè)制高點的競爭,歸根結(jié)底還是裝備制造業(yè)的競爭,因此有“一代設(shè)備、一代工藝、一代產(chǎn)品”之說。裝備制造也正是我國半導(dǎo)體產(chǎn)業(yè)中最薄弱的環(huán)節(jié),作為芯片制造的基石,對我國半導(dǎo)體產(chǎn)業(yè)鏈安全具有重大意義。

近幾年以來的全球芯片短缺,引發(fā)全球晶圓廠尤其國內(nèi)掀起擴產(chǎn)潮,對半導(dǎo)體設(shè)備的需求再次激增,作為上游的半導(dǎo)體設(shè)備行業(yè)持續(xù)增長,在行業(yè)擴容和國產(chǎn)替代的雙重作用下,正式步入發(fā)展的“黃金時代”。

審核編輯 黃宇

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423152 -

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361637 -

電化學(xué)

+關(guān)注

關(guān)注

1文章

322瀏覽量

20589

發(fā)布評論請先 登錄

相關(guān)推薦

電化學(xué)沉積技術(shù)在集成電路行業(yè)有哪些應(yīng)用呢?

模擬前端設(shè)計增強電化學(xué)傳感性能

新型銅互連方法—電化學(xué)機械拋光技術(shù)研究進展

18650鋰電池化學(xué)電源測試技術(shù)的發(fā)展歷程

電化學(xué)原理介紹和分析方法

應(yīng)用電化學(xué)傳感器的設(shè)計

基于電化學(xué)傳感器的Arduino兼容電化學(xué)氣體檢測電路CN0357

電化學(xué)傳感器的發(fā)展怎么樣?

電化學(xué)工作站有什么功能?

電化學(xué)知識:電化學(xué)的應(yīng)用與三電極體系!

電化學(xué)沉積技術(shù)在集成電路行業(yè)的應(yīng)用

電化學(xué)沉積技術(shù)在集成電路行業(yè)的應(yīng)用

電化學(xué)沉積技術(shù)在集成電路行業(yè)的應(yīng)用

評論