作者:Edwin Robledo,譯者:紫蔬

在Fusion 360中,我們關(guān)注于使電子工程師能夠輕松設(shè)計具有高速信號元器件的電路板。Fusion 360信號完整性擴(kuò)展程序有助于提高產(chǎn)品合規(guī)性和性能,減少實物電路板測試和原型制作的昂貴花費,并加快高速電路板開發(fā)進(jìn)程。

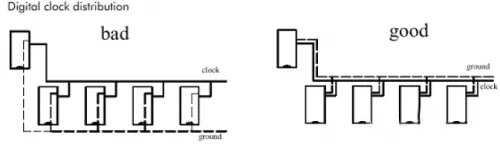

在使用高速信號元器件布置電路板時,需要遵循許多經(jīng)驗法則。讓我們看看其中的一些,探索為什么遵循它們是有意義的,并了解什么時候可以不用。

1.盡可能保持您的布線路徑短而直

這個經(jīng)驗法則是一個金標(biāo)準(zhǔn)。短直線布線具有最小的時間延遲,并保持一致的阻抗。像Fusion 360 Signal Integrity Extension(信號完整性擴(kuò)展程序)這樣的電路板布局模擬軟件可以計算沿著其長度的跡線的阻抗,讓您知道不連續(xù)性是否存在以及在哪里存在。

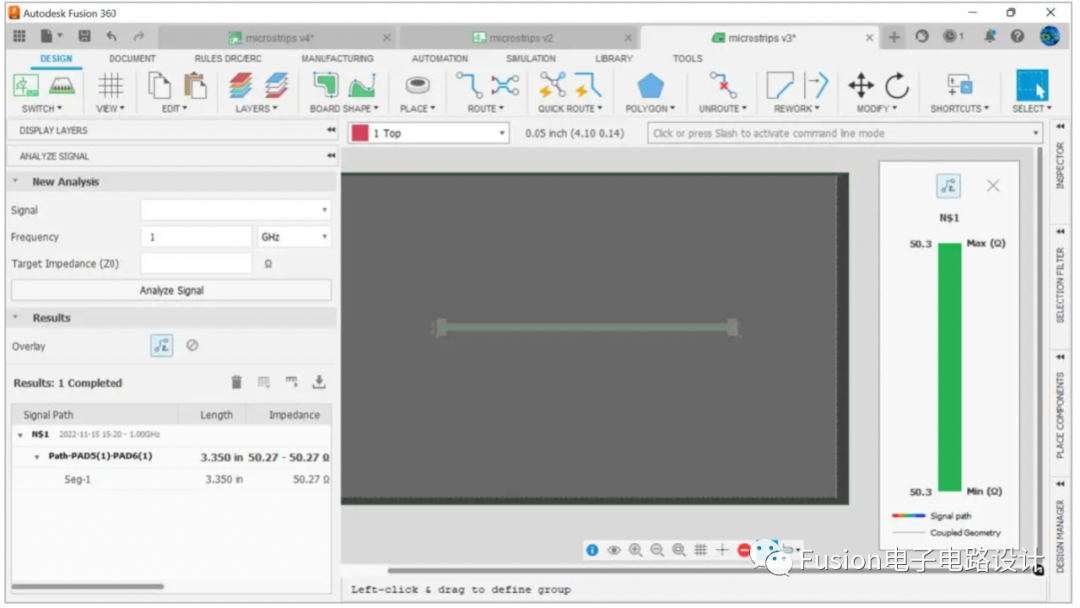

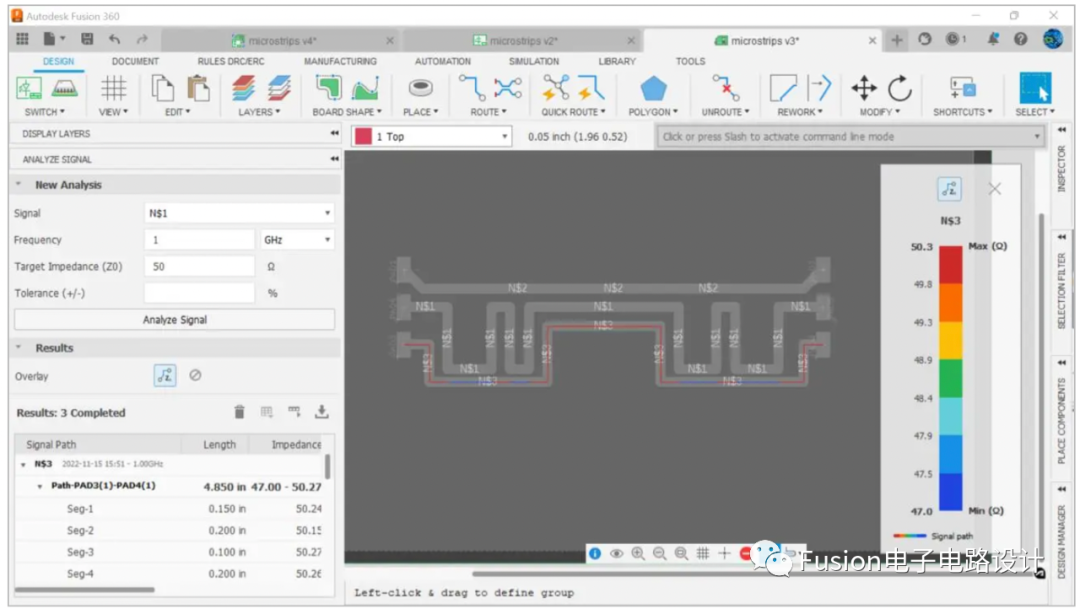

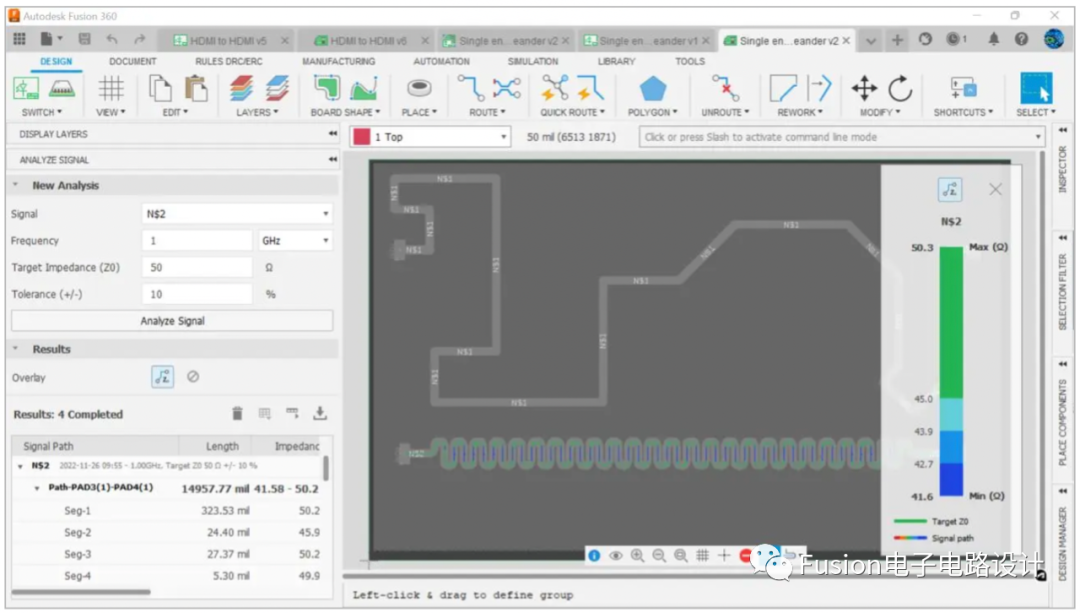

使用Fusion 360信號完整性擴(kuò)展程序,我們可以看到直線布線沿其長度呈現(xiàn)恒定阻抗。

Fusion 360 Electronics的信號完整性擴(kuò)展程序擴(kuò)展顯示了具有恒定50.3Ω阻抗的布線。

2.不要使用90°角(沒關(guān)系,你可以使用)

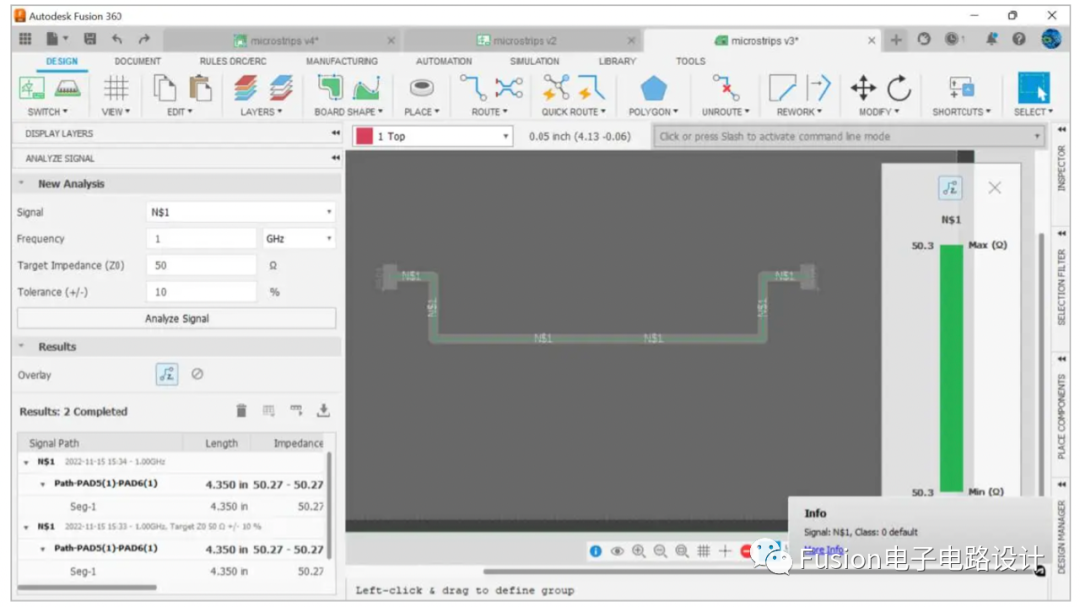

這是一條常見的規(guī)則,幾乎與被反駁的頻率一樣頻繁。這條規(guī)則的共同點是,90°角會導(dǎo)致阻抗不連續(xù),也就是說,當(dāng)直線軌跡上有90°角時,阻抗會發(fā)生變化。除非你在亞毫米波段工作,否則情況并非如此。請注意,使用90°直角布線的該跡線保持恒定阻抗。

90°直角布線不會影響跡線的阻抗。

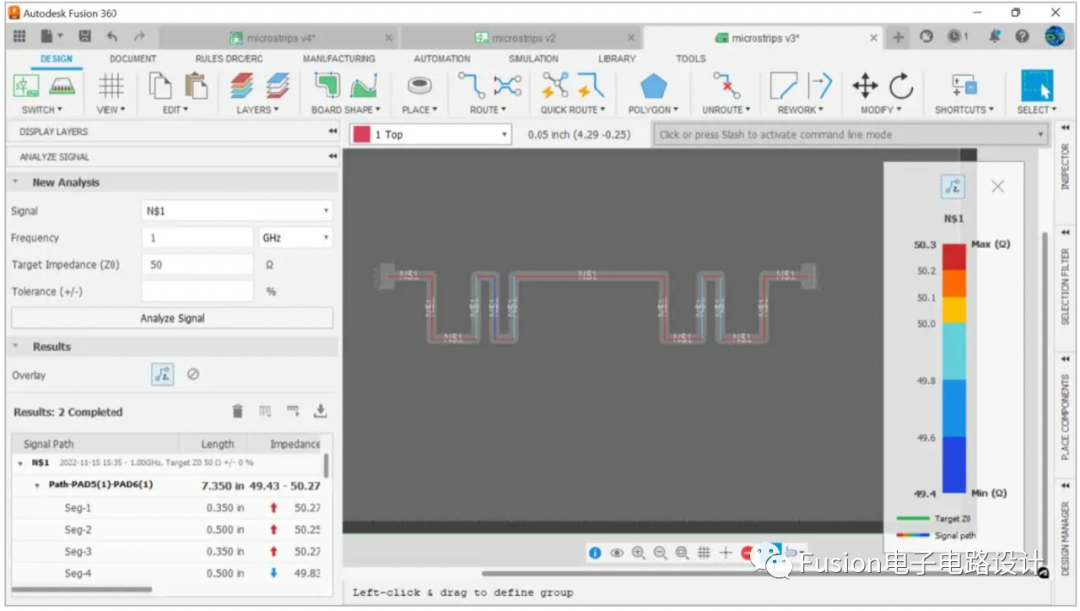

在高速信號設(shè)計中布線時,需要考慮電場重疊的情況,這也是我們在線路下面敷銅的原因。一起看看如果我們把線路來回移動靠近它自己的話,會發(fā)生什么吧。

重疊的電場將導(dǎo)致跡線阻抗的變化。

我們看到阻抗現(xiàn)在在變化。是的,雖然變化不是很多,但它仍然在變化,因為電場現(xiàn)在存在重疊的情況。

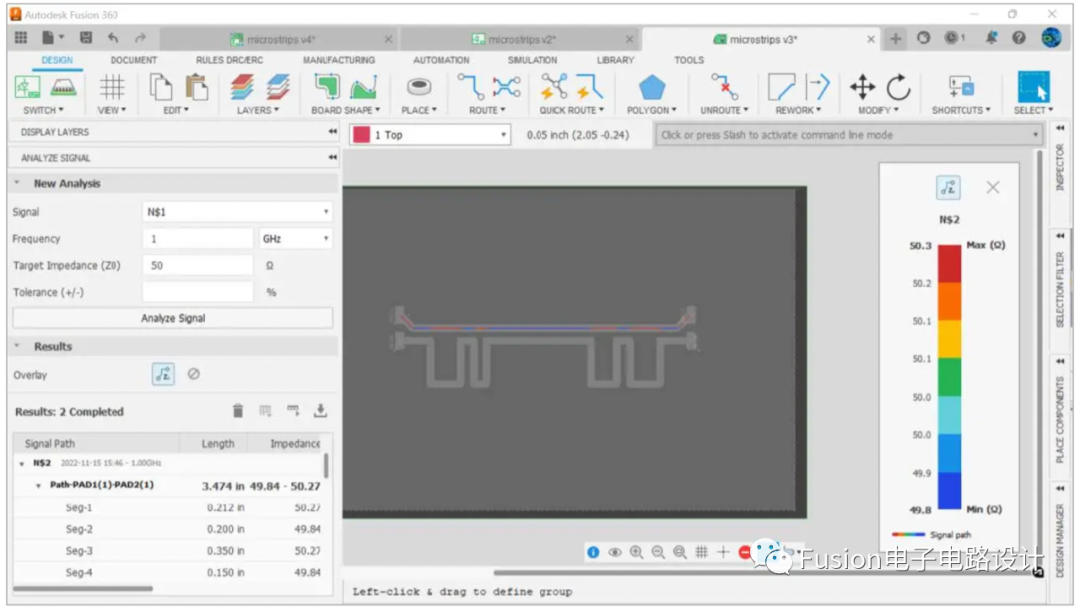

相鄰跡線在確定阻抗方面也起著作用。

相鄰布線也會改變線路的阻抗。

請注意,當(dāng)磁場由于彼此靠近而可能重疊時,會發(fā)生阻抗變化。

還要注意,跡線越靠近相鄰跡線,阻抗不連續(xù)性越大。

跡線越近,阻抗變化越大。

因此,90°角在阻抗不連續(xù)性中不起作用。重要的是相鄰的電場足夠接近而重疊——這將影響阻抗。

那么,有什么理由遵循沒有90°直角的規(guī)則嗎?是的,如果您正在設(shè)計高壓電路板,任何尖銳的角落都會集中電場,并可能導(dǎo)致發(fā)生弧閃(Flashover Arcs)。使用45°角的另一個優(yōu)點是跡線更短,環(huán)路面積更小,從而減少EMI(電磁干擾),信號到達(dá)更快。

說到信號到達(dá),讓我們來看看長度匹配的重要性。

3.長度匹配高速信號,避免信號到達(dá)時間不匹配

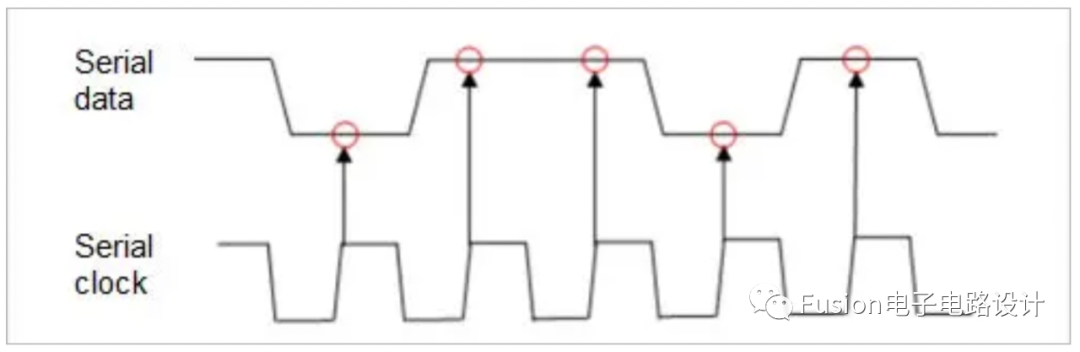

當(dāng)布線高速信號時,重要的是跟蹤長度匹配,因為長度不匹配意味著信號到達(dá)時間不匹配。考慮一個高速時鐘信號及其相關(guān)數(shù)據(jù)。

來源:Difference Between Serial Communication Function With and Without Clock | Renesas Customer Hub.

https://en-support.renesas.com/knowledgeBase/17943143

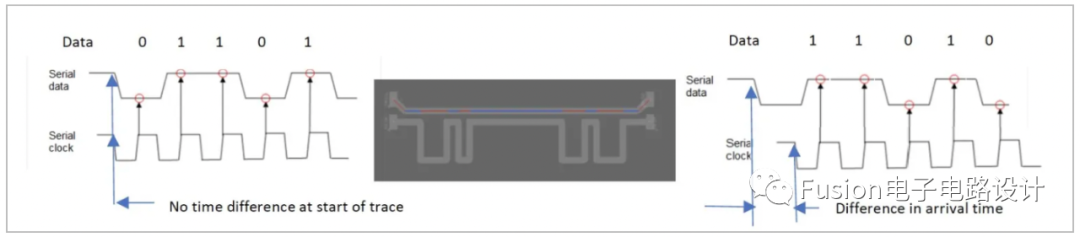

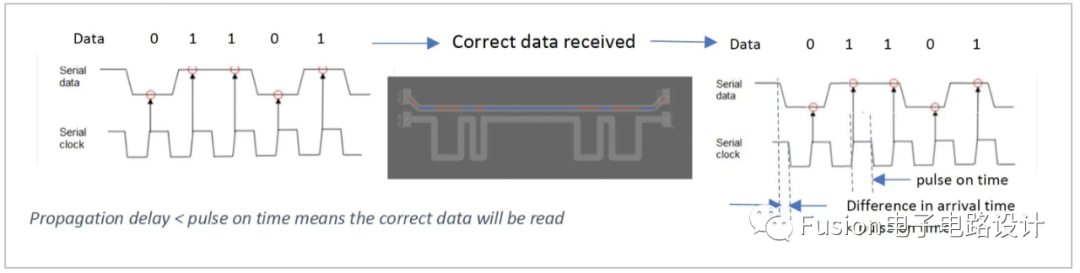

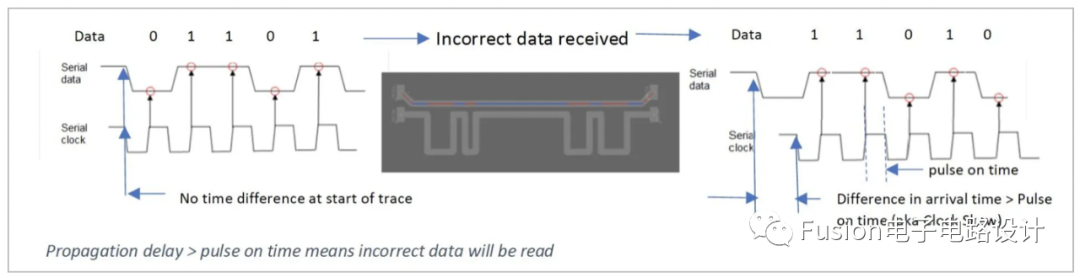

該時鐘的上升沿確定要讀取的數(shù)據(jù)是零還是一。對于高速信號,信號沿軌跡傳播所需的時間(稱為傳播延遲)可以在信號是否被正確讀取方面發(fā)揮作用。檢查下面的情況,底部時鐘跡線比頂部數(shù)據(jù)跡線長。

不相等跡線長度導(dǎo)致的脈沖到達(dá)時間有所差異(也稱為傳播延遲或時間延遲)。

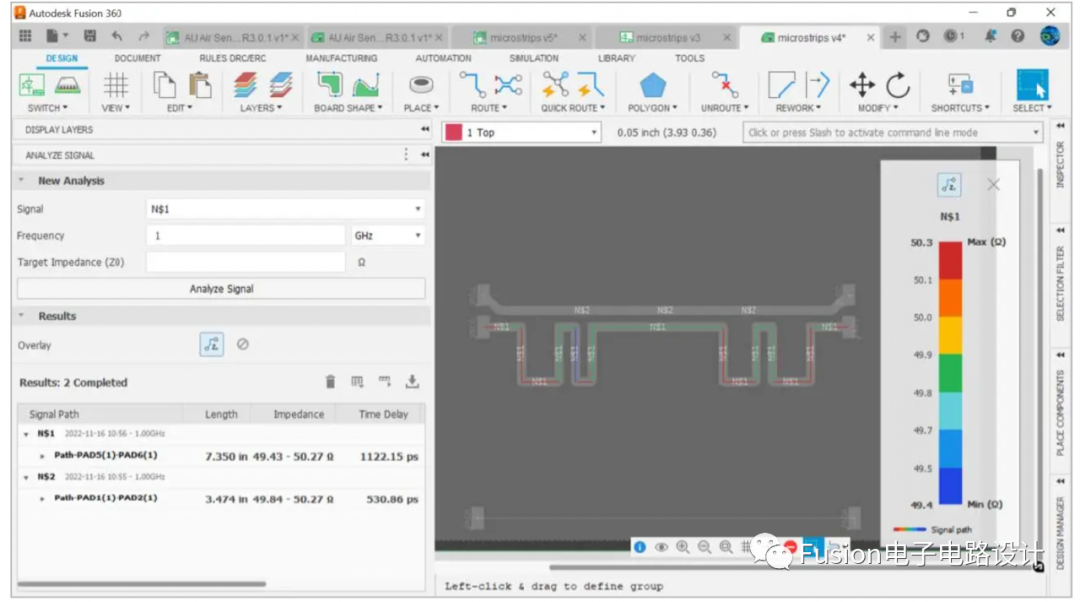

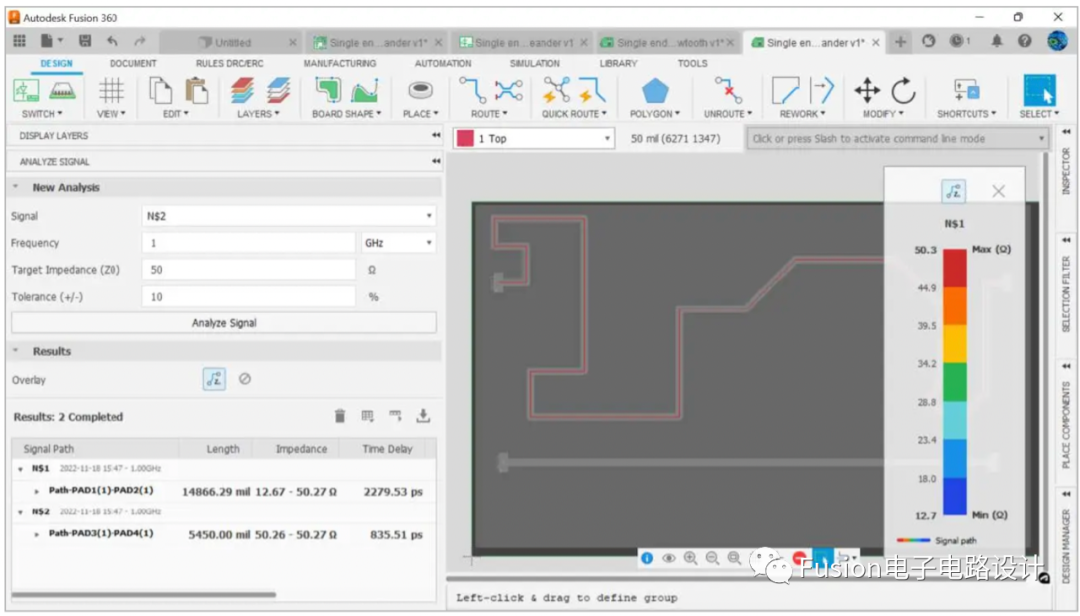

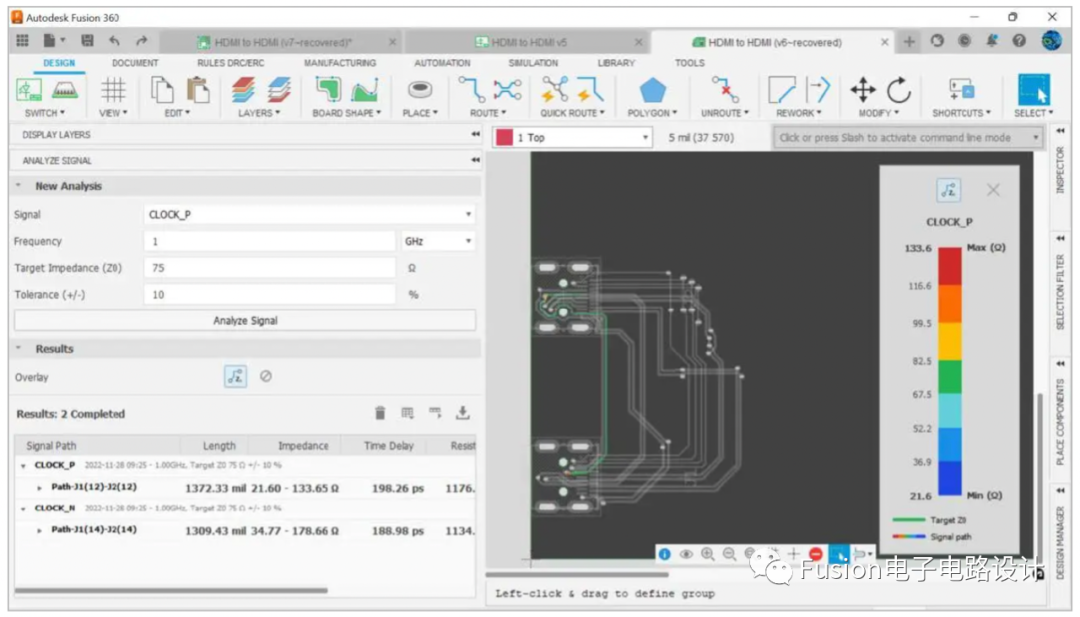

在這種情況下,時鐘信號比串行數(shù)據(jù)信號延遲得多,接收器不能讀取到01101,而是將錯誤地“看到”11010。所以高速信號的長度匹配很重要。Fusion 360中的信號完整性擴(kuò)展程序計算了跡線中的傳播延遲,從而可以很容易地看出信號的定時是否會出現(xiàn)問題。

Fusion 360 Electronics的信號完整性擴(kuò)展程序?qū)槟嬎阚E線傳播延遲。

這里我們可以看到,兩條跡線之間的傳播時間差為591.29ps。如果我們的時鐘頻率脈沖開啟時間開始接近兩條跡線之間的傳播速度差,我們將在數(shù)據(jù)讀取中出現(xiàn)錯誤。

考慮傳播時間差小于脈沖接通時間的情況。

我們可以在上面看到發(fā)送的數(shù)據(jù) = 接收的數(shù)據(jù)。

然而,到達(dá)時間差越接近脈沖接通時間,就越可能發(fā)生錯誤。

數(shù)據(jù)和時鐘之間的時間差稱為時鐘偏差。這就引出了我們的下一條經(jīng)驗法則。

4.保持時鐘偏差小于時鐘周期的1/10

我們可以從上面的示例中看到,這個經(jīng)驗法則使時鐘邊緣遠(yuǎn)離數(shù)據(jù)轉(zhuǎn)換區(qū)。如果我們的時鐘和數(shù)據(jù)信號的差異大于時鐘周期的1/10,我們需要延長更快的信號。

5.延長跡線以均衡定時延遲

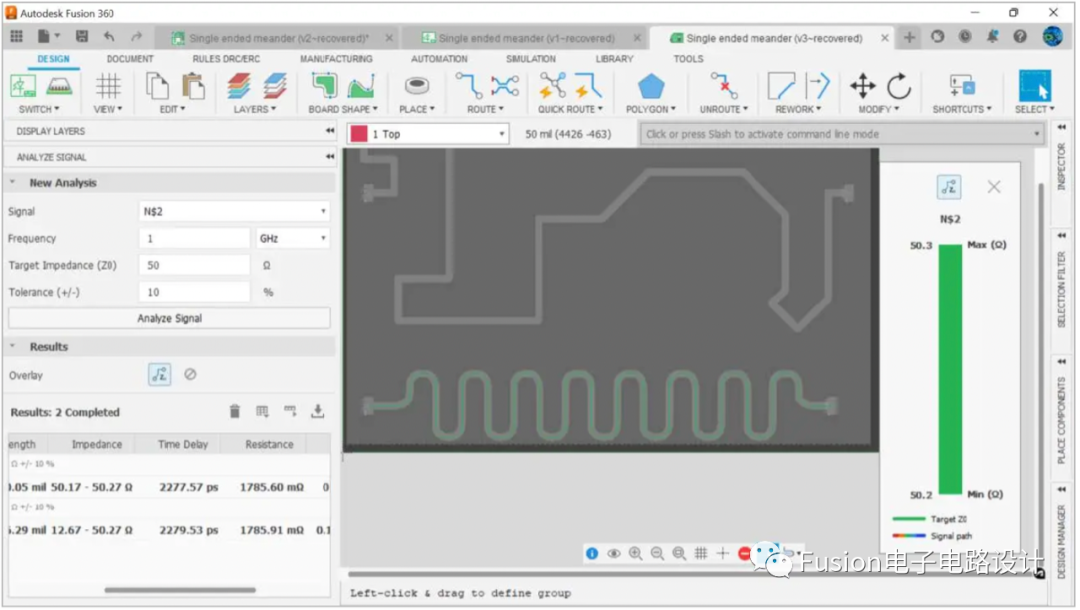

有幾種方法可以延長跡線,以便將時間差異納入規(guī)范中。如果長度不匹配很小,可以通過重新布線跡線使其稍長來延長。Fusion 360 Electronics中的信號完整性擴(kuò)展程序工具將顯示跡線的傳播延遲,您可以決定是否需要調(diào)整長度或使用折彎跡線命令延長長度。

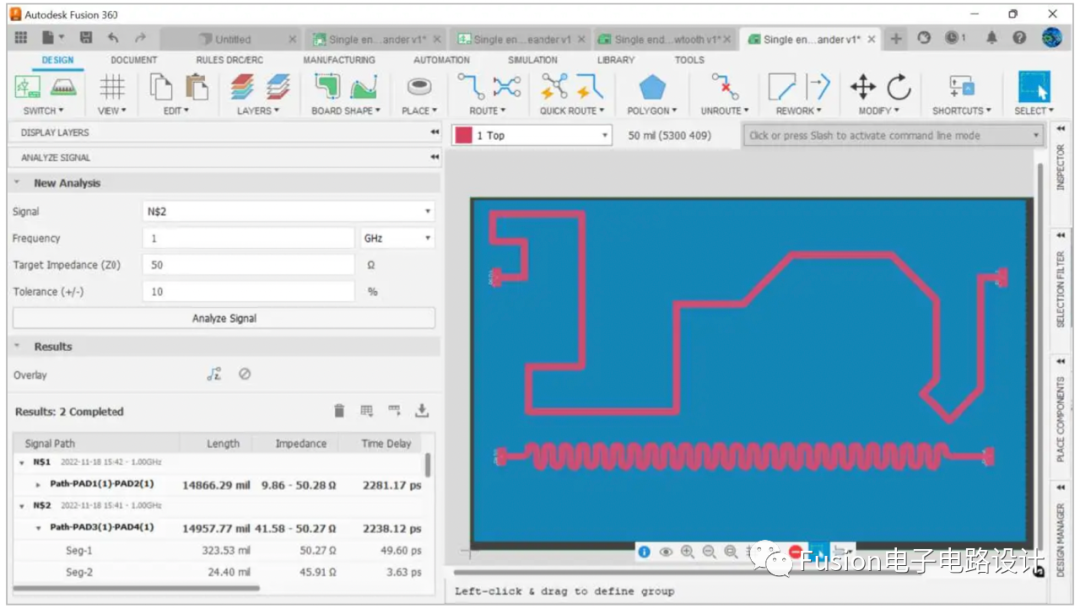

6.折彎線路時遵循4X規(guī)則

折彎意味著來回移動跡線以延長它。考慮所示的電路板,注意底部跡線比頂部跡線短得多,而且速度明顯快。

頂部跡線大約是底部跡線的兩倍長。

折彎底部跡線會導(dǎo)致更長的長度和傳播延遲,這可能在規(guī)范范圍內(nèi)。Fusion 360 Electronics允許您在單端信號和差分信號之間進(jìn)行迂回。

底部跡線加長以匹配頂部跡線的長度。

當(dāng)折彎時,電路板設(shè)計者通常遵循4X規(guī)則:將折彎之間的距離保持為跡線寬度的4X(4倍),因為這將最小化阻抗不連續(xù)性。讓我們看看這個例子中的跡線阻抗。

底部跡線由于間距小而緊密耦合。

相鄰跡線之間存在許多不連續(xù)性,這是電場相互重疊導(dǎo)致的。看看當(dāng)我們將間距設(shè)為跡線寬度的4倍時會發(fā)生什么。阻抗現(xiàn)在變得一致啦!

阻抗現(xiàn)在一致啦。

差分布線也可能需要延長,但讓我們等到稍后討論差分信號時再說吧。

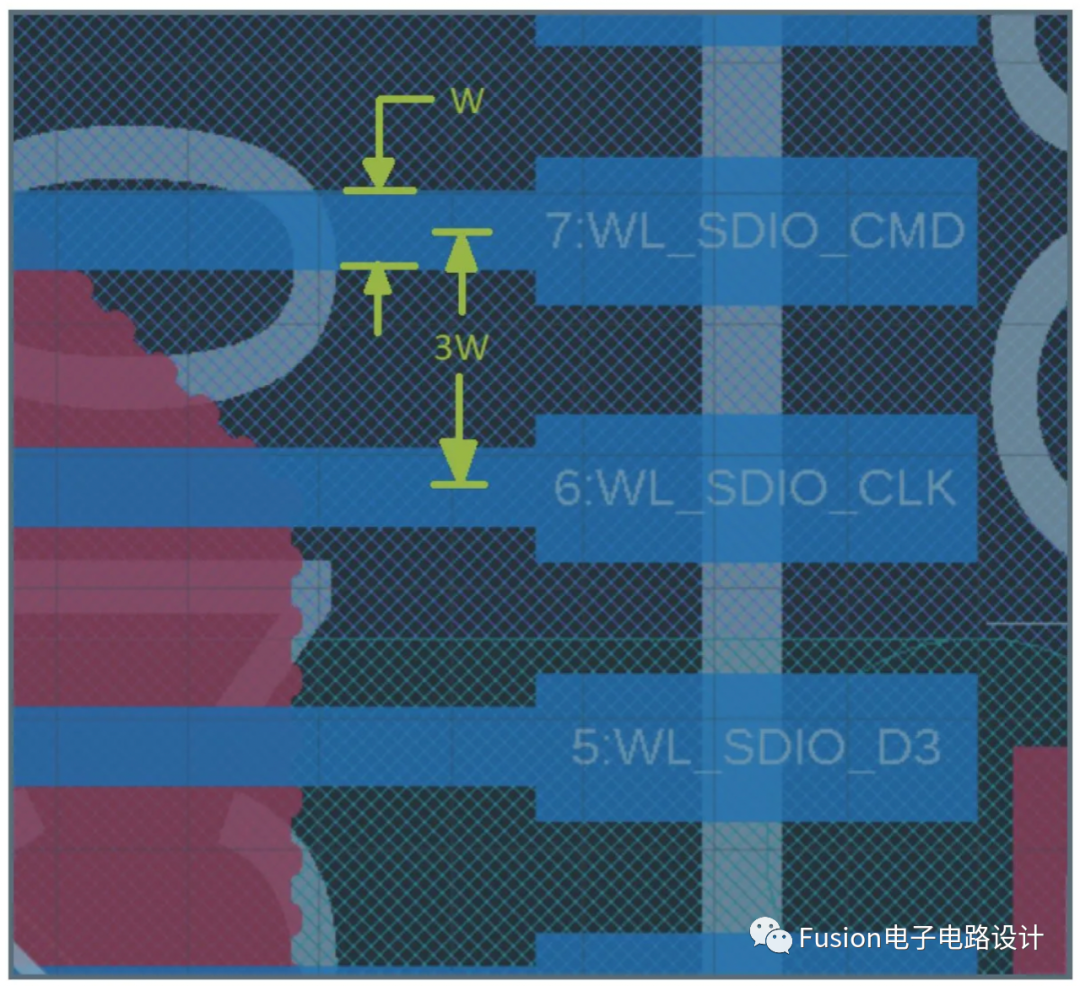

7.遵循3W規(guī)則以最小化串?dāng)_

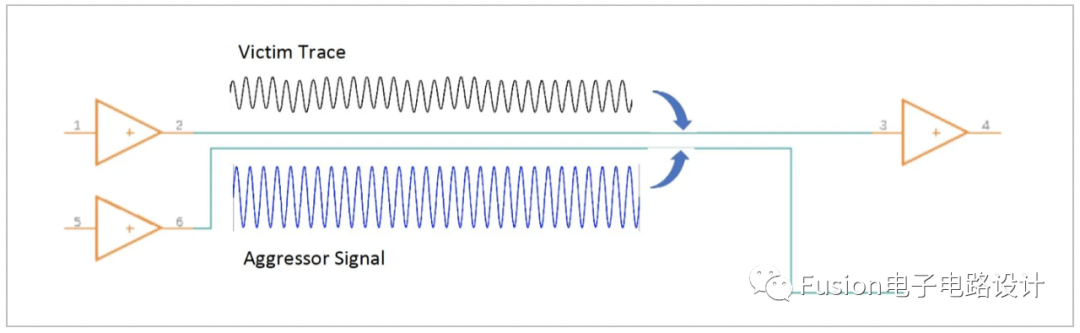

在早期的電話時代,如果承載通話的電纜中的電線并排,您可以聽到鄰居的談話。這種現(xiàn)象稱為“串?dāng)_”。

考慮傳統(tǒng)的單端數(shù)字信號。數(shù)據(jù)由代表1和0的高電壓和低電壓組成。

單端信號。

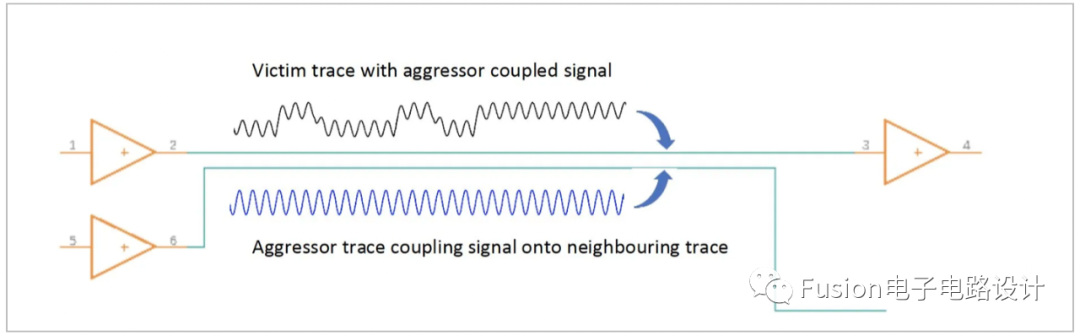

然而,附近的線路會將不需要的噪聲耦合到信號上。

如果來自“侵略信號”的耦合噪聲(不需要的信號)足夠大,則“受害信號”(需要的信號)可能被嚴(yán)重地混淆。

串?dāng)_的3W規(guī)則規(guī)定,平行跡線之間的距離應(yīng)至少為3W,從跡線的中心到中心進(jìn)行測量,以最小化它們之間的耦合,其中W=跡線的寬度。當(dāng)然,更多的空間是更好的,特別是當(dāng)頻率增加到GHz區(qū)域或長度過長時。還要注意的是,3W規(guī)則假設(shè)相鄰層上有敷銅,因為這將電場限制在跡線兩側(cè)較小的距離。

可以將兩條相鄰的跡線視為電容耦合的兩條跡線。電容器只是由絕緣體隔開的兩個極板,正好是兩個相鄰的跡線,絕緣體是它們之間的空氣。與電容器一樣,極板之間的距離越大,電容越小。電容越低,耦合信號越小。類似地,電路板越長,電容越大,耦合信號越大。所以,在高速設(shè)計中,盡量保持跡線短而遠(yuǎn)。

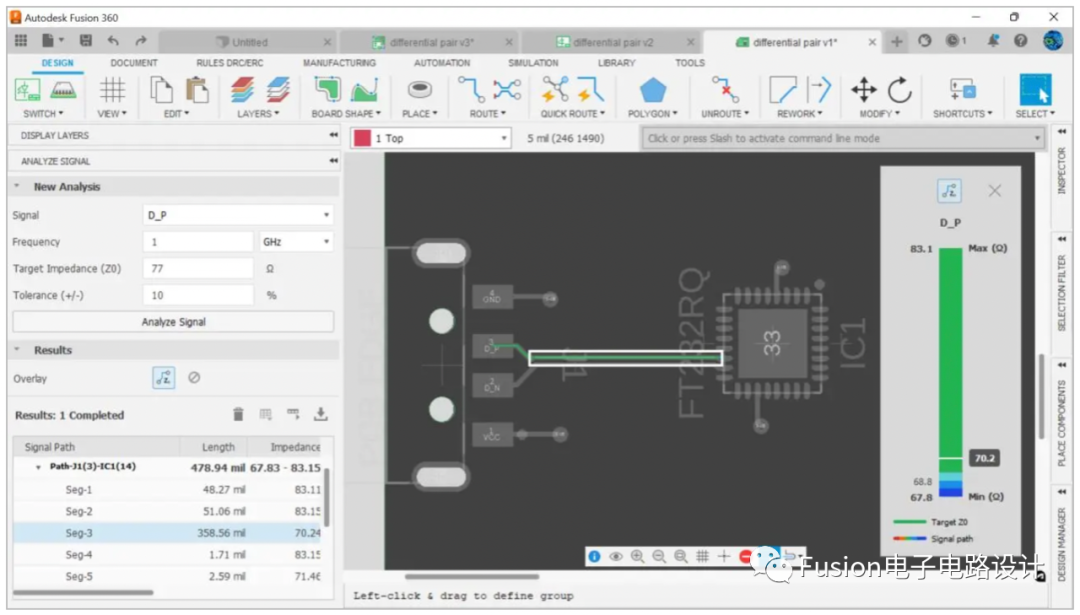

8.遵循差分時鐘的8W間隔(或探索其他規(guī)則)

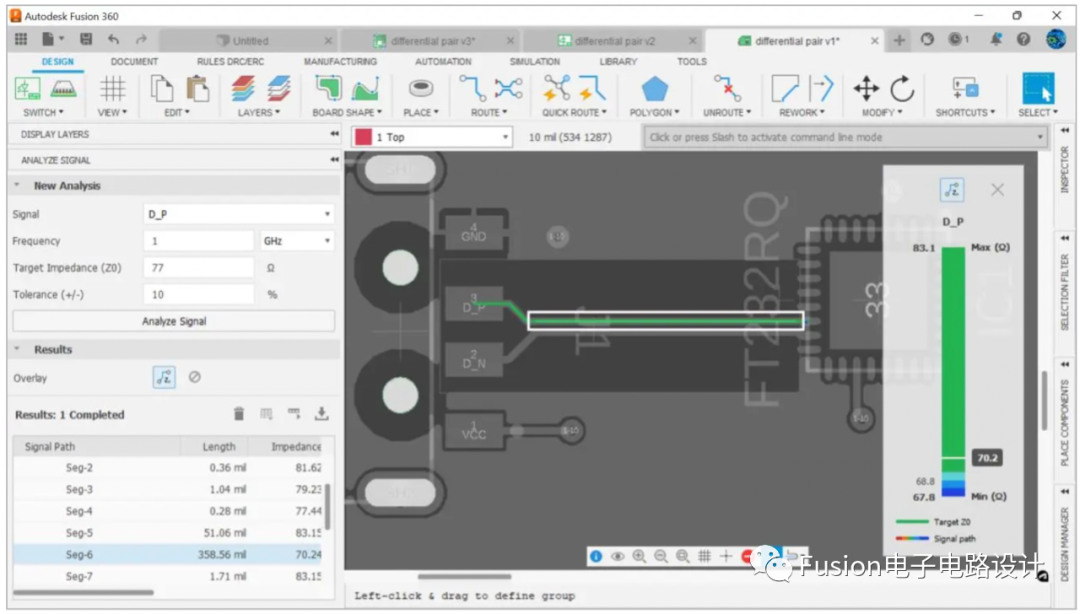

高速差分信號需要更大的間隔。此規(guī)則可保持所需的信號阻抗。此8W規(guī)則也適用于同一層上的敷銅。考慮以下USB差分信號:

70.2Ω阻抗的跡線。

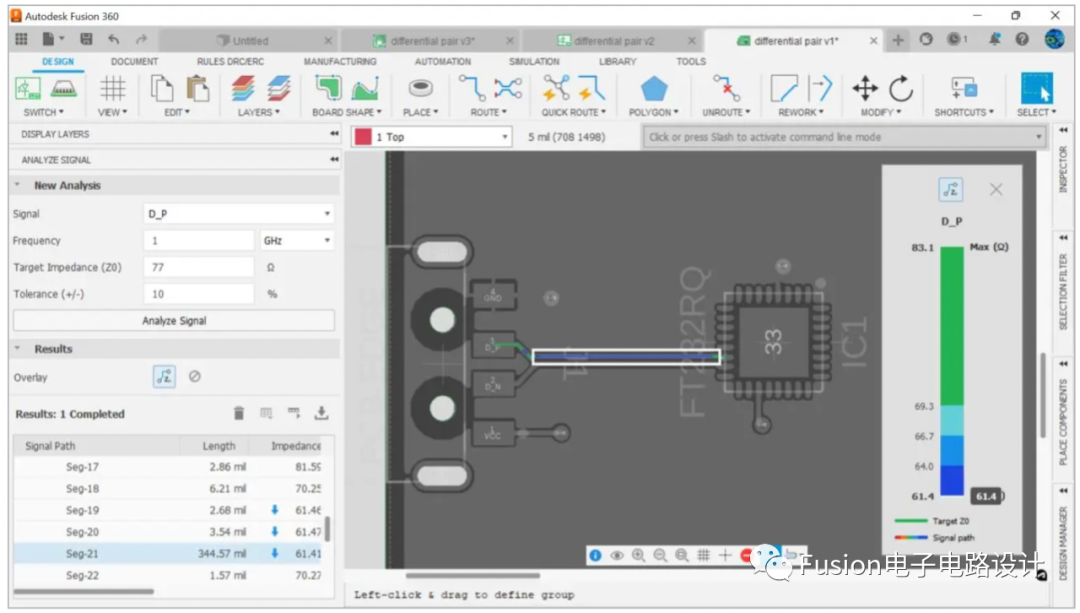

上圖示例里,大多數(shù)跡線的阻抗為70.2Ω。看看如果我們在靠近信號的頂層放置接地敷銅,阻抗會發(fā)生什么變化。線路阻抗幾乎全部為61Ω。

阻抗隨頂部接地敷銅顯著變化。

但是,按照我們的8W規(guī)則,放入80mil 間距,我們得到了之前的阻抗70.2Ω。

將接地敷銅與跡線隔開,使阻抗回到70.2Ω。

8W規(guī)則是保守的數(shù)字,有些使用5W甚至3H,其中H = 接地層和信號層之間的電介質(zhì)高度。通過信號完整性擴(kuò)展程序,F(xiàn)usion 360 Electronics可以向您顯示計算的阻抗值,并幫助您確定擁擠信號線路之間的影響。

9.差分布線的長度不匹配沒有經(jīng)驗法則

到目前為止,我們已經(jīng)多次提到差分信號,因此讓我們更詳細(xì)地了解它們。

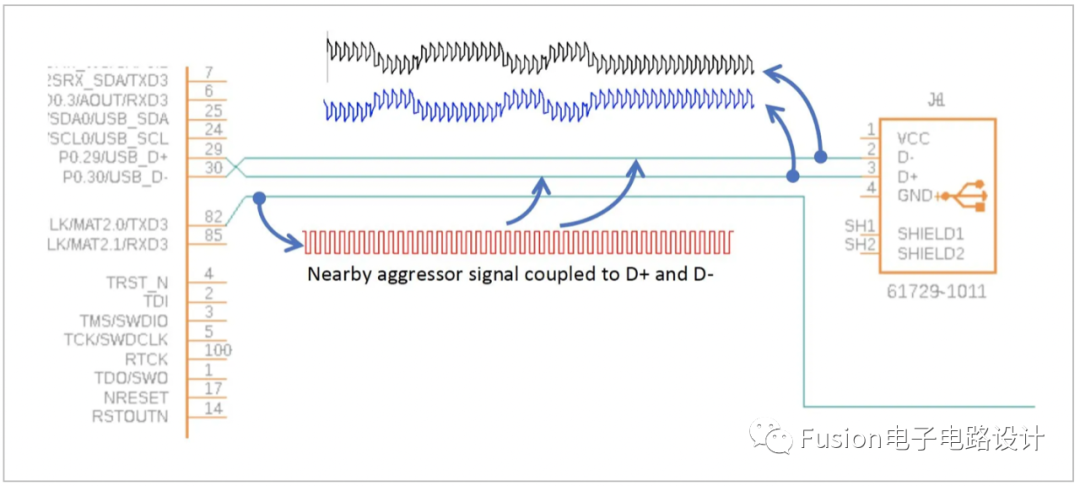

差分信號在HDMI、USB、LVDS等高速通信標(biāo)準(zhǔn)中非常常見。這是因為它們抗噪音。讓我們看看他們?yōu)槭裁茨芫芙^噪音。

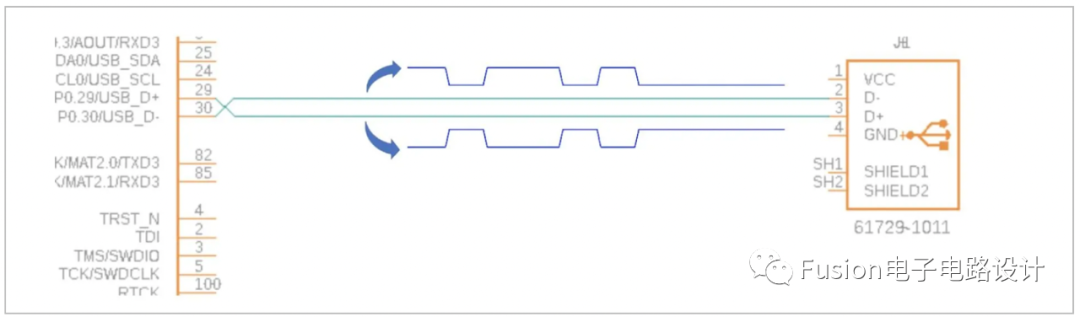

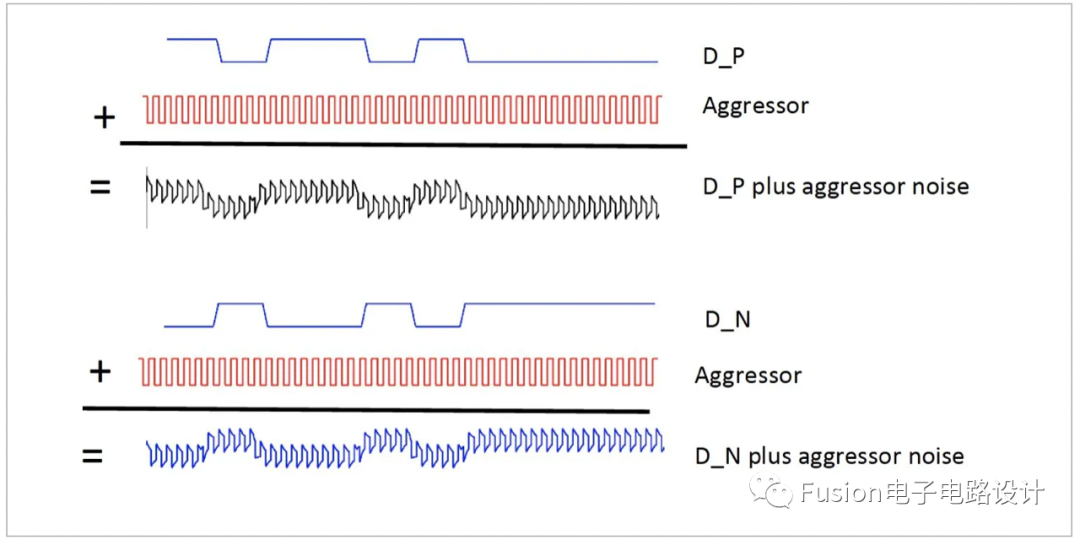

差分信號由兩個信號D+(D_P)和D-(D_N)組成。這對電線上的信號極性相反。

差分信號極性相反。

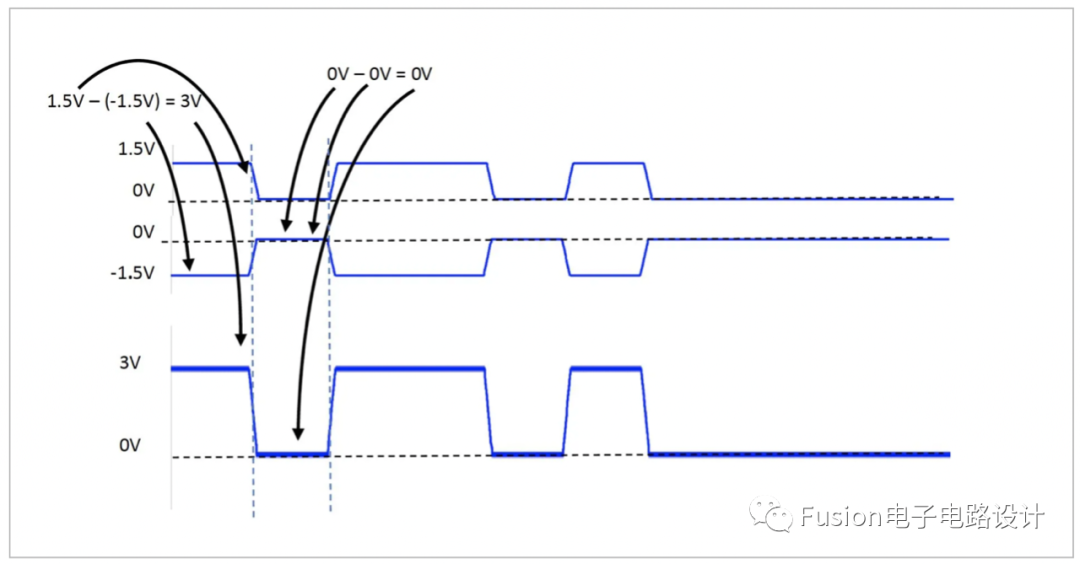

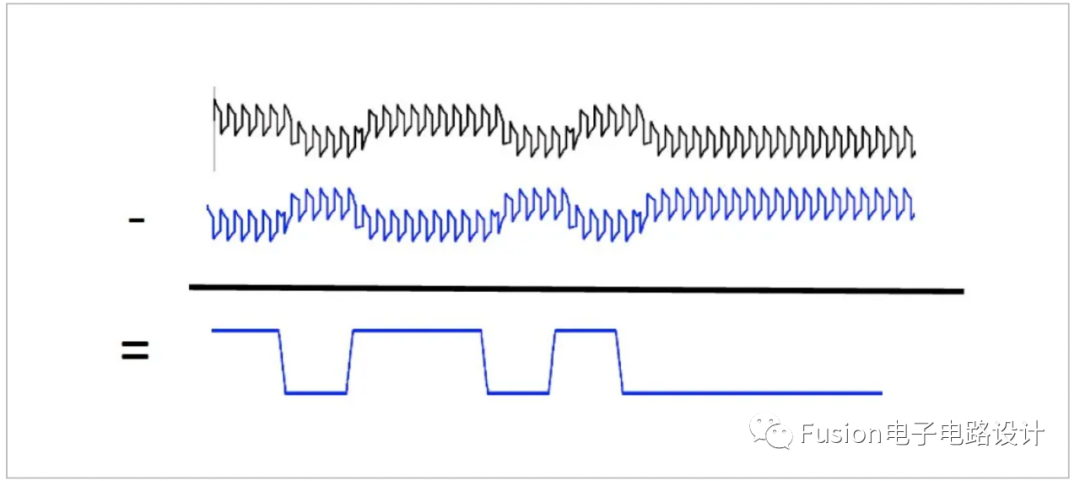

差分信號的接收端從正信號中減去負(fù)信號,得到恢復(fù)信號。

正如我們前面所說的,差分信號的真正優(yōu)點是它們可以抑制噪聲。考慮附近具有不希望的干擾信號的差分信號,該干擾信號將信號耦合到每個差分線。

產(chǎn)生的耦合信號將以相同的極性出現(xiàn)在差分布線的每條跡線上。即:

在接收機(jī)處,兩個噪聲信號彼此相減,我們得到兩個沒有任何干擾噪聲的差分信號。即,

(D_P+Aggressor)–(D_N+Aggressor)=D_P – D_N

而且,從前面我們知道D_P – D_N = 兩倍大的單個信號。從圖形上看,它意味著:

兩種信號的共同噪聲消失了。

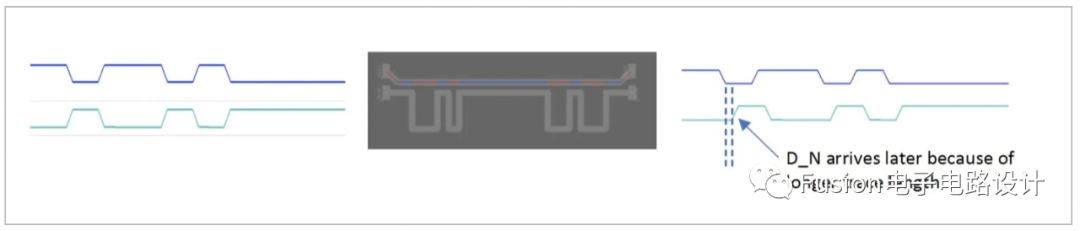

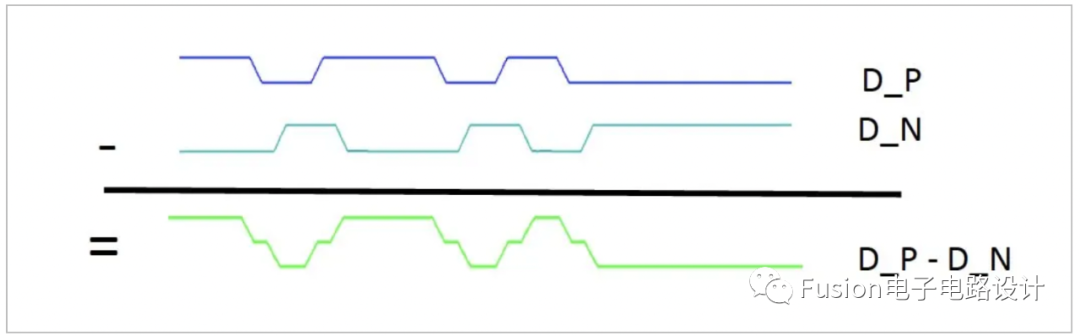

差分信號也對信號對之間的定時差敏感。考慮以下情況,其中一對信號中的一個信號必須傳播更長的距離,因此到達(dá)時間較晚。

從D_P減去D_N后的結(jié)果如下:

也許接收機(jī)能正確解碼D_P–D_N,也許不能。這就引出了我們的下一條經(jīng)驗法則:差分布線的長度不匹配沒有經(jīng)驗法則。

高速信號規(guī)格將確定差分布線的長度最大的不匹配值。遵守技術(shù)規(guī)格說明,不然任何其他情況都可能導(dǎo)致不必要的EMI或EMC問題。

10.了解對內(nèi)和對間延時差 (Understand intra pair and inter pair skew)?

對內(nèi)延時差(Intra-pair skew)是單個差分對的布線路徑之間的時間差。如上所示,不同的時差會干擾信號,使其變得不可用。解決方案是延長較短的差分對。

差分對之間的不同長度。

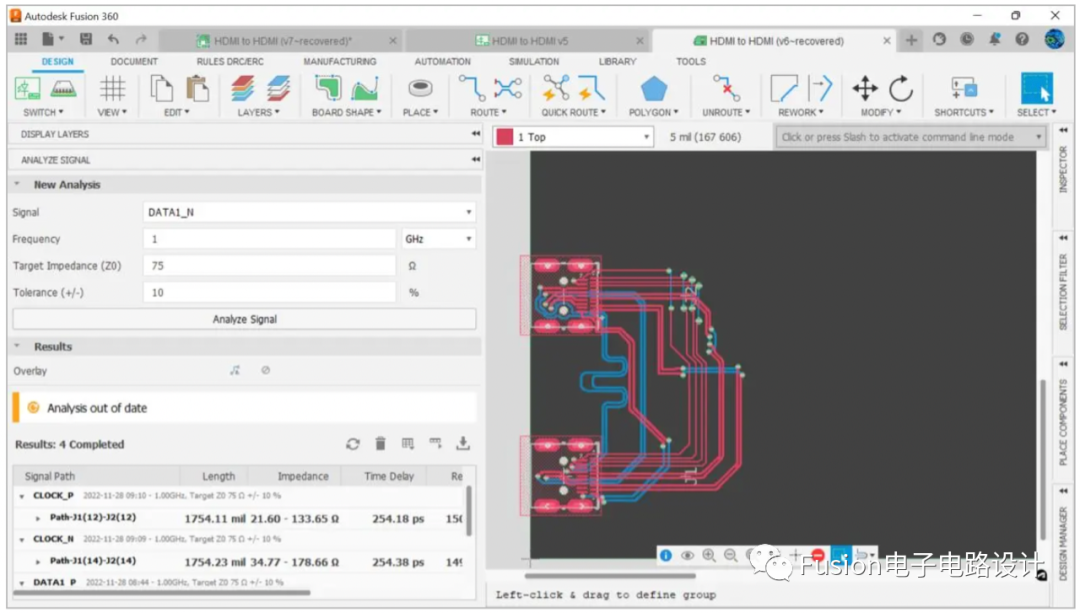

“meander 1800 mil”命令會讓時鐘線延長到1800 mil(數(shù)據(jù)線的長度)。

折彎命令用于延長差分對的線路長。?

請注意,折彎還調(diào)整了時鐘差分對的長度,以最小化對間偏移。

Fusion 360信號完整性擴(kuò)展程序使電路板設(shè)計者能夠模擬跡線的阻抗和傳播延遲。可以看到間距、跡線寬度、信號擁擠和層堆疊對阻抗控制線路的影響。經(jīng)驗法則可以得到驗證,所提供的見解可以用來確定是否需要遵循經(jīng)驗法則。通過Fusion 360信號完整性擴(kuò)展程序,設(shè)計人員可以修改和調(diào)整跡線長度和路徑,提高電路板的信號完整性和設(shè)計質(zhì)量。

準(zhǔn)備好開始高速電路板設(shè)計了嗎?立即免費14天試用Fusion 360信號完整性擴(kuò)展程序吧。?

審核編輯:湯梓紅

-

元器件

+關(guān)注

關(guān)注

112文章

4709瀏覽量

92209 -

電路板

+關(guān)注

關(guān)注

140文章

4951瀏覽量

97689 -

信號完整性

+關(guān)注

關(guān)注

68文章

1404瀏覽量

95458 -

高速電路板

+關(guān)注

關(guān)注

0文章

15瀏覽量

8196 -

高速信號

+關(guān)注

關(guān)注

1文章

225瀏覽量

17694

原文標(biāo)題:高速電路板設(shè)計的十條規(guī)則

文章出處:【微信號:HGL-DXP2004,微信公眾號:DXP設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

88條規(guī)則敲定:PCB電路板測試、檢驗及規(guī)范

**十條PCB元器件擺放小建議**

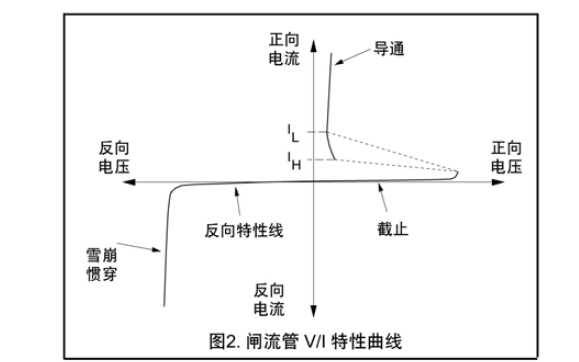

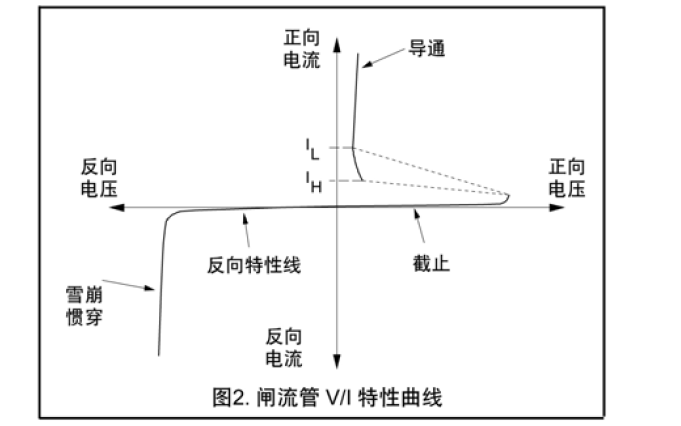

閘流管和雙向可控硅-成功應(yīng)用的十條黃金規(guī)則

十條最有效的PCB設(shè)計黃金法則

閘流管和雙向可控硅-成功應(yīng)用的十條黃金規(guī)則

PLD、FPGA優(yōu)秀設(shè)計的十條戒律

閘流管和雙向可控硅 - 成功應(yīng)用的十條黃金規(guī)則

PCB設(shè)計中元器件布局的10條規(guī)則,布線的規(guī)則是什么?

閘流管和雙向可控硅成功應(yīng)用的十條黃金規(guī)則詳細(xì)說明

閘流管和雙向可控硅成功應(yīng)用的規(guī)則有哪些十條黃金規(guī)則詳細(xì)說明

元器件布局的10條規(guī)則

高速電路板設(shè)計的十條規(guī)則

高速電路板設(shè)計的十條規(guī)則

評論