在IEDM 2023上,英特爾展示了結合背面供電和直接背面觸點的3D堆疊CMOS晶體管,這些開創性的技術進展將繼續推進摩爾定律。

2023年12月9日,英特爾在IEDM 2023(2023 IEEE國際電子器件會議)上展示了多項技術突破,為其未來的制程路線圖提供了豐富的創新技術儲備,充分說明了摩爾定律仍在不斷演進。具體而言,英特爾研究人員在大會上展示了結合背面供電和直接背面觸點(direct backside contacts)的3D堆疊CMOS晶體管,分享了近期背面供電研發突破的擴展路徑(如背面觸點),并率先在同一塊300毫米晶圓上,而非封裝中,成功實現了硅晶體管與氮化鎵(GaN)晶體管的大規模單片3D集成。

英特爾公司高級副總裁兼組件研究總經理Sanjay Natarajan表示:“我們正在進入制程技術的埃米時代,展望‘四年五個制程節點’計劃實現后的未來,持續創新比以往任何時候都更加重要。在IEDM 2023上,英特爾展示了繼續推進摩爾定律的研究進展,這顯示了我們有能力面向下一代移動計算需求,開發實現晶體管進一步微縮和高能效比供電的前沿技術。”

晶體管微縮和背面供電是滿足世界對更強大算力指數級增長需求的關鍵。一直以來,英特爾始終致力于滿足算力需求,表明其技術創新將繼續推動半導體行業發展,也仍然是摩爾定律的“基石”。英特爾組件研究團隊不斷拓展工程技術的邊界,包括晶體管堆疊,背面供電技術的提升(有助于晶體管的進一步微縮和性能提升),以及將不同材料制成的晶體管集成在同一晶圓上。

英特爾近期在制程技術路線圖上的諸多進展,包括PowerVia背面供電技術、用于先進封裝的玻璃基板和FoverosDirect,彰顯了英特爾正在通過技術創新不斷微縮晶體管。這些創新技術均源自英特爾組件研究團隊,預計將在2030年前投產。

在IEDM 2023上,英特爾組件研究團隊同樣展示了其在技術創新上的持續投入,以在實現性能提升的同時,在硅上集成更多晶體管。研究人員確定了所需的關鍵研發領域,旨在通過高效堆疊晶體管繼續實現微縮。結合背面供電和背面觸點,這些技術將意味著晶體管架構技術的重大進步。隨著背面供電技術的完善和新型2D通道材料的采用,英特爾正致力于繼續推進摩爾定律,在2030年前實現在單個封裝內集成一萬億個晶體管。

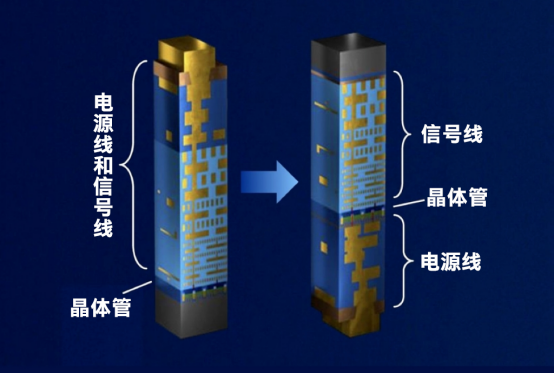

英特爾實現了業界領先的、突破性的3D堆疊CMOS晶體管,結合了背面供電和背面觸點技術:

?英特爾在IEDM 2023上展示了業界領先的最新晶體管研究成果,能夠以微縮至60納米的柵極間距垂直地堆疊互補場效應晶體管(CFET)。該技術可通過晶體管堆疊提升面積效率(area efficiency)和性能優勢,還結合了背面供電和直接背面觸點。該技術彰顯了英特爾在GAA(全環繞柵極)晶體管領域的領先地位,展示了英特爾在RibbonFET之外的創新能力,從而能夠領先競爭。

超越其“四年五個制程節點”計劃,以背面供電技術繼續微縮晶體管,英特爾確定了所需的關鍵研發領域:

?英特爾的PowerVia將于2024年生產準備就緒,率先實現背面供電。英特爾組件研究團隊在IEDM 2023上發表的研究明確了超越PowerVia,進一步拓展背面供電技術的路徑,及所需的關鍵工藝進展。此外,該研究還強調了對背面觸點和其它新型垂直互聯技術的采用,從而以較高的面積效率堆疊器件。

英特爾率先在同一塊300毫米晶圓上成功集成硅晶體管和氮化鎵晶體管,且性能良好:

?在IEDM 2022上,英特爾聚焦于性能提升,以及為實現300毫米硅基氮化鎵(GaN-on-silicon)晶圓開辟一條可行的路徑。今年,英特爾在硅和氮化鎵的工藝集成方面取得了進展,成功實現了一種高性能、大規模的集成電路供電解決方案,名為“DrGaN”。英特爾的研究人員率先在這一技術領域實現了良好的性能,有望讓供電解決方案滿足未來計算對功率密度和能效的需求。

英特爾推進2D晶體管領域的研發工作,以使其在未來繼續按照摩爾定律的節奏微縮下去:

?過渡金屬二硫屬化物(TMD, Transition metal dichalcogenide)2D通道材料讓晶體管物理柵極長度有機會微縮到10納米以下。在IEDM 2023上,英特爾將展示高遷移率(high-mobility)的過渡金屬二硫屬化物晶體管原型,用于NMOS(n型金屬氧化物半導體)和PMOS(p型金屬氧化物半導體)這兩大CMOS關鍵組件。此外,英特爾還將展示其率先實現的兩項技術:GAA2D過渡金屬二硫屬化物PMOS晶體管和在300毫米晶圓上制造的2D PMOS晶體管。

審核編輯:湯梓紅

-

英特爾

+關注

關注

61文章

9949瀏覽量

171692 -

半導體

+關注

關注

334文章

27286瀏覽量

218076 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080

發布評論請先 登錄

相關推薦

英特爾Intel 18A制程芯片2025年量產計劃公布

英特爾向聯想交付首款18A工藝CPU樣品

英特爾基于Intel 18A制程節點處理器樣片成功出廠

英特爾是如何實現玻璃基板的?

英特爾開啟新時代:Intel 3制程節點引領性能與能效飛躍

英特爾加大玻璃基板技術布局力度

英特爾推進面向未來節點的技術創新,在2025年后鞏固制程領先性

英特爾展示下一代至強處理器,助力vRAN性能顯著提升

英特爾展示下一代晶體管微縮技術突破,將用于未來制程節點

英特爾展示下一代晶體管微縮技術突破,將用于未來制程節點

評論