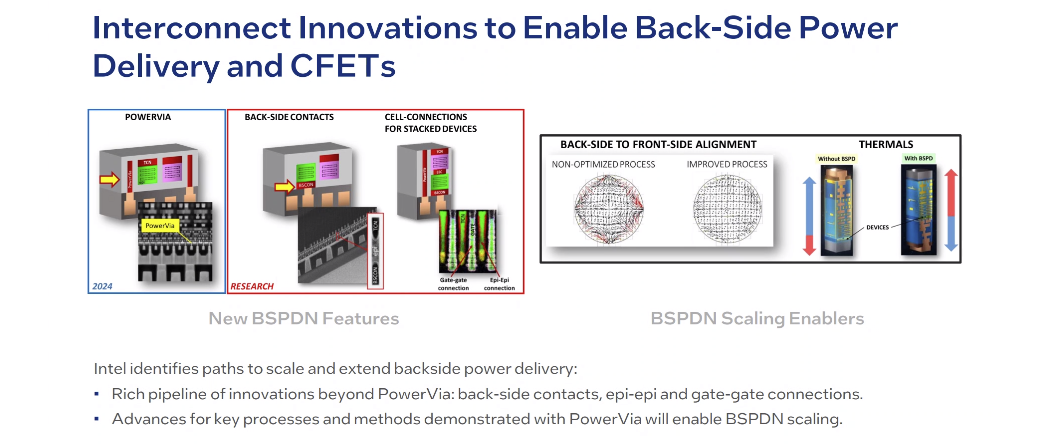

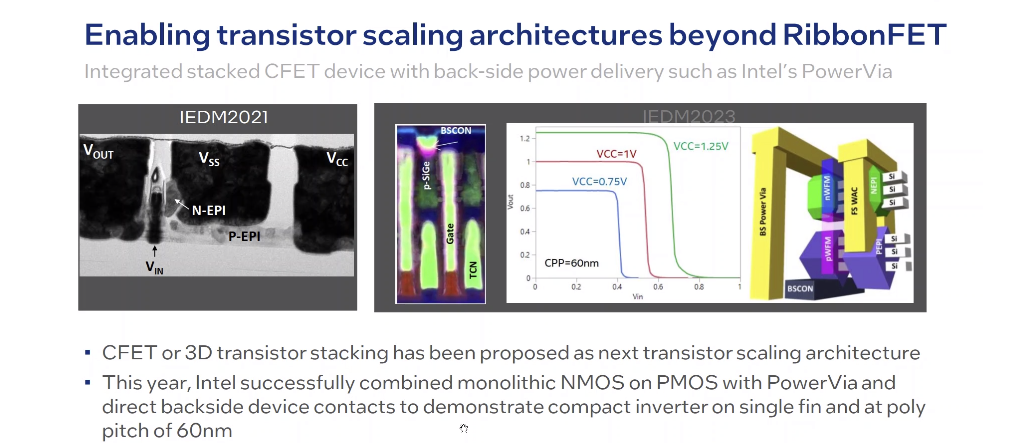

英特爾在2023年國際電子設備制造大會上宣布,他們已經成功完成了一項名為PowerVia的背面供電技術的開發。這個技術是基于英特爾的最新晶體管研究成果,它實現了互補金屬氧化物半導體場效應晶體管(CFET)的60納米柵極間距垂直堆疊。通過堆疊晶體管,該技術提高了面積效率和性能,同時還結合了背面供電和直接背面接觸這兩種技術。

英特爾解釋說,過去幾年芯片制造都是層層疊加的,從最小的元件-晶體管開始制造,之后需要創建更小的線路層,用于連接晶體管和金屬層。這些線路被稱為信號互連線,其中還包括用于給晶體管供電的電源線等。但是隨著晶體管逐漸變小、密度日益提高,互連線和電源線共享的線路層變得越來越混亂。面對這個問題,英特爾開始尋找將電源線遷移到芯片背面的背面供電技術。

英特爾的背面供電解決方案PowerVia已經產生了具有競爭力的測試結果。這項技術解決了傳統"披薩式"制造方法帶來的問題,尤其是電源線和互連線的分離以及線徑的擴大,從而改進了供電和信號的傳輸。

對于英特爾的晶體管堆疊和背面供電的技術,研究表明,它將在微縮晶體管的密度上發揮重要作用。英特爾強調,這將超越其"四年五個制程節點計劃",以背面供電技術繼續微縮晶體管。

目前,英特爾的這項技術在競爭對手中具有一定的優勢。比如臺積電將在2025年量產的第一代2納米制程時引入全環繞柵極(GAA)架構,然后在2026年的第二代2納米制程中引入背面供電技術。與此同時,盡管韓國三星在2022年量產的3納米制程技術上已經引入了GAA架構,但是他們預計要到2025年量產的2納米制程才會引入背面供電技術。從這個角度來看,英特爾確實領先了一步。

-

芯片

+關注

關注

455文章

50714瀏覽量

423158 -

英特爾

+關注

關注

61文章

9949瀏覽量

171694 -

晶體管

+關注

關注

77文章

9682瀏覽量

138083 -

三星

+關注

關注

1文章

1521瀏覽量

31208

發布評論請先 登錄

相關推薦

世紀大并購!傳高通有意整體收購英特爾,英特爾最新回應

英特爾CEO Gelsinger宣布退休

英特爾宣布擴容成都封裝測試基地

英特爾至強品牌新戰略發布

英特爾是如何實現玻璃基板的?

英特爾CEO:AI時代英特爾動力不減

英特爾加大玻璃基板技術布局力度

英特爾推進面向未來節點的技術創新,在2025年后鞏固制程領先性

英特爾宣布代工虧損70億美元

浪潮信息與英特爾合作推出一種大模型效率工具“YuanChat”

英特爾宣布完成PowerVia背面供電技術的開發

英特爾宣布完成PowerVia背面供電技術的開發

評論