今天我們就為大家分享——在電源設計過程中,如何恰當選擇上下 MOS 管的比例來提高電源的工作效率。

MOS 選擇的困惑

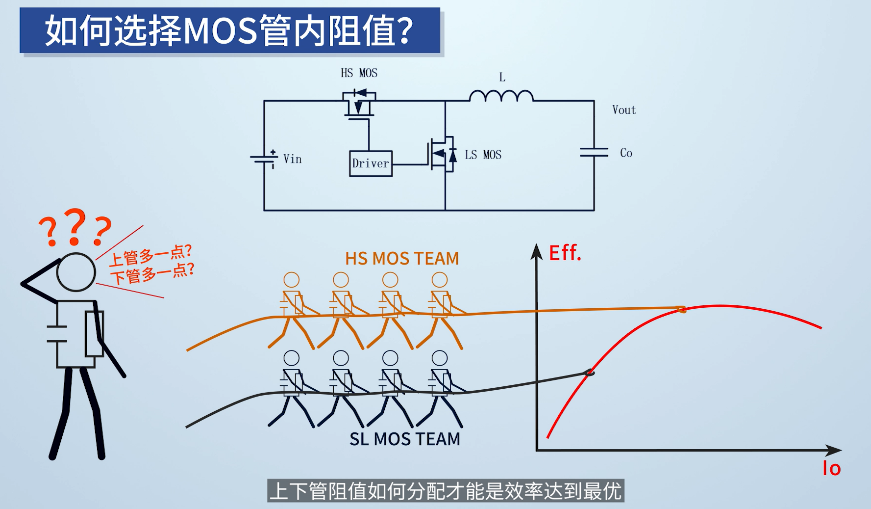

如何選擇合適的 MOS 管內阻值一直是電源工程師困擾的問題。

內阻選多少才好?

上下管阻值如何分配才能是效率達到最優?

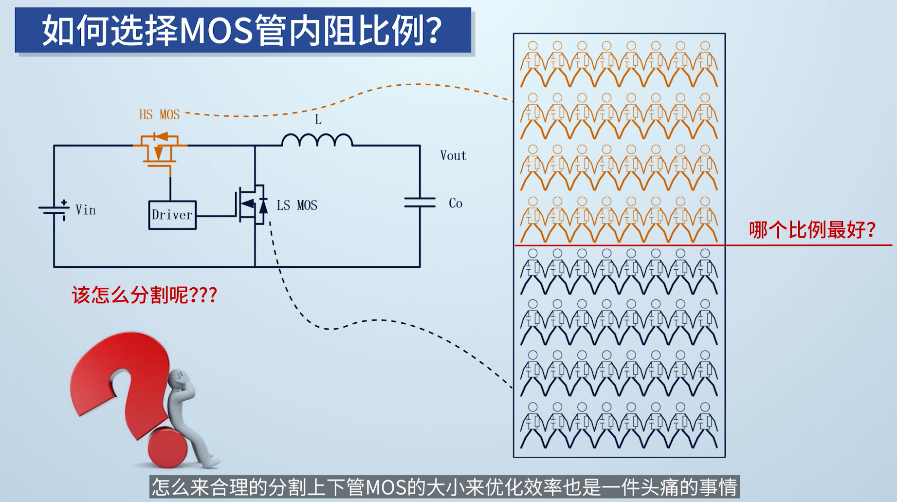

在芯片的設計中,MOS 管內阻的分配也是非常重要的。往往能給 MOS 管的空間就這么大,怎么來合理地分割上下管 MOS 的大小,來優化效率也是一件頭痛的事情。

MOS 的結構和損耗組成

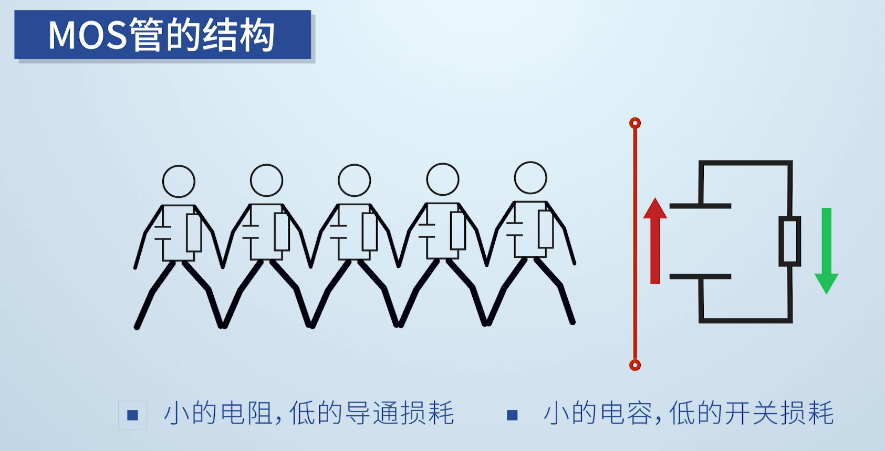

首先讓我們來了解一下 MOS 管的結構。

MOS 管是個多元集成結構,即一個器件由多個MOSFET單元并聯組成。MOS 管導通時表現為電阻特性,且存在三個寄生電容。所以我們可以把 MOS 單元理解為電容和電阻的并聯體。MOS 晶元體并聯數量越多,導通電阻值就會變得越小,但寄生電容卻會變得越大。小的導通電阻帶來低的導通損耗,但會讓寄生電容變得更大,從而增加開關損耗。

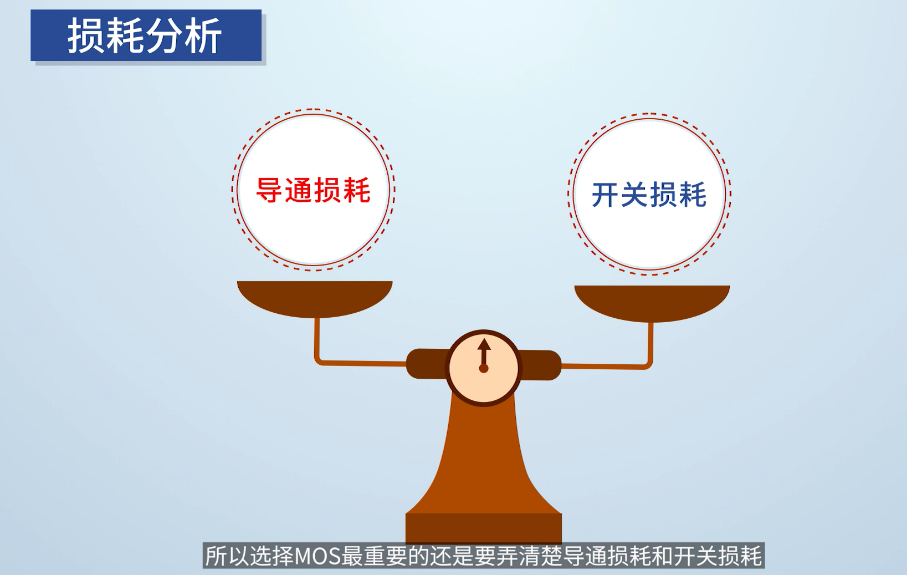

所以選擇 MOS 最重要的還是要弄清楚導通損耗和開關損耗,找到一個最佳平衡點。

怎么找呢?

板上測試,雖然準確,但需要非常大的工作量,并不現實。

建立精確的數學模型來分析損耗是一個簡單又快捷的方法。

1.導通損耗

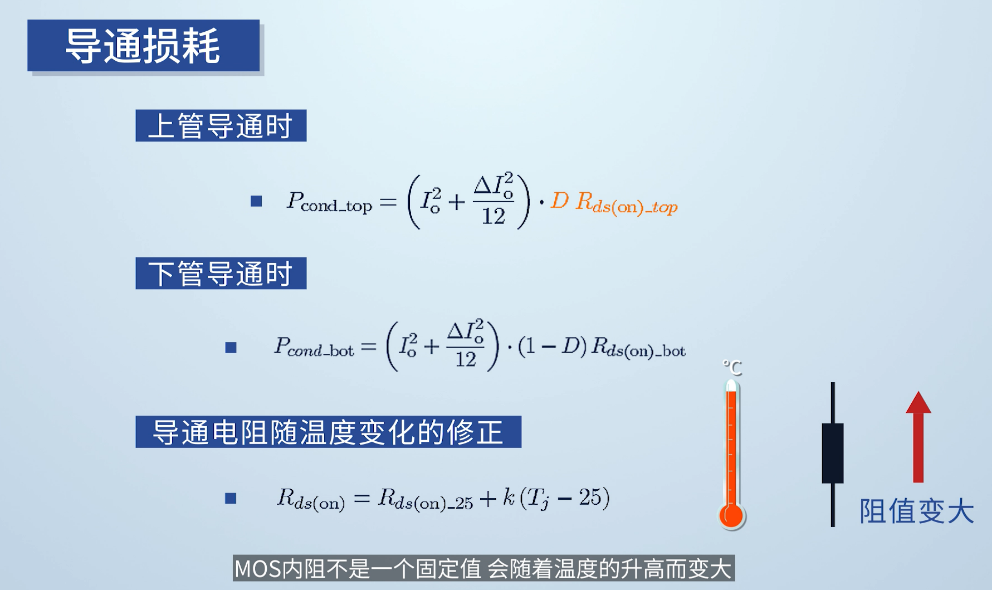

首先,我們計算導通損耗,導通損耗的計算相對簡單,流過 MOS 的電流并考慮紋波電流就可算出單周期上的導通損耗。為了模型的準確性,必須要考慮導通內阻與溫度之間的修正關系。MOS 內阻不是一個固定值,會隨著溫度的升高而變大。找元器件現貨上唯樣商城

2.開關損耗中的寄生參數

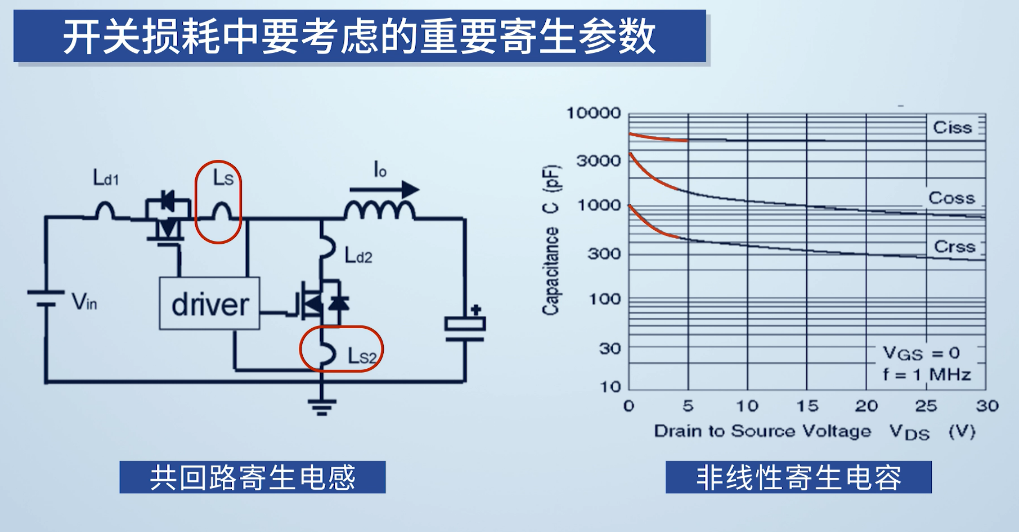

開關損耗的計算相對復雜,為了得到準確的開關損耗模型,必須考慮下面的兩點因素:

一個是驅動與主回路共享的寄生電感;

一個是 MOS 寄生電容在不同 DS 電壓下的非線性容值。

3.開關損耗中的開通損耗

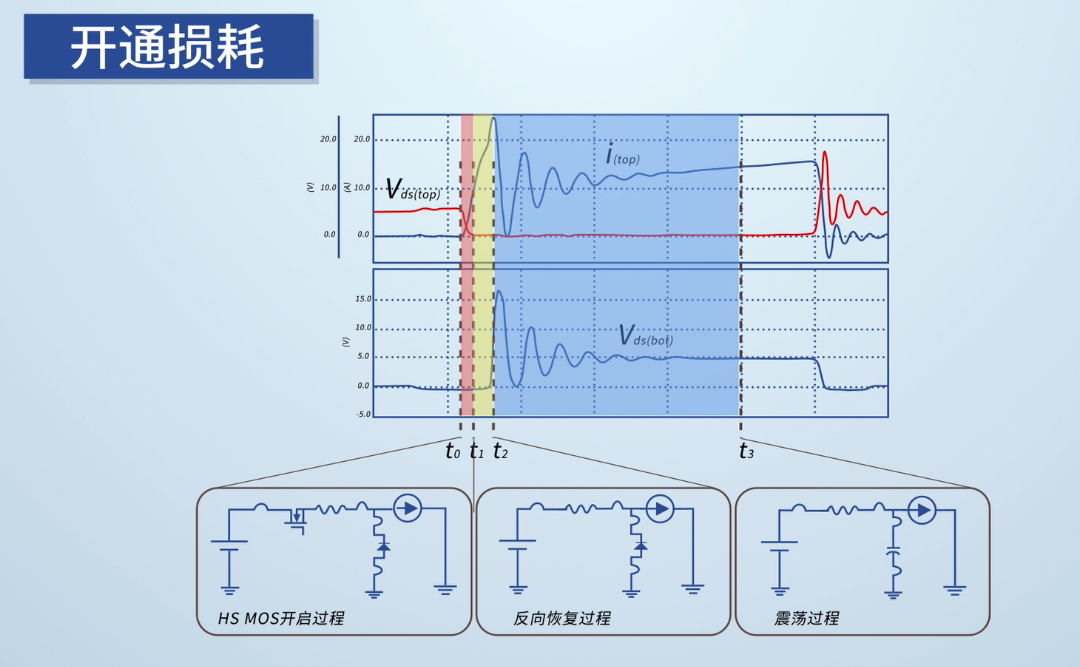

開通損耗分為三個階段:

第一階段,上管 MOS 開啟過程,上管的 DS 電壓開始下降,DS 電流開始上升的過程,直到上管 Vds(top) 電壓降到0或上管 Itop 電流上升到輸出電流 Io 值為止結束;

第二階段,反向恢復過程,這個階段到 Itop 到達峰值點結束,之后下管開始建立電壓;

第三階段,震蕩過程,直到上管 Itop 電流不再波動時結束。

4.開關損耗中的關斷損耗

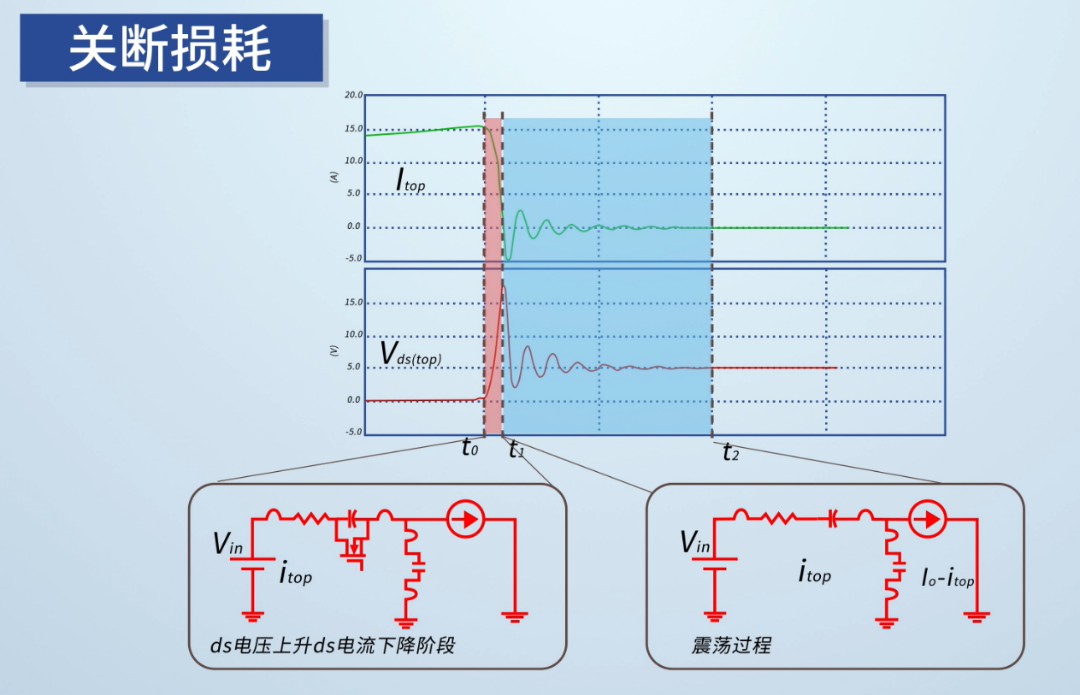

關斷損耗分為兩個階段:

第一階段,Vds 電壓上升和 Ids 電流下降階段,直到 Ids 電流降到0時該階段結束;

第二階段,震蕩過程,直到 Vds 電壓不再震蕩為止。

數學模型和分析驗證

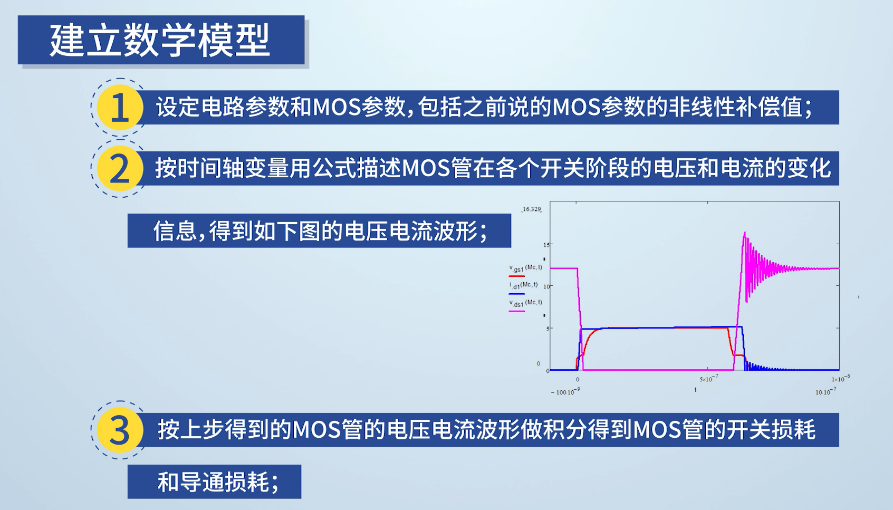

了解清楚了電路工作過程的各個損耗后,我們就可以建立數學模型了。首先設定所需的電路參數值和上面分析的 MOS 管參數值及其非線性參數補償值;然后按時間軸變化描述出各個開關階段的電壓電流波形;再對電壓電流波形做積分就可得到 MOS 管的開關損耗和導通損耗。

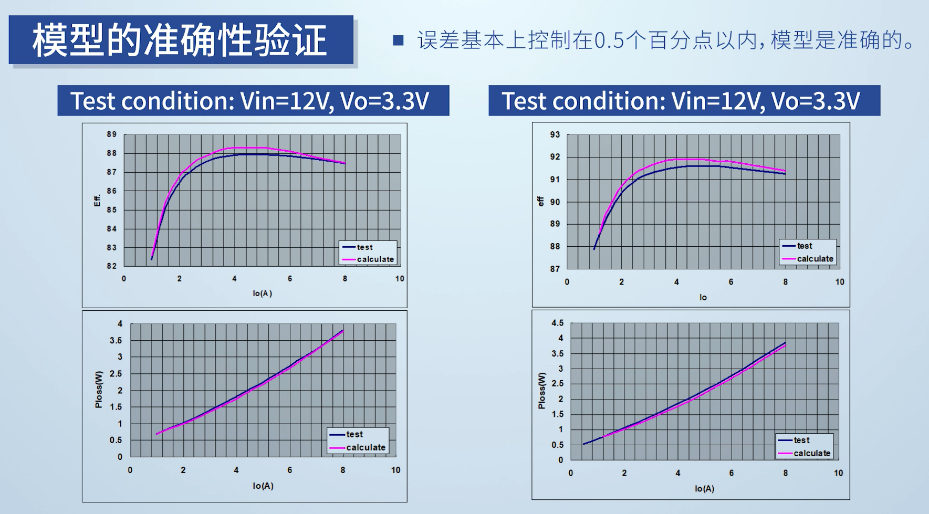

模型有了,我們接下來驗證一下模型的準確性,將板子上實際測得的效率曲線和模型的計算結果做對比。計算和測試的效率誤差基本上控制在0.5個百分點以內。模型是準確的。

基于數學模型工具的MOS選擇

在 MOS 的設計上可以放飛自我了。

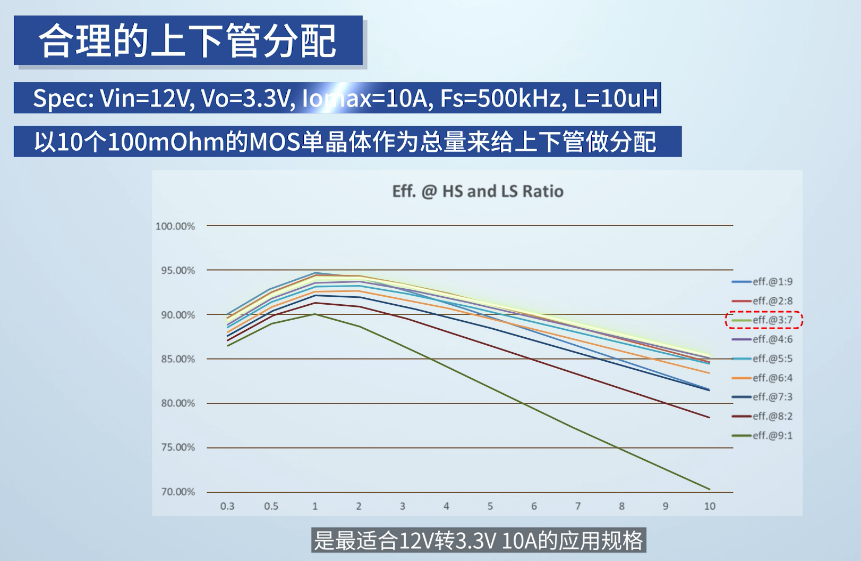

我們以10個 100m?內阻的 MOS 單晶元為整體,用模型來計算不同配比下的效率曲線,右邊的比例代表單晶元的數量比例。通過曲線的對比,我們可以很直觀的得出3:7的 MOS 管配比是最適合12V轉3.3V,10A 的應用規格。從這個效率曲線簇中我們也可以發現,同樣單位數量的 MOS,不同的比例分配會得到不同的效率曲線,找到這個最優配比,讓你的效率曲線最優化。

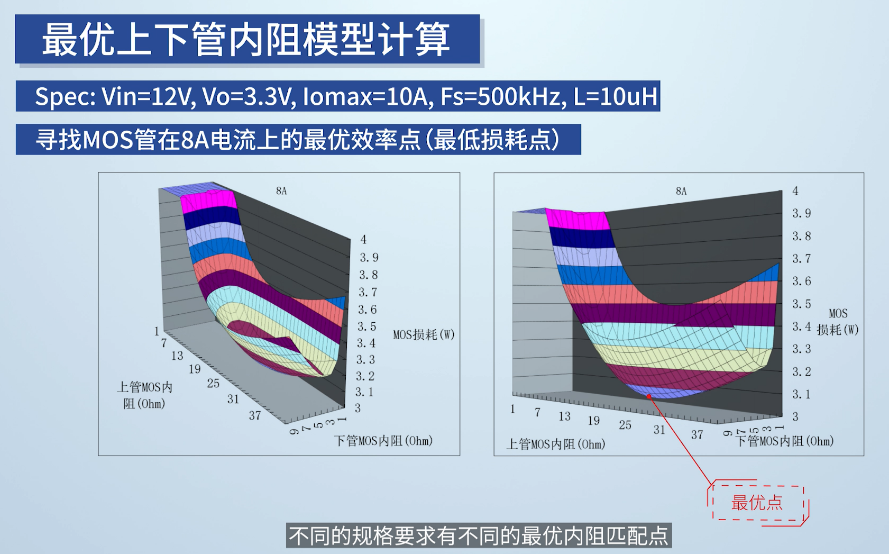

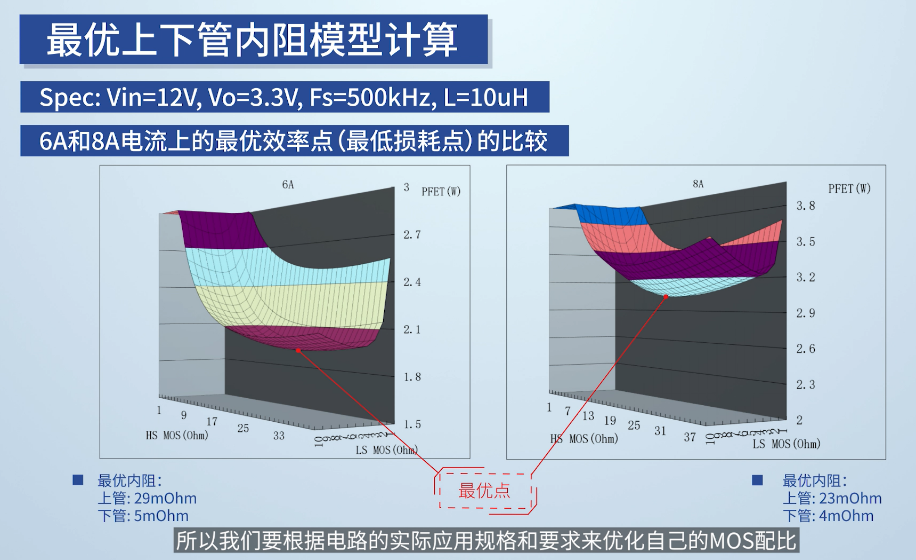

通過模型,我們還可以找到 MOS 管的最優內阻值。我們不限定 MOS 管的并聯個數,直接按內阻從小到大來計算后可得到損耗關于上下管內阻的三維立體圖,損耗的最低點也就是我們效率的最高點。從圖中可以看出,MOS 管的內阻并不是越小越好,不同的規格要求有不同的最優內阻匹配點。

我們再做個橫向比較,同樣的輸入輸出規格,不同的輸出電流點,最優的配比也是不一樣的。所以我們要根據電路的實際應用規格和要求來優化自己的 MOS 配比。

總結

MOS 的選擇對于電路效率的優化非常重要。

精準的數學模型可以讓 MOS 管的選擇設計變的簡單。為了得到準確的模型,必須考慮電路的這三個非線性寄生參數。

審核編輯 黃宇

-

電源

+關注

關注

184文章

17706瀏覽量

250002 -

MOS

+關注

關注

32文章

1269瀏覽量

93703

發布評論請先 登錄

相關推薦

關羽Labview中三維曲線坐標軸比例的問題

優美的系統是什么

【解密】如何讓電池充放電測試變得更加簡單

如何讓電池充放電測試變得更加簡單

請問怎么為gm vs vg曲線選擇合適的柵極電壓?

曲線追蹤儀與I-V曲線追蹤儀軟件

Chapyter讓編碼更加地高效

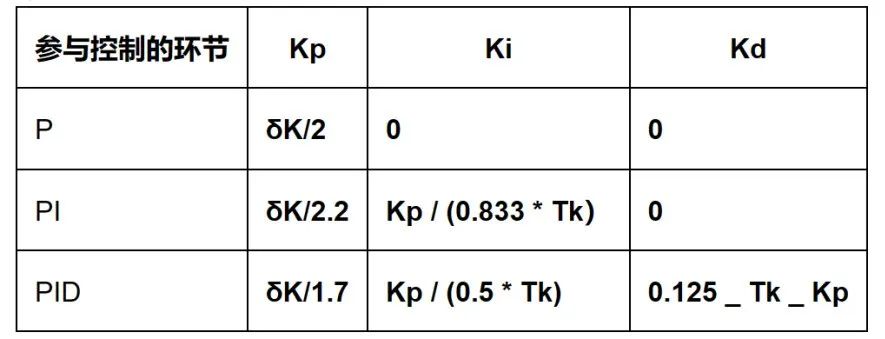

PID臨界比例法和一般調節法介紹

電源管理芯片效率測試曲線的繪制與分析:電子設備性能優化關鍵

合適的比例,讓效率曲線更加優美

合適的比例,讓效率曲線更加優美

評論