歡迎了解

邵滋人,李太龍,湯茂友

摘要:

在存儲(chǔ)技術(shù)發(fā)展過(guò)程中,三維閃存存儲(chǔ)器以其單位面積內(nèi)存儲(chǔ)容量大、改寫(xiě)速度快等優(yōu)點(diǎn),正逐步取代機(jī)械硬盤(pán)成為大數(shù)據(jù)存儲(chǔ)領(lǐng)域中的主角。但是目前市面上的 Nand Flash 產(chǎn)品封裝還是多以傳統(tǒng)金屬線鍵合技術(shù)為主,這類傳統(tǒng)方案會(huì)在一些特殊應(yīng)用和需求下存在較難進(jìn)一步降低封裝體的尺寸、傳輸速度受限等問(wèn)題。為了應(yīng)對(duì)產(chǎn)品尺寸持續(xù)向小、速度和帶寬需求持續(xù)增大的趨勢(shì),三維閃存封裝也需要更多的形式,可以結(jié)合當(dāng)前涌現(xiàn)出的多種先進(jìn)封裝形式尋找新的解決方案。本文通過(guò)分析 SiP、Fan-out、3D 和 Chiplet 等先進(jìn)封裝形式,探討在三維閃存封裝中的可能應(yīng)用方案,利用重新布線層(RDL)代替基板、TSV,Bumping 代替金線的連接等技術(shù),有效縮小封裝體面積同時(shí),提升產(chǎn)品的運(yùn)行速度,增強(qiáng)數(shù)據(jù)處理能力。

0 引言

近年來(lái),隨著人工智能、物聯(lián)網(wǎng)和 5G 等技術(shù)的蓬勃發(fā)展和應(yīng)用,市場(chǎng)對(duì)數(shù)據(jù)處理以及存儲(chǔ)的需求逐漸增大。根據(jù) IDC 預(yù)測(cè),全球數(shù)據(jù)圈每年被創(chuàng)建、采集或復(fù)制的數(shù)據(jù)量,由 2018 年的 32 ZB 到 2025年將增至 175 ZB。半導(dǎo)體存儲(chǔ)具有存取速度快、功耗低、體積小、可靠性高等優(yōu)勢(shì),廣泛應(yīng)用在電子設(shè)備中,并且正逐步取代機(jī)械硬盤(pán)成為主流存儲(chǔ)器。其中閃存不同于 DRAM,因其具有斷電數(shù)據(jù)不丟失的優(yōu)點(diǎn),多用于“數(shù)據(jù)倉(cāng)庫(kù)”來(lái)使用。其技術(shù)的發(fā)展也是朝著不斷增大單位面積存儲(chǔ)容量的方向發(fā)展,由二維到三維,再到不斷地增加堆棧層數(shù),當(dāng)前業(yè)界已經(jīng)推出 200 層以上堆棧的產(chǎn)品,未來(lái)還會(huì)向 1000 層發(fā)展。閃存因其采用電荷隧穿的方式實(shí)現(xiàn)存儲(chǔ)功能,相比 DRAM 的電容方式,存儲(chǔ)速度上大打折扣,封裝方式上也以傳統(tǒng)的封裝形式為主,目前市面上采用先進(jìn)封裝工藝來(lái)實(shí)現(xiàn)其存儲(chǔ)功能的產(chǎn)品非常少。隨著數(shù)據(jù)時(shí)代的發(fā)展,各領(lǐng)域 AI 應(yīng)用對(duì)數(shù)據(jù)傳輸及處理的多樣性需求逐步增多,同時(shí)伴隨摩爾定律的放緩和各類先進(jìn)封裝技術(shù)的涌現(xiàn),持續(xù)探索新的封裝形式,將處理器、DRAM、閃存采用新的形式結(jié)合起來(lái),提升總體運(yùn)算能力,將會(huì)影響未來(lái)三維閃存封裝發(fā)展方向。

1 三維閃存及當(dāng)前主要封裝形式簡(jiǎn)介

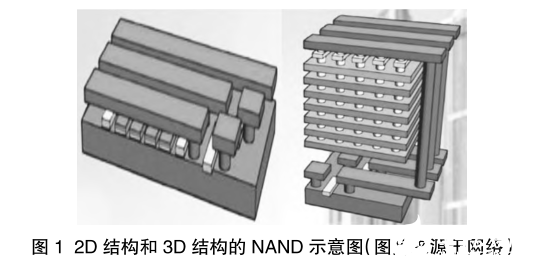

東芝公司于 1989 年開(kāi)發(fā)了 NAND Flash 的結(jié)構(gòu),主要目的是降低每比特的成本,獲得高性能,并且可以通過(guò)接口輕松升級(jí)。最初 2D 結(jié)構(gòu)的存儲(chǔ)單元僅僅是布置在平面中,因此想要提高單位存儲(chǔ)密度,唯一方法就是微縮晶體管,不斷減小制程工藝的節(jié)點(diǎn)。但是對(duì)于 NAND Flash 器件,減小晶體管會(huì)帶來(lái)電荷存儲(chǔ)空間不足、電荷串?dāng)_等問(wèn)題。在不增大芯片面積的情況下,為了提高存儲(chǔ)密度,NAND Flash廠商紛紛推出 3D 堆疊技術(shù),將存儲(chǔ)單元沿垂直方向進(jìn)行堆疊,從而提高單位面積的存儲(chǔ)量,如下示意圖 1 所示。目前,NAND Flash 的主要代表公司有三星、鎧俠、西數(shù)、海力士、美光,英特爾和國(guó)內(nèi)的長(zhǎng)江存儲(chǔ)等。

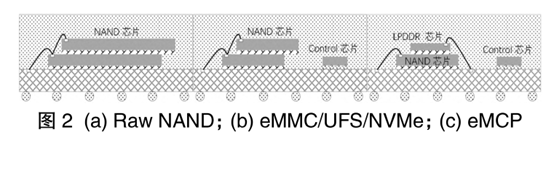

從封裝角度來(lái)看,BGA 形式是實(shí)現(xiàn)大容量存儲(chǔ)的主要方案,且主要有 3 種,即封裝體內(nèi)只含有NAND 芯片的 Raw NAND,增加控制芯片的 Managed NAND(eMMC/UFS/NVMe),和增加主控芯片以及LPDDR 芯片的 eMCP,如圖 2 所示。內(nèi)部實(shí)現(xiàn)電連接主要采用 Wire Bonding 形式,對(duì)部分高端 Managed NAND 產(chǎn)品中的控制芯片會(huì)采用 Flip Chip 形式(圖示為 Flip Chip)。

由于 3D NAND 產(chǎn)品目前主要應(yīng)用在存儲(chǔ)卡、閃存盤(pán)和固態(tài)硬盤(pán)等,以 Wire Bonding 為主的傳統(tǒng)封裝方案可以滿足對(duì)高密度數(shù)據(jù)存儲(chǔ)的需求。未來(lái),隨著物聯(lián)網(wǎng)(IoT)、人工智能、自動(dòng)駕駛和其他數(shù)據(jù)密集型應(yīng)用的不斷發(fā)展,對(duì)數(shù)據(jù)的存儲(chǔ)和讀寫(xiě)速度的要求將變得更具挑戰(zhàn)性,因此有必要思考更多封裝形式及技術(shù),來(lái)解決相應(yīng)的需求。

2 先進(jìn)封裝技術(shù)及其在三維閃存中的可能應(yīng)用

隨著半導(dǎo)體行業(yè)進(jìn)入后摩爾時(shí)代,在成本和性能要求的綜合驅(qū)動(dòng)下,涌現(xiàn)出各種先進(jìn)封裝形式,并已成為行業(yè)未來(lái)發(fā)展的趨勢(shì)之一。當(dāng)前主要的先進(jìn)封裝形式有 SiP (System in a Package)、Fan in/out、2.5D/3D、Chiplet 等,相關(guān)的技術(shù)有凸塊(Bumping)、RDL(Redistribution Layer)、TSV(Through Silicon Via)等技術(shù)。此類封裝技術(shù)的特點(diǎn)是:封裝內(nèi)部連接擺脫傳統(tǒng)的焊線方式,基板被部分或全部取代,使用凸塊及直接鍵合等方式實(shí)現(xiàn)連接,從而在提高集成度、降低封裝尺寸的同時(shí),縮短電流傳導(dǎo)路徑、減少能耗、降低成本,滿足性能需求。

2.1 先進(jìn)封裝技術(shù)及其在三維閃存產(chǎn)品封裝中可能的應(yīng)用

2.1.1Bumping & RDL

Bumping 和 RDL(Redistribution Layer)的工藝在流程上大體一致,都包含噴涂、曝光、顯影、濺射、電鍍和刻蝕等主要的工藝過(guò)程,Bumping 工藝最后流程需要經(jīng)過(guò)回流焊形成凸塊,實(shí)現(xiàn)與外界的電性能連接,而 RDL 的最外層線路也需要 Bumping 工藝,實(shí)現(xiàn)內(nèi)外的線路的導(dǎo)通。

RDL 也稱重新布線層,由金屬層和介質(zhì)層組成,其工藝是在載體或者晶圓的表面沉積金屬層和相應(yīng)保護(hù)的介質(zhì)層形成金屬布線,對(duì) I/O 的端口進(jìn)行重新布局,可以根據(jù)產(chǎn)品的需求相應(yīng)地增加端口的數(shù)量及布局的位置,形成面排布的過(guò)程。目前,RDL 技術(shù)主要應(yīng)用在晶圓級(jí)封裝、2.5D/3D 和 Chiplet封裝等,不僅完美地解決了高密度集成芯片的 I/O間距受限的問(wèn)題,同時(shí)也利用 RDL 取代基板實(shí)現(xiàn)芯片與外界的電性連接,以此降低封裝體的體積。

2.1.2TSV

TSV(Through Silicon Via)技術(shù)是一種穿透硅的通孔技術(shù),簡(jiǎn)稱硅通孔技術(shù)。該技術(shù)利用硅通孔結(jié)構(gòu),使芯片與芯片之間、芯片與基板之間實(shí)現(xiàn)垂直連接,從而有效縮短傳導(dǎo)線路,降低功耗,提高芯片的運(yùn)行速度。應(yīng)用在存儲(chǔ)芯片時(shí),可以通過(guò)增加芯片堆疊數(shù)量,實(shí)現(xiàn)高帶寬、大容量存儲(chǔ);其次,還可以實(shí)現(xiàn)不同功能芯片之間的互連,使單個(gè)封裝體具有更多的功能。TSV 工藝主要包括通孔刻蝕、通孔薄膜淀積(絕緣層、阻擋層、種子層的沉積)、通孔填充、化學(xué)機(jī)械拋光(CMP)、晶圓減薄和 RDL 與微凸點(diǎn)制作等關(guān)鍵技術(shù)。

2.1.3RDL/Bumping,TSV 在三維閃存封裝中的可能應(yīng)用方案

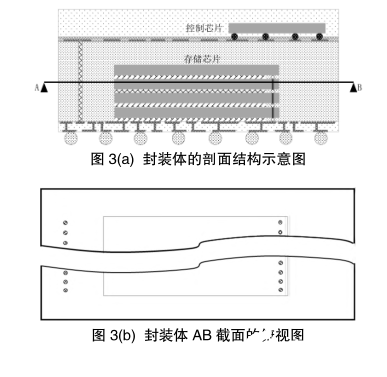

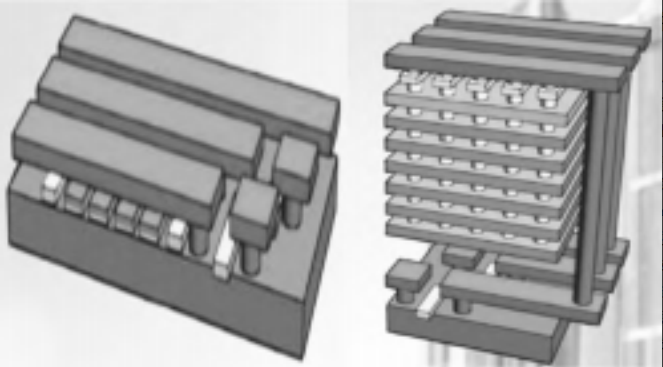

相比 DRAM 產(chǎn)品,將先進(jìn)封裝技術(shù)應(yīng)用到NAND 產(chǎn)品上,并實(shí)現(xiàn)商用的案例幾乎很少,本文基于 NAND 芯片的功能和先進(jìn)封裝技術(shù),對(duì)其應(yīng)用做了一些設(shè)想,其中一個(gè)方案如圖 3 所示。將 NAND芯片以垂直方向堆疊,利用 TSV 技術(shù)制作的通孔導(dǎo)電結(jié)構(gòu)代替?zhèn)鹘y(tǒng)的 WB 打線,用微 Bumping 來(lái)實(shí)現(xiàn)芯片與芯片、芯片與 RDL 之間的互連,并利用Molding 工藝對(duì)整個(gè)封裝體進(jìn)行第一次塑封。然后將控制芯片以倒裝的形式鍵合在另一 RDL 上,并且通過(guò)導(dǎo)電結(jié)構(gòu)實(shí)現(xiàn)兩層 RDL 的互連,以此實(shí)現(xiàn)內(nèi)部異質(zhì)芯片電路的連接。該結(jié)構(gòu)難點(diǎn)主要在于分層的問(wèn)題,因?yàn)?TSV 中導(dǎo)電結(jié)構(gòu)的金屬 Cu 的熱膨脹系數(shù)(1.8x10-5℃ -1 )和 Si 的熱膨脹系數(shù)(3x10-6℃ -1 )差距較大,當(dāng)該結(jié)構(gòu)熱量不能及時(shí)散出時(shí),金屬層 Cu 和Si 表面可能發(fā)生分層,從而導(dǎo)致產(chǎn)品的失效。

2.2 先進(jìn)封裝形式及其在三維閃存封裝中的可能應(yīng)用

2.2.1SiP

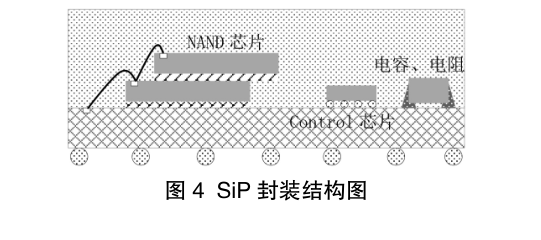

SiP 是將不同功能的芯片(例如存儲(chǔ)器、處理器、無(wú)源器件等)封裝在同一個(gè)塑封體中,以此來(lái)實(shí)現(xiàn)一個(gè)完整功能的封裝形式,具有高集成、低功耗、良好的抗機(jī)械和化學(xué)腐蝕的能力以及高可靠性等優(yōu)點(diǎn),如圖 4 所示。對(duì)照此概念,目前 3D NAND 應(yīng)用中的Managed NAND(eMMC,UFS 等),eMCP 產(chǎn)品較類似且已廣泛應(yīng)用,即將堆疊的 NAND 芯片、倒裝或金線連接的 Control 芯片、以及電容電阻互連在一個(gè)封裝體中,實(shí)現(xiàn)系統(tǒng)集成,同時(shí)根據(jù)產(chǎn)品需求的不同,增加芯片的數(shù)量和種類,以此實(shí)現(xiàn)異構(gòu)、異質(zhì)集成,減少封裝體積,降低系統(tǒng)成本。

2.2.2Fan-in/Fan-out

Fan-in 封裝是在晶圓上布 RDL,并植球,直接切割后形成單顆芯片。這種形式得到的單顆封裝體的尺寸幾乎與芯片的尺寸相同,且可以多晶圓同時(shí)加工,提高封裝的作業(yè)效率。但也因其 I/O 局限在單顆芯片尺寸范圍內(nèi),導(dǎo)致 I/O 數(shù)量被極大限制住,所以應(yīng)用一般僅限在小型電子器件,并且不需要較多I/O 需求的產(chǎn)品上。Fan-out 封裝技術(shù)屬于晶圓重構(gòu)技術(shù),將晶圓切割成單顆芯片后,重新布置在載體上,然后進(jìn)行塑封、RDL、植球、切割 ,從而得到面積大于芯片面積的封裝體。這樣可以靈活把控 I/O 的間距及數(shù)量不受芯片尺寸的限制。Fan-out 工藝也可分為芯片先上(Die First)和芯片后上(Die Last)兩種,相對(duì)于芯片先上,芯片后上具有塑封翹曲小和成品率高等優(yōu)點(diǎn),但是制造工藝相對(duì)復(fù)雜。

當(dāng)前,市面上的三維閃存芯片封裝的主流還是將芯片通過(guò)直接貼裝在封裝基板的表面上,然后采用金屬線鍵合工藝實(shí)現(xiàn)芯片焊盤(pán)與基板電性能連接。基板作為芯片封裝的核心材料之一,其成本占據(jù)整個(gè)封裝材料成本的 30%~50%;并且為了應(yīng)對(duì)產(chǎn)品朝著輕薄小的方向發(fā)展,基板中的設(shè)計(jì)會(huì)越來(lái)越復(fù)雜,而且層數(shù)也會(huì)隨之增加,導(dǎo)致基板的厚度增加,影響了總體的封裝厚度,還致使基板的價(jià)格進(jìn)一步提高。在線寬線徑方面,15/15μm(mSAP 工藝)已經(jīng)是接近極限,想再進(jìn)一步下探需要更換制作工藝,同時(shí)會(huì)帶來(lái)成本或其他負(fù)面效果,并且也很難低于5μm,單層的 PP 厚度最薄也只能接近 15μm。RDL工藝是晶圓制造端較成熟的工藝,可以達(dá)到1.5/1.5μm 的線寬線距;在厚度方面,單層的 RDL厚度可以控制在 5~20μm 的范圍之內(nèi),也是低于基板的厚度。

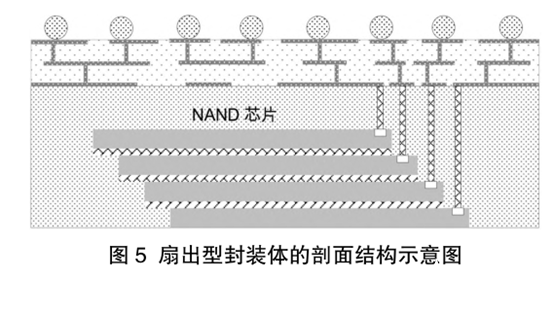

如將 Fan-out 應(yīng)用在三維閃存芯片封裝上,可起到提升信號(hào)速度,減少封裝體厚度的作用。本文設(shè)想的結(jié)構(gòu)如圖 5 所示,將 NAND 芯片層錯(cuò)開(kāi)堆疊(露出焊盤(pán)區(qū)),然后利用金屬導(dǎo)電結(jié)構(gòu)代替 WB 打線與外界信號(hào)連接,塑封后制作重新布線層和凸塊,以此實(shí)現(xiàn)內(nèi)外的導(dǎo)通結(jié)構(gòu)。該結(jié)構(gòu)的主要難點(diǎn)在于連接的問(wèn)題,本文針對(duì)該難點(diǎn)采用激光打孔和做金屬柱兩種方法,激光打孔是需要在塑封體上進(jìn)行鉆孔,使孔底落在芯片焊盤(pán)上,然后再深孔內(nèi)形成導(dǎo)電結(jié)構(gòu),從而連接 RDL 層實(shí)現(xiàn)電信號(hào)傳輸;金屬柱則是先在芯片 Pad 上形成金屬結(jié)構(gòu),然后進(jìn)行塑封,然后打磨塑封體露出金屬柱,實(shí)現(xiàn)與 RDL 層連接。

2.2.32.5D/Chiplet

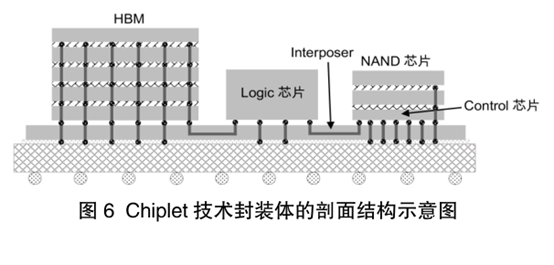

Chiplet 的封裝[6-8]被視為延續(xù)摩爾定律的新法寶,是將原 SoC 大尺寸的設(shè)計(jì)分散在較小的芯片上,將多個(gè)芯片通過(guò)先進(jìn)封裝技術(shù)重新組合在一個(gè) Si中介板上,形成一種“SiP”封裝形式,以此來(lái)滿足產(chǎn)品的需求。應(yīng)用 Chiplet 的優(yōu)勢(shì)首先在于利用 Si 中介板代替基板,將 NAND 芯片、DRAM 芯片、Logic 芯片和 Control 芯片等異質(zhì)芯片集成在 Si 中介板上,一是可以有效地解決熱效應(yīng)導(dǎo)致的異質(zhì)芯片與基板之間熱膨脹系數(shù)不匹配的問(wèn)題,二是由于 Si 中介板采用的 TSV 技術(shù),可以有效縮短電性傳輸路徑,從而提高其傳輸?shù)乃俣龋黄浯危琒i 中介板的電路設(shè)計(jì)是可以根據(jù)異質(zhì)芯片的不同需求而采取不同的工藝節(jié)點(diǎn),這正好符合處理器、DRAM、NAND 的不同工藝現(xiàn)狀,從而增加工藝的靈活性,縮短產(chǎn)品更新周期。

本文設(shè)想的結(jié)構(gòu)如圖 6 所示,結(jié)合 Chiplet 技術(shù)在 NAND 中的應(yīng)用,可采用前文提到的 TSV 技術(shù)將DRAM 芯片和 Logic 芯片垂直堆疊連接成 HBM 結(jié)構(gòu),然后通過(guò) Si interposer 與外界基板實(shí)現(xiàn)連接;單個(gè)的 Logic 芯片以倒裝(FC)的形式與 Si interposer實(shí)現(xiàn)連接,并通過(guò)內(nèi)部布線實(shí)現(xiàn)與 HBM 的電信連接;NAND 芯片和 Control 芯片垂直堆疊并通過(guò) Si interposer 實(shí)現(xiàn)與內(nèi)部的 Logic 芯片和外部的基板互連;通過(guò) Si interposer 實(shí)現(xiàn)系統(tǒng)內(nèi)互連,達(dá)到高度集成的目的。該結(jié)構(gòu)的難點(diǎn)在于產(chǎn)品還存在散熱等問(wèn)題,目前,市面上還沒(méi)有發(fā)現(xiàn)規(guī)模化的相關(guān)產(chǎn)品應(yīng)用,因此,未來(lái)還是充滿了挑戰(zhàn)。

3 結(jié)論

隨著數(shù)字經(jīng)濟(jì)時(shí)代的來(lái)臨,數(shù)據(jù)已經(jīng)成為了核心的生產(chǎn)要素,爆炸式的數(shù)據(jù)增長(zhǎng)對(duì)計(jì)算和存儲(chǔ)提出了更高的要求,傳統(tǒng)的三維閃存芯片封裝技術(shù)和形式將會(huì)面臨更多的技術(shù)挑戰(zhàn)。為此,本文重點(diǎn)探討了 Bumping、RDL 和 TSV 等先進(jìn)封裝技術(shù)及 SiP、Fan-in/Fan-out 和 2.5D/Chiplet 等先進(jìn)封裝形式在3D NAND 中應(yīng)用的可行性。在 3D NAND 中,先進(jìn)封裝不僅能提高芯片的集成度,減少封裝的體積,還可以縮短信號(hào)的傳播路徑,從而提高數(shù)據(jù)處理的速度。

國(guó)家“十四五”信息化政策提出加快集成電路關(guān)鍵技術(shù)的攻關(guān),存儲(chǔ)芯片的創(chuàng)新,強(qiáng)調(diào)了存儲(chǔ)芯片的重要性。我國(guó)已初步完成在存儲(chǔ)芯片領(lǐng)域的戰(zhàn)略布局,雖然起步比較晚,部分核心技術(shù)受到封鎖,距離其他國(guó)家還有一定的差距,但是由于存儲(chǔ)產(chǎn)品屬于大宗商品,只要性能滿足用戶需求,可替換率很高,這為我國(guó)存儲(chǔ)器發(fā)展趕超其他國(guó)家的行業(yè)巨頭提供了機(jī)會(huì)。先進(jìn)封裝作為延續(xù)摩爾定律的前沿技術(shù),目前在 3D NAND Flash 產(chǎn)品中的應(yīng)用還處于探索階段,隨著未來(lái)市場(chǎng)的不斷需求,以及先進(jìn)封裝技術(shù)的不斷成熟和成本不斷降低,相信在未來(lái)必將迎來(lái)新的篇章。

審核編輯 黃宇

-

芯片

+關(guān)注

關(guān)注

456文章

50886瀏覽量

424193 -

閃存

+關(guān)注

關(guān)注

16文章

1789瀏覽量

114961 -

封裝

+關(guān)注

關(guān)注

126文章

7933瀏覽量

143045 -

存儲(chǔ)

+關(guān)注

關(guān)注

13文章

4320瀏覽量

85904

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

三維封裝工藝流程與技術(shù)

先進(jìn)封裝技術(shù)在三維閃存中的應(yīng)用

先進(jìn)封裝技術(shù)在三維閃存產(chǎn)品中的應(yīng)用探討

先進(jìn)封裝技術(shù)在三維閃存產(chǎn)品中的應(yīng)用探討

評(píng)論