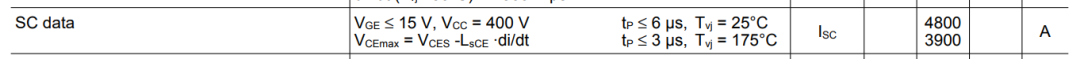

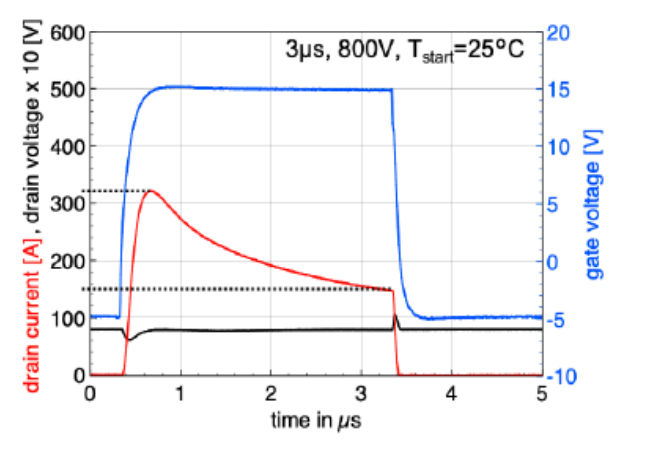

SiC MOSFET芯片的短路能力是非常差的,目前大部分都不承諾短路能力,有少數在數據手冊上標明短路能力的幾家,也通常把短路耐受時間(SCWT:short circuit withstand time)限制在3us內。

這個相比Si基IGBT動輒6us甚至10us的時間,降低了很多,最近看了一些資料,嘗試著理解一下。

從最基本的邏輯出發,芯片發熱是芯片內部的電流做功引起的,因此主要考慮電流和芯片內部的結構。

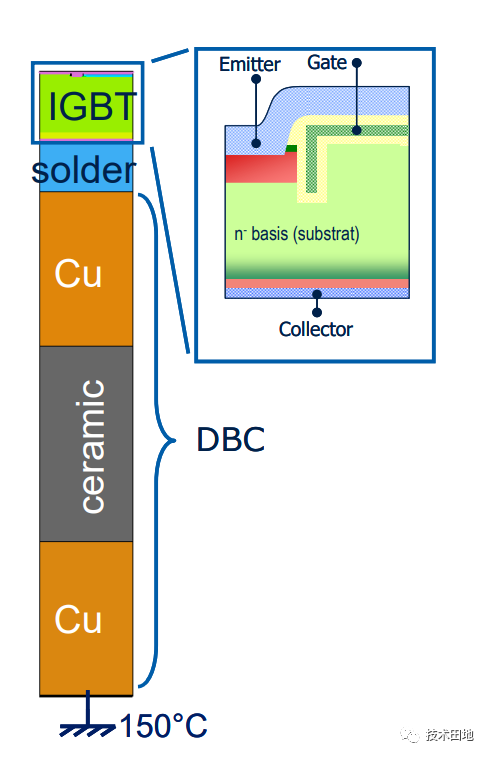

先看Si IGBT模塊的結構:

我們可以看到,一顆IGBT芯片焊接在DBC襯板上,芯片底部是集電極(Collector),和散熱的銅連接,頂部是發射極(Emitter),和鍵合線相連(圖中未畫出),電流方向從C到E。

我們都知道,IGBT工作的時候,本來電阻較高的N-漂移層,由于電導調制效應,載流子被注入,這就導致N-漂移層的電導率很高,因此大電流流過這個區域的時候,壓降ΔV drift很小,此區域的發熱功耗P=ΔV×I就很小,因此在N-區不會產生大量的熱量。

IGBT的壓降主要是來自哪里?其實主要是襯底的P到N這個場截止層,從下圖的紅色電場分布看得出來,電場主要是由靠近集電極的PN結來承受。

根據發熱功率P=ΔV×I,這個ΔV很大,因此這個P很大,發熱主要是靠近IGBT芯片底部的集電極。

再看第一張圖,IGBT芯片底部,那不正好是散熱的覆銅板嗎?所以這個熱可以很快擴散,相對來說容易散出去。

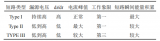

再看SiC MOSFET的結構:

大家不要被這張圖騙了,圖是對的,但是下面那個N+SUBSTRATE厚度比例不對,圖中N-DRIFT層的厚度是10um,而N+SUBSTRATE的厚度,是200um左右!

MOS結構就很簡單了,導通的時候沒有PN結,是通過MOS溝道導電的,因此,哪個地方發熱嚴重完全取決于哪個地方的電阻大!

直接上圖(感謝Anant Agarwal教授的資料)

可以看到,溝道電阻和外延層占比遙遙領先!根據最簡單的安培定理

可以得出,SiC MOSFET芯片發熱最嚴重的區域是MOS溝道和外延層,也就是芯片的頂部區域!

對于溝槽SiC來說也差不多,因為溝槽SiC電阻最大的區域是外延層,也靠近芯片的頂部。

這下就不太好搞了,因為散熱板在芯片底部,但是發熱集中在芯片頂部,因此SiC MOSFET芯片短路時的散熱天然要差一些,畢竟導熱銅襯板離熱源還有點遠。

當然,不能完全只看壓降和電阻,Si IGBT和SiC MOSFET芯片本身的尺寸以及電流大小也要看的。

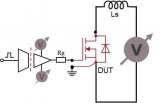

上圖是英飛凌做的一個對比,我們簡單算一下,一個標稱300A的IGBT芯片,尺寸10mm×10mm,短路電流差不多2000A。

一個標稱120A的SiC MOSFET芯片,尺寸5×5mm,短路電流差不多1200A來算。

IGBT短路電流密度:2000/100=20A/mm2

SiC MOSFET短路電流密度:1200/25=48A/mm2

僅僅是電流密度大了2.5倍,再加上發熱位置是芯片散熱較差的頂部,SiC 芯片短路能力比IGBT差也是情理之中。

如圖,可以看到,大部分發熱集中在SiC MOSFET芯片頂部。

圖源:英飛凌

再看看IGBT的溫度分布,就要均勻很多。

-

芯片

+關注

關注

455文章

50719瀏覽量

423164 -

MOSFET

+關注

關注

147文章

7157瀏覽量

213151 -

IGBT

+關注

關注

1266文章

3789瀏覽量

248899 -

SiC

+關注

關注

29文章

2805瀏覽量

62608

發布評論請先 登錄

相關推薦

如何實現SiC MOSFET的短路檢測及保護?

為何使用 SiC MOSFET

SiC-MOSFET的應用實例

SiC-MOSFET與Si-MOSFET的區別

SiC-MOSFET的可靠性

SiC-MOSFET有什么優點

SiC功率器件SiC-MOSFET的特點

SiC MOSFET:經濟高效且可靠的高功率解決方案

SiC MOSFET的器件演變與技術優勢

為什么SiC MOSFET的短路耐受時間比較小

SiC MOSFET學習筆記1:短路保護時間

SiC MOSFET短路失效的兩種典型現象

淺談SiC MOSFET芯片的短路能力

淺談SiC MOSFET芯片的短路能力

評論