一推薦使用獨立的上/下電時序管理芯片:SLG7RN46137V

1SLG7RN46137V芯片已經編程燒錄完畢,直接貼片使用即可。

2高壓伺服、交流伺服、變頻器、壓力變送器、中壓伺服應用中,強烈推薦使用獨立的上電時序管理芯片。

因為這類似系統的干擾信號相對比較大,如 “振鈴干擾”、“電容退耦”等原因,導致弱電控制部分的控制信號,較容易被高壓部分干擾。使用獨立的上電/下電管理芯片,可以有效的規避這個問題。

3PLC控制器、PLC耦合器、一網到底PLC-DIDO模塊,可以暫時不考慮。

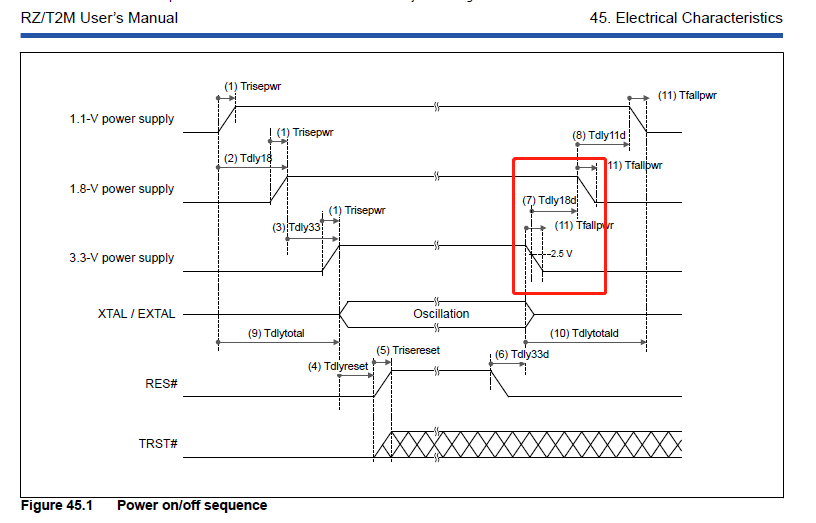

4RZ/T2M、RZ/T2L、RZ/N2L系列,上電和下電管理時序說明如下:

低電壓的先上電,高電壓的后上電;高電壓的先掉電,低電壓的后掉電。這樣的時序要求其實對于分立式DCDC的供電設計邏輯控制是比較復雜的。

詳細的時序圖如下:

上圖中紅框里面的這個時序,是最為關鍵的。如果1.8v跌落后,3.3v依然持續供電,會導致RZ/T2M、RZ/N2L、RZT2L芯片損壞。

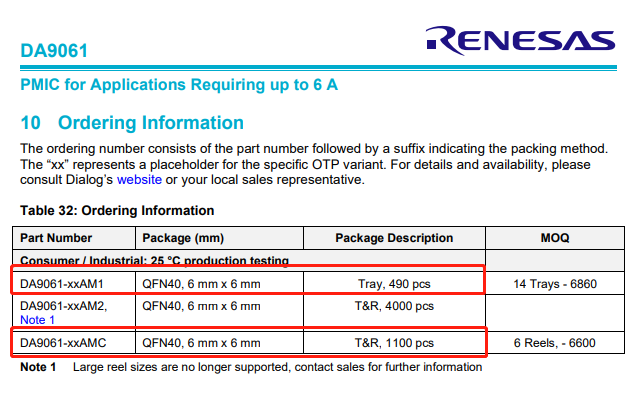

二推薦使用的PMIC:DA9061-16AM1 & DA9061-16AM

1AM1和AMC僅僅是芯片包裝方式的不同。芯片本身并未明顯不同。

2早期的這份文檔(2.7以及之前),此處描述有明顯錯誤。

DA9061-00AMx,為空白片。

DA9061-16AMx,為編程片,無需燒錄,購買后直接焊接。上電時序和電源管理邏輯,已經在出廠之前燒錄到了芯片內部。

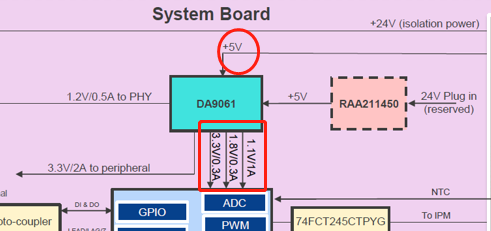

應用細節描述

RZ/T2M和RZ/N2L芯片內部的供電結構的原因,導致3.3v,1.8v,1.2v的上電時序有較為嚴格的時序要求。

PMIC的上電和掉電時序,是完全可以由內部OTP控制的。目前PMIC的完整料號是DA9061-16AM1,其中16AM1代表這個OTP已經被燒錄,并可以支持RZ/T2M、RZ/N2L。

下單和訂購樣品的時候,直接選擇DA9061-16AM1或者DA9061-16AMC即可。不要訂購空白片DA9061-00AM1。

此設計已經在瑞薩中國的EVK上進行過驗證。不用擔心匹配性、穩定性問題。

三IAR編譯環境使用小技巧

1IAR打“編譯”專用補丁

如您不評估Profinet,請使用IAR 9.30.1或以上,比如9.32.1。官方例程均基于該版本(IAR 9.30.1),可以跳過下面的所有敘述。

a) IAR85和IAR92,無法編譯R52 CORE的 RZ/T2M和RZ/N2L。所以需要打補丁。

b) IAR9.3x 版本,可以編譯RZT2M和RZN2L。

①如果使用IAR85和IAR92,需要手動打補丁進行編譯。

②實測,IAR 8.5.x,IAR 9.2.X系列,打過補丁后,均可正常編譯出 可執行文件。

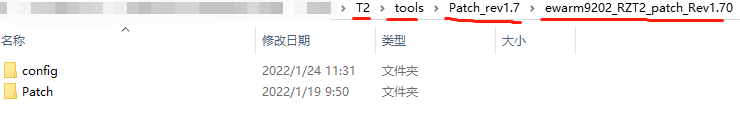

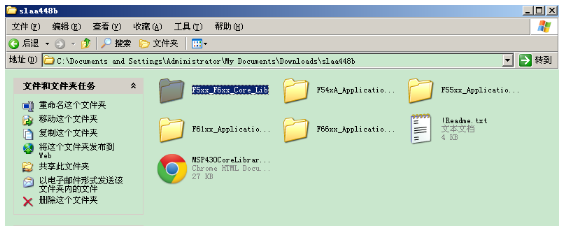

③編譯器補丁如下。

④打補丁的方法。

Please copy and overwrite the files of "config" and "Patch" to the

把這兩個文件復制到

注意:這個編譯補丁,和PN demo的運行補丁,不是同一個概念,請勿混淆。

2編譯例程不通過時,請嘗試以下修改和對策

● 編譯路徑太深,或者某一級的目錄的名字太長。

●編譯的目錄中有文中路徑。

●把需要編譯的目錄,復制到某個盤符的根目錄,或者桌面。

● ECAT例程,需要按照ecat例程中的pdf文件指導,自己生成ecat源碼。

3如何簡單的判斷是否堆棧溢出

①首先找到工程目錄下的startup_ram.asm文件,這個文件在RZT1上是loader_init.asm文件。

②找到下面的類似于clear bss段。這個區域在RZT1上是“loader_bss_init:”部分。

③加入如下代碼:給每個stack設置初始值為特定的 0x55,0x66,0x77等。

原理:一旦程序異常復位,并進入“abort handler”或者“hard fault”后,可以立刻查看如下堆棧段,是否有被“撐爆”的情況。即如果堆棧段 頂端出現非“0x55,0x66,0x77”的數據,即可認為棧溢出 出現過。

左右滑動查看完整內容

;-----------------------------------------add stack init to 0x55----------------------------------- cstack_set55: ldr r0, =0x55555555 ldr r1, =SFB(CSTACK) ldr r2, =SFE(CSTACK) cmp r2, r1 beq svcstack_set66 set_loader_cstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_cstack dsb ; Ensuring data-changing svcstack_set66: ldr r0, =0x66666666 ldr r1, =SFB(SVC_STACK) ldr r2, =SFE(SVC_STACK) cmp r2, r1 beq IRQSTACK_set77 set_loader_svcstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_svcstack dsb ; Ensuring data-changing IRQSTACK_set77: ldr r0, =0x77777777 ldr r1, =SFB(IRQ_STACK) ldr r2, =SFE(IRQ_STACK) cmp r2, r1 beq FIQSTACK_set88 set_loader_irqstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_irqstack dsb ; Ensuring data-changing FIQSTACK_set88: ldr r0, =0x88888888 ldr r1, =SFB(FIQ_STACK) ldr r2, =SFE(FIQ_STACK) cmp r2, r1 beq UNDSTACK_set99 set_loader_fiqstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_fiqstack dsb ; Ensuring data-changing UNDSTACK_set99: ldr r0, =0x99999999 ldr r1, =SFB(UND_STACK) ldr r2, =SFE(UND_STACK) cmp r2, r1 beq ABTSTACK_setAA set_loader_undstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_undstack dsb ; Ensuring data-changing ABTSTACK_setAA: ldr r0, =0xAAAAAAAA ldr r1, =SFB(ABT_STACK) ldr r2, =SFE(ABT_STACK) cmp r2, r1 beq jump_loader_init2 set_loader_abtstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_abtstack dsb ; Ensuring data-changing ;---------------------------------------end---------------------------------------

審核編輯:湯梓紅

-

控制器

+關注

關注

112文章

16332瀏覽量

177813 -

變頻器

+關注

關注

251文章

6548瀏覽量

144515 -

IAR

+關注

關注

5文章

350瀏覽量

36665 -

時序圖

+關注

關注

2文章

58瀏覽量

22443 -

DCDC

+關注

關注

29文章

813瀏覽量

71263

原文標題:RZ/T2M RZ/N2L RZ/T2L系列應用心得(3-上)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在IAR軟件編譯環境編譯,出現中斷標志警告如何解決?

IAR環境配置

如何用IAR6.3編譯環境中ucos在msp430上的移植的詳細中文資料

IAR ARM集成開發環境學習教程

IAR編譯環境使用小技巧(1)

IAR編譯環境使用小技巧(1)

評論