設(shè)計中經(jīng)常會碰到一些非常復(fù)雜的邏輯,組合邏輯層數(shù)非常多,往往造成無法滿足設(shè)計的時鐘頻率要求。

Cadence綜合工具Genus支持retime技術(shù)。

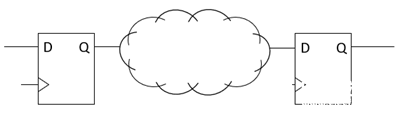

Retime技術(shù)的原理非常簡單。例如下圖,兩級flop之間的組合邏輯太大,限制了時鐘頻率。

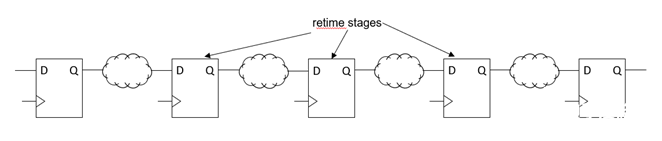

Retime技術(shù)類似pipeline。Retime技術(shù)在兩級flop之間插入retime stage flop,把復(fù)雜的組合邏輯分割成里幾個部分,每個部分的組合邏輯層數(shù)都相對較小,使得每一級都能工作在較高的頻率,從而滿足整個設(shè)計的時鐘要求。

當(dāng)然,retime技術(shù)不是“免費”的。

-插入了中間級,latency增加了。上圖中l(wèi)atency增加了3個cycle。

-插入了中間級flop,面積功耗都會大一些。

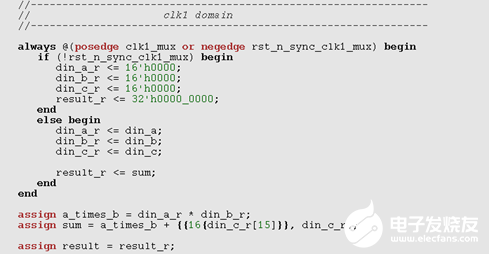

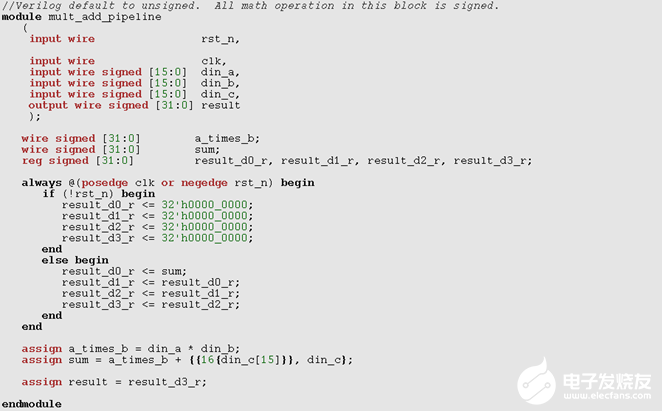

下面是一個實例。這個設(shè)計實現(xiàn)乘+加(multiply-add)運算。這類運算在DSP中很常見。這里的乘法器是16位輸入乘16位輸入,得到32位結(jié)果,再和符號擴展(sign extended)后的第三個輸入相加。

綜合用Genus,target 65nm的庫。順便插一句,很多朋友總以為只要上了先進工藝,timing的問題就解決了。做產(chǎn)品與做科研不同。做產(chǎn)品是要講成本的。上了先進工藝只能說明你資金充裕。使用成熟工藝,雖然慢很多卻能實現(xiàn)一樣的performance,這才是真正的設(shè)計能力。

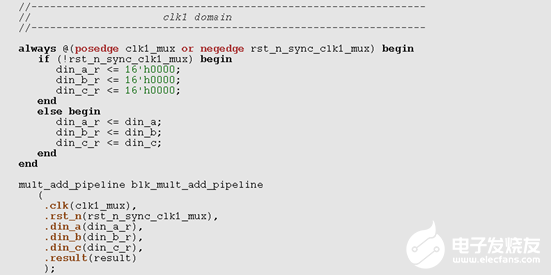

首先來看看最直接的實現(xiàn)方案。這里輸入鎖存后再運算,運算結(jié)果鎖存后再輸出。這樣做屏蔽了input delay,output delay對運算邏輯timing的影響,可以更好地評測運算邏輯的速度。

這里也可以看到,手動插入pipeline stages很難,尤其是乘法運算。這是一個整體,無法手動切割。當(dāng)然有朋友可能會說,例化Synopsys DesignWare里的multi-stage multiplier。那樣當(dāng)然也是可以的,優(yōu)缺點你也知道了,這里就不贅述了。

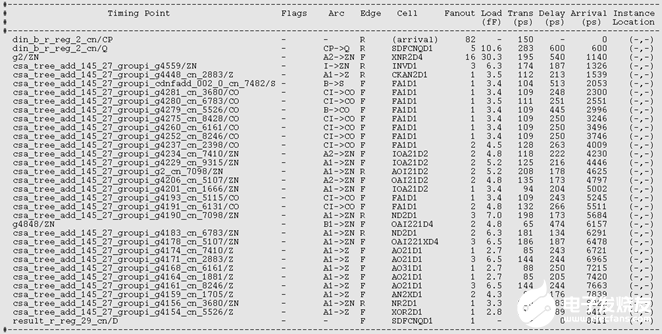

Genus綜合后最差的路徑如下。

時鐘周期為9ns,positive slack 26ps,能滿足。也就是說這個實現(xiàn)方案最多也就是只能跑110MHz左右。如果系統(tǒng)的要求是400MHz,這個最直白的實現(xiàn)方案顯示是不行的。

下面再來看看使用Genus retime技術(shù)的實現(xiàn)方法。在這個實現(xiàn)中把multiply-add放到了一個獨立的module中,這樣做是為了在Genus綜合中單獨將這個module的retime打開。

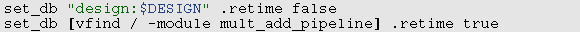

Genus綜合時在syn_generic之前關(guān)閉整個設(shè)計地retime,打開multiply_add_pipeline模塊地retime。

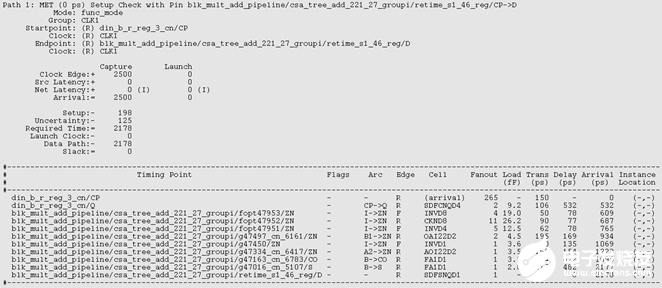

Genus綜合結(jié)果如下。

可以看到,時鐘提高到了2.5ns (400MHz),依然能滿足,slack為0。

這里還要提一下,Genus retime的算法非常聰明。RTL里我們給了中間三級32*3=96個DFF,實際上最后Genus并沒有全部用掉96個DFF,只用了2+9+31個DFF置換為retime中間級flop,其余的都優(yōu)化掉了。可以說Genus retime真的很“省”。

總結(jié)一下,Genus retime技術(shù)通過移動pipeline flop的位置將復(fù)雜組合邏輯分割成幾級,可以大大提高電路的速度。

審核編輯:黃飛

-

Cadence

+關(guān)注

關(guān)注

65文章

921瀏覽量

142084 -

時鐘設(shè)計

+關(guān)注

關(guān)注

0文章

27瀏覽量

10908 -

Retimer

+關(guān)注

關(guān)注

2文章

9瀏覽量

7393

發(fā)布評論請先 登錄

相關(guān)推薦

使用Genus retime技術(shù)的實現(xiàn)原理

使用Genus retime技術(shù)的實現(xiàn)原理

評論