Part1 問題的來源

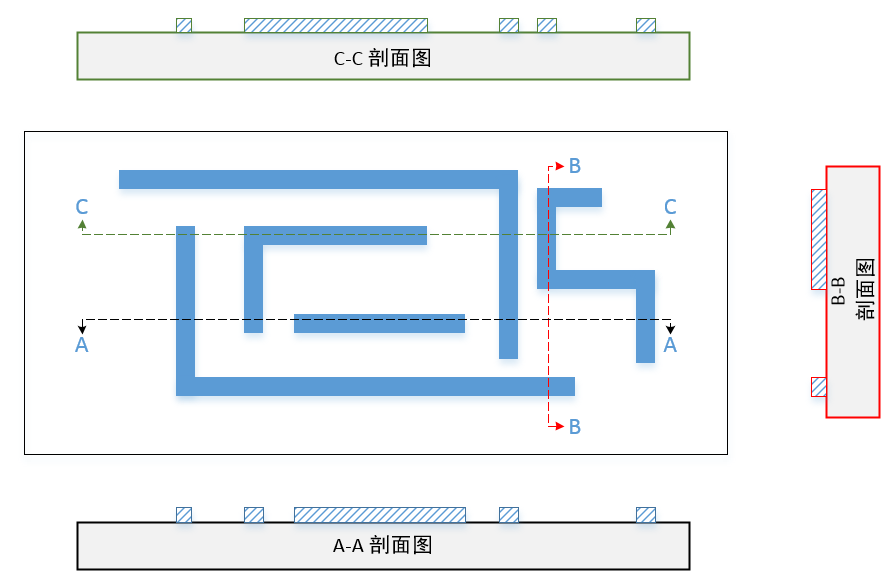

圖1.1單層布線

如果之前看過分立電路的印刷電路板(PCB),那么集成電路的布線層就相當于“微縮版的PCB”,它也分為單層布線(單面板)和多層布線(雙面板,多層板)。(如圖1.1)在集成電路的同一個布線層中,不同金屬導線之間通過絕緣材料(二氧化硅很常見)實現(xiàn)電學絕緣。

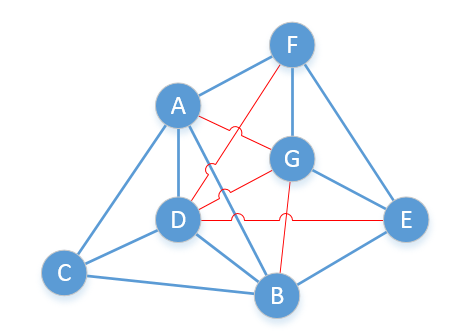

圖1.2復雜拓撲關系的布線

為了實現(xiàn)更復雜的功能,電路中的器件會越來越多,器件之間的電學連接拓撲關系也越來越復雜,結果是使用單層布線無法“布通”。這種情況下,只有增加布線層才能實現(xiàn)“布通”的效果(如圖1.2,紅色跳線就代表需要另外一層才能完成布線),這就是所謂的“多層布線”。

Part2 多層布線

2.1 多層布線的物理結構

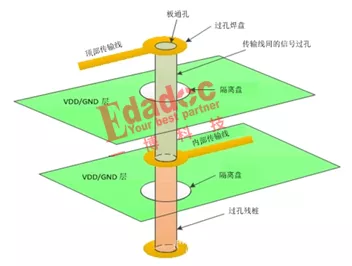

相鄰布線層之間使用絕緣材料(常見的是SiO2)進行電學隔離,相同布線層中的導線使用絕緣材料(常見的是SiO2)進行電學隔離;相鄰布線層中的導線,通過在絕緣層上開孔、孔內填滿導電材料,“實現(xiàn)電學連通”。

2.2 孔

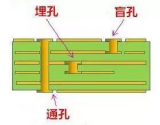

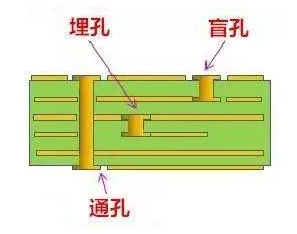

穿透絕緣層的“孔”分為兩大類:第一種“孔”稱為Contact(接觸孔),用來連接“布線”和“器件層的電極”;第二種“孔”稱為Via(通孔),用來連接位于不同布線層的導線。

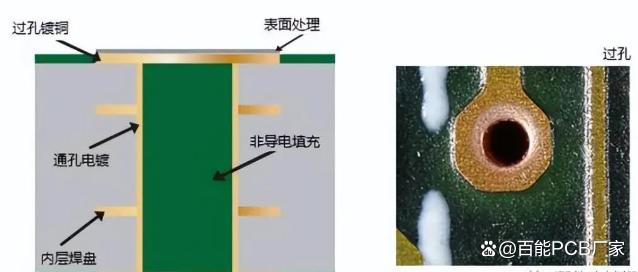

“孔”,從工藝制備的角度來說,分為兩步,首先是開孔,然后是在孔內填滿導電材料;從版圖的角度來說,畫出來就只是一個“矩形”而已。

2.3 量變帶來的新問題

在進行“多層互連”的時候,很多問題自然而然的出現(xiàn)了,接下來通過剖面圖來逐一說明:

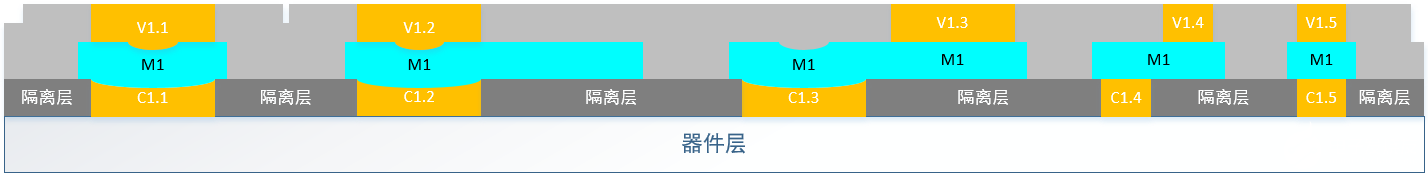

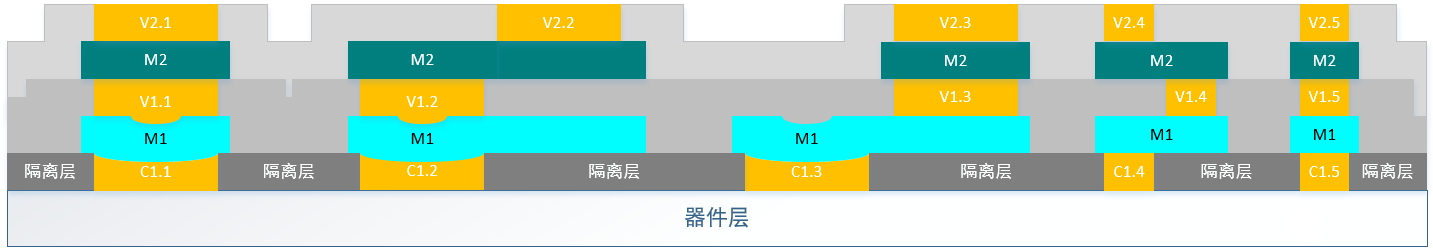

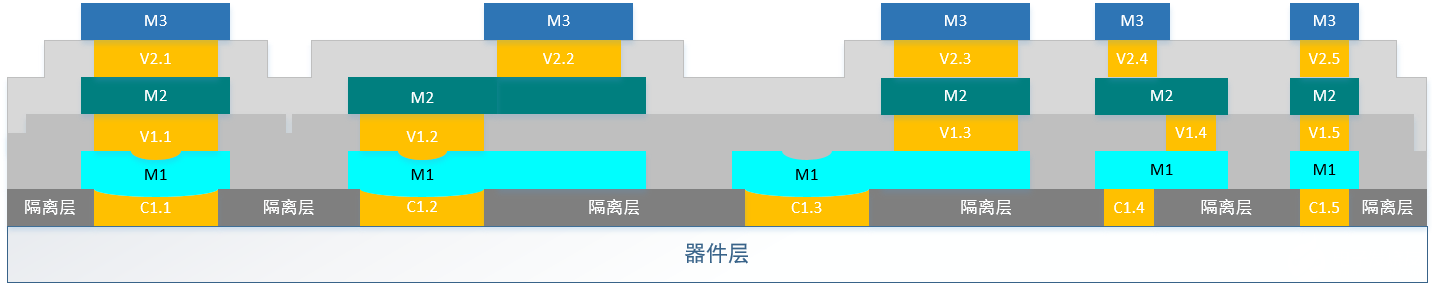

圖2.1制作Contact(接觸孔)

(圖2.1)在器件層上制作了“Contact”,“黃色”表示在孔中填充的導電材料,“灰色”表示各孔之間的絕緣材料,共用C1.1,C1.2,C1.3,C1.4,C1.5表示了五種情況。其中C1.1~C1.3因為孔比較大,所以金屬材料在填充的時候,表面會向下凹(表面張力和重力導致);C1.4和C1.5因為孔比較小,所以填充的金屬表面近似水平。

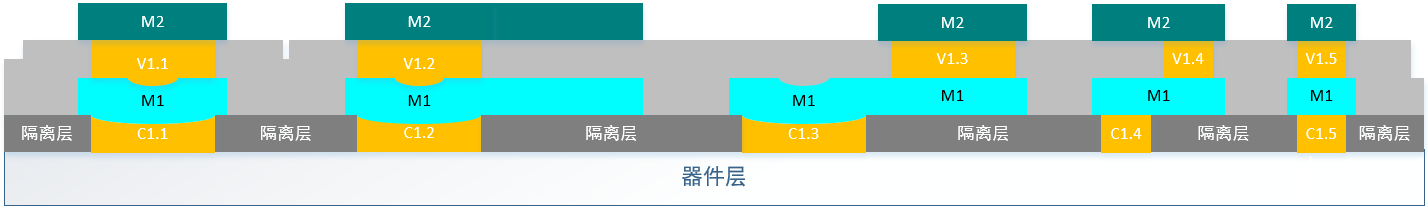

圖2.2制作Metal 1(簡寫為M1)

(圖2.2)做完了Contact之后,先在材料表面生長一層Metal,然后使用光刻和腐蝕工藝得到需要的金屬布線。

圖2.3制作Via 1(簡寫為V1)

(圖2.3)在Metal 1上生長絕緣層,然后做孔。因為這次的孔用來連接M1和M2,所以它的名字改為“Via”,翻譯成“通孔”,通的意思類似“架在河上的橋梁,取穿通,打通的意思,打通的就是相鄰互連層之間的絕緣材料”。

那么Via應該放在哪里呢?這個東西沒有多么神器,你就把它當成做試驗,所有的可能都試一下,我畫了5種情況,分別是“V1.1~V1.5”。

圖2.4制作Metal 2(簡寫為M2)

(圖2.4)做完了Via 1之后,先在材料表面生長一層Metal,然后使用光刻和腐蝕工藝得到需要的金屬布線。因為這是第二層Metal,所以稱它為Metal 2,這里簡寫為M2。

圖2.5制作Via 2(簡寫為V2)

(圖25)在Metal 2上生長絕緣層,然后做孔,即Via 2。現(xiàn)在,應該把所有的可能都列出來了,如果有忘記分析的情況,大家留言提醒一下。

圖2.6制作Metal 3(簡寫為M3)

(圖2.4)做完了Via 2之后,先在材料表面生長一層Metal,然后使用光刻和腐蝕工藝得到需要的金屬布線。因為這是第三層Metal,所以稱它為Metal 3,這里簡寫為M3。現(xiàn)代多層布線可以到128層以上,這里只畫3層進行演示。

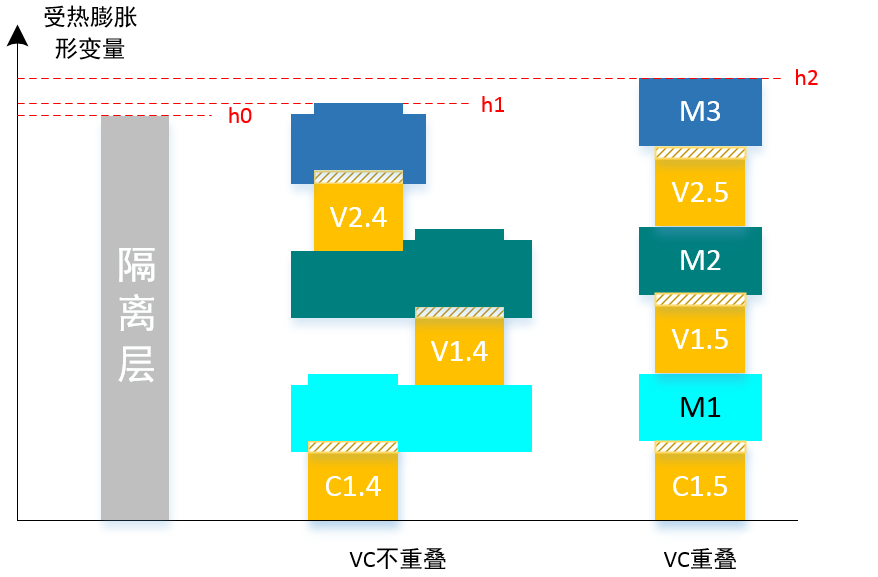

小結一下:金屬層數(shù)的命名是根據(jù)工藝制造的先后命名的,從剖面圖來看就是從下向上依次排序的;在垂直方向,C1.1-V1.1-V2.1和C1.5-V1.5-V2.5是重合的,其它的都存在不重合,也就是說,Contact和Via在垂直方向可能會出現(xiàn)“重合、交錯”兩種情況。

那么問題來了,重合和交錯可能會帶來什么影響?

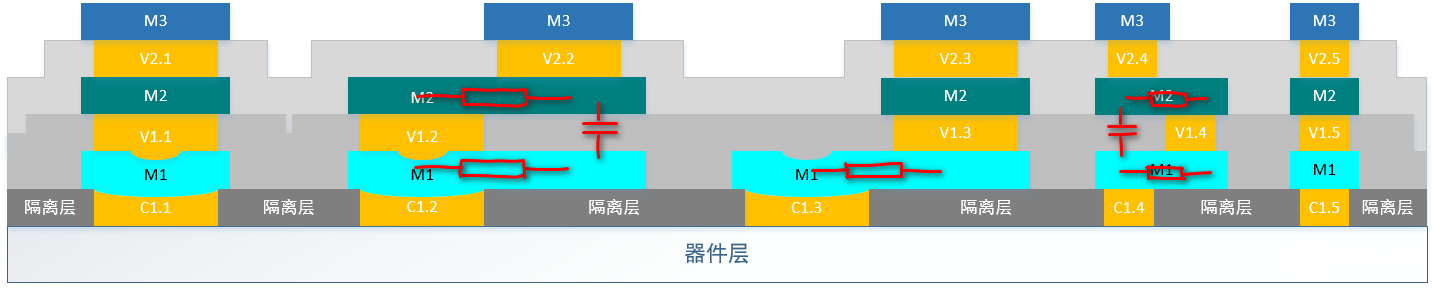

2.4 問題分析

交錯的孔會引入寄生電阻和寄生電容,除非是設計本來就有的,否則寄生效應會對電路性能構成不利的影響,會增加后仿真中調整參數(shù)的工作量。

圖2.7寄生電阻和寄生電容

2.4.2 可制造性

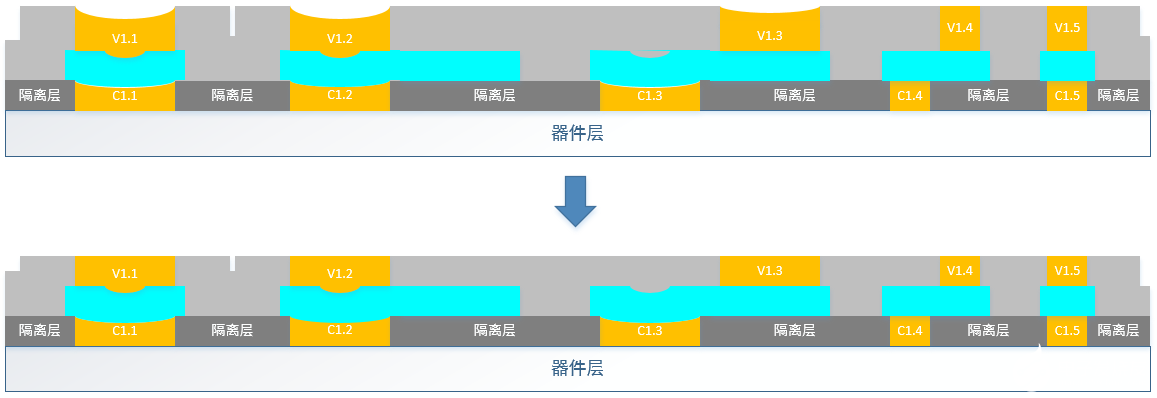

除了電學性能之外,還需要考慮的是可造性。對比V1.2和V1.3,其中V1.2的地基是凹陷,V1.3的地基是平面。因為后面的工藝會繼承前面的凹陷,很多時候都會放大凹陷的程度,最終降低良率,所以“平面地基”更有利于后面的工序制造。

對于打孔來說,表面無法填平是客觀存在的。為了避免在不平整的地基上做孔,要么采用V1.3的方法做孔,要么開發(fā)“平坦化工藝”,比如CMP工藝,把表面去掉一層,也就是表面沒有填平的地方全部去掉,那么就不存在不平整的地基了。Via 1這一層就采用了平坦化工藝(如圖2.8)。

圖2.8平坦化工藝(去掉坑坑洼洼,把表面磨平)

2.4.3 可靠性

集成電路工作時可能會產(chǎn)生大量的熱(比如,計算機CPU不加散熱器是可以煎雞蛋的),構成集成電路的各種材料就發(fā)生“熱脹冷縮”(如圖2.9)

圖2.9熱脹冷縮

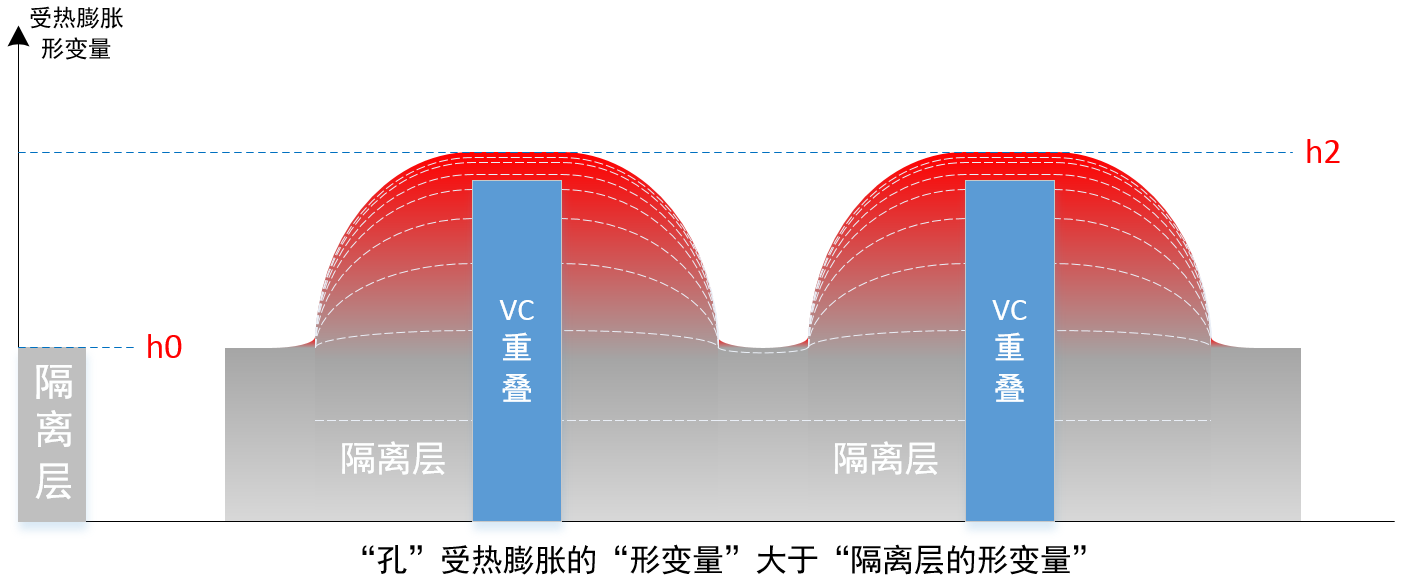

這里做的是最簡單的受熱膨脹的分析,并且假設“孔受熱膨脹變形最嚴重,絕緣材料(隔離層)和導電材料(Metal)相對很小被忽略”:

(圖2.9的縱坐標)重合孔的形變量(h2)最大,交錯孔的形變量(h1)次之。隨著布線層數(shù)↑,h2和h1繼續(xù)增大,顯然“h2-h1”繼續(xù)增大。

如果h0隨溫度變化沒有h2大,就會出現(xiàn)(圖2.10)的情況:最壞的情況=隔離層被孔撐破;次之,隔離層沒有被撐破,但是反復大幅度形變,很快就會出現(xiàn)裂縫。隔離層被破壞之后,相鄰層的導線可能會短路,形變較大處的導線可能會被折斷,通過裂縫入侵的水汽等雜質會破壞芯片內部結果,導致芯片很快報廢。“芯片壽命很短,可靠性很低”都是不能被用戶接受的。(圖2.10)僅以重疊孔為例,“VC不重疊”只是比“VC重疊”的破壞力弱一些而已。

圖2.10孔受熱膨脹的極端情況

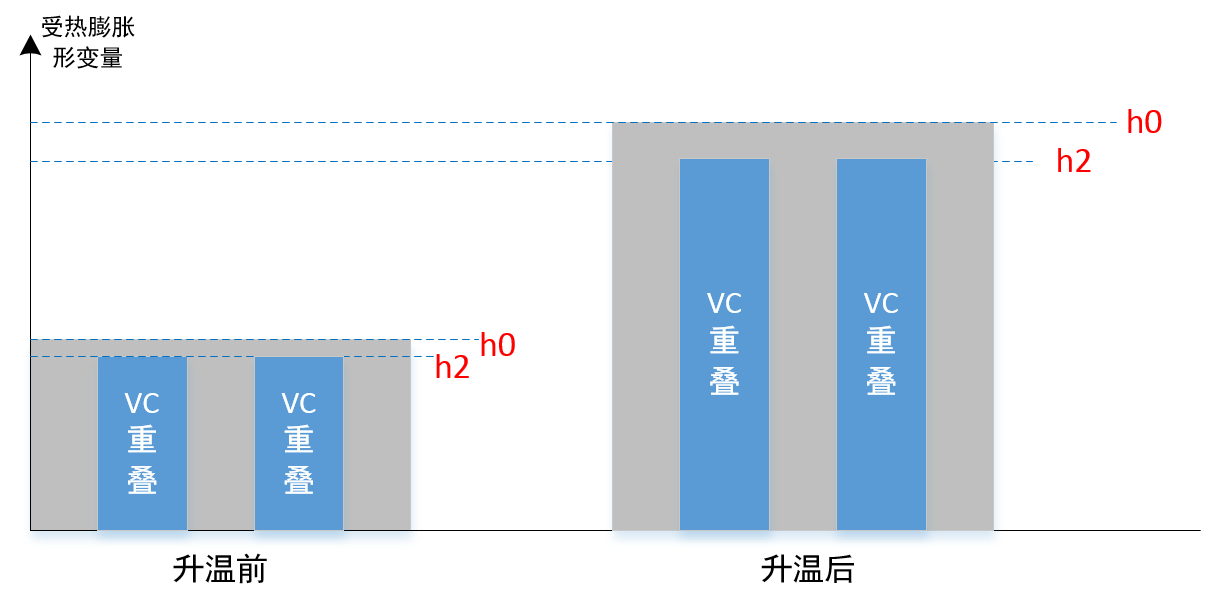

如果h0隨溫度變化與h2相同,就會出現(xiàn)(圖2.11)這種非常理想的情況。

圖2.11受熱膨脹的理想情況

2.5 對策

版圖設計是建立在“工藝流程”基礎上的,不能隨心所欲的畫;版圖和工藝配合,就會制造出特定的物理結構。

盡可能的使孔和絕緣材料的膨脹形變量相同,如果工藝上無法實現(xiàn)這一點,首先要減少重合孔的使用,其次是減少布線的層數(shù)。

審核編輯:黃飛

-

集成電路

+關注

關注

5387文章

11536瀏覽量

361664 -

電容

+關注

關注

100文章

6038瀏覽量

150277 -

cpu

+關注

關注

68文章

10855瀏覽量

211606 -

光刻

+關注

關注

8文章

321瀏覽量

30159 -

寄生電阻

+關注

關注

1文章

20瀏覽量

2280

發(fā)布評論請先 登錄

相關推薦

多層印制電路板中過孔互連多層供電系的建模與仿真

高速PCB中的過孔設計,你真的懂嗎?

高速PCB設計中的過孔和背鉆技術解析

多層PCB如何過孔

如何實現(xiàn)多層PCB的過孔

PCB中過孔和背鉆的技術知識

PCB生產(chǎn)中的過孔和背鉆有些什么樣的技術?

深度解析多層互連的過孔設計

深度解析多層互連的過孔設計

評論