簡介

SiC 功率 MOSFET 和肖特基二極管正在快速應用于電力電子轉換半導體 (PECS) 應用,例如電動汽車充電和牽引、儲能系統和工業電源。SiC 功率 MOSFET 已在電動汽車車載充電器中得到廣泛應用,并且在非車載充電器中也越來越受歡迎。與當前逆變器中的 Si IGBT 解決方案相比,這些器件為純電動汽車帶來了改善逆變器續航里程和/或降低成本的優勢。服務器電源中的設備已大量出貨,牽引逆變器中的設備數量也在不斷增加。盡管 SiC MOSFET 至少從 1987 年就已經存在,但在如此大批量和高可靠性市場的廣泛采用卻花了幾十年的時間。這是因為器件的許多方面都需要進行數量級的改進,特別是柵極氧化物的質量和可靠性。

挑戰在于,所有這些市場,尤其是交通運輸市場,都期望系統級別具有極高的可靠性。應用要求相當高:大量 SiC 芯片和總 SiC 有效面積(數百至數千 mm2)、高結溫(通常為 175 °C 及以上)和低故障率(“早期”期間每年累計 < 1 ppm)。”,預計很快就會得到改善。)預計很快就會有所改善。)同時,與硅相比,SiC 的可靠性情況是獨一無二的:

- 一些 SiC 失效機制比 Si 更嚴重

- 至少一種失效機制是 SiC 所獨有的,并且在Si

- 對 SiC 的要求在很多方面都高于對 Si 的要求

接受這一挑戰意味著 SiC 器件制造商必須能夠通過提供徹底且有時新穎的表征,在“浴盆曲線”的所有階段展示出色的可靠性預測質量、隨機故障率和磨損壽命。但這也意味著,與硅行業相比,由制造商和最終用戶組成的行業聯盟組織必須以極快的速度制定指南和標準。

在硅產業中,相對于技術的成熟度和廣泛采用程度,指導方針和標準的啟動和制定需要更長的時間。

SiC 中的失效機制

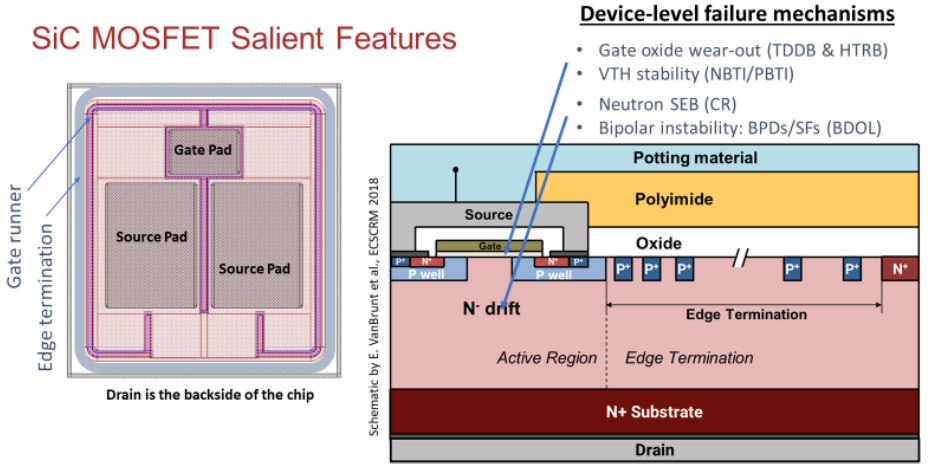

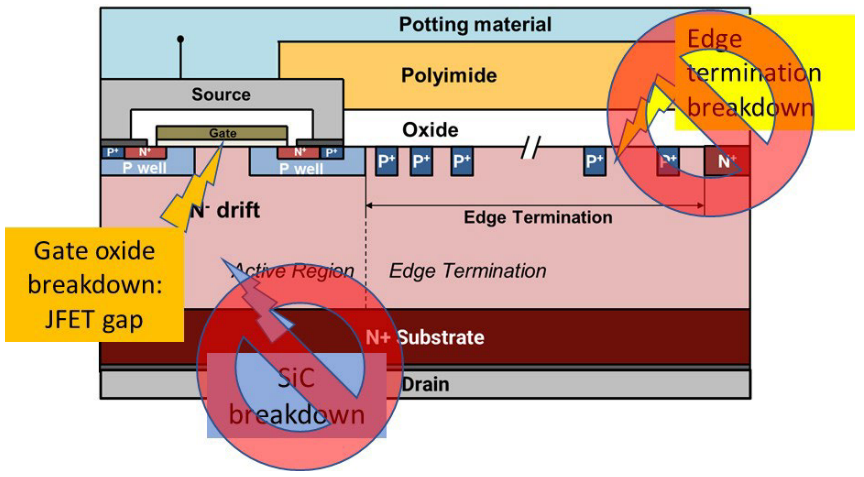

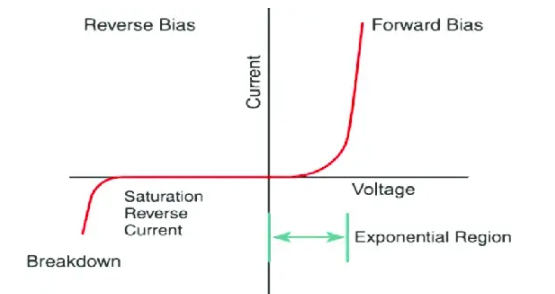

在 SiC 器件中觀察到的一些失效機制與在 Si 器件中觀察到的類似,例如單粒子燒毀(SEB,由于地球中子)和柵極氧化物磨損。SiC MOSFET 顯示偏置溫度不穩定性 (BTI) 退化機制,具有與 Si MOSFET 類似的加速因子和時間依賴性。然而,由于界面和近界面電荷陷阱的密度較高,SiC 器件中的 BTI 可能更加突出,因此需要更徹底地表征 BTI 響應,包括表征閾值電壓 (VT) 的特殊技術。SiC MOSFET 很容易受到雙極退化(增加的導通電阻和可能的泄漏),這是由于在第三象限操作中發生的電子空穴復合的影響下基面位錯 (BPD) 轉化為堆垛層錯。這種雙極退化機制是 SiC 所獨有的,需要新穎的可靠性表征。值得注意的是,觀察結果與雙極退化是一種早期故障率 (ELFR) 機制而不是內在磨損一致,因為只有預先存在 BPD 的設備才會經歷雙極退化。通過表征這些機制,可以構建完整的可靠性“浴缸曲線”,其中表示早期壽命故障率/“嬰兒死亡率”(雙極穩定性)、使用壽命期間的恒定(隨機)故障率(SEB 和隨機潛在缺陷)產品生命周期的磨損(柵極氧化、VT 穩定性和封裝)階段。本文中顯示的可靠性數據來自 Wolfspeed Gen3 SiC 平面 MOSFET,其顯著特征如圖 1 所示。這些可靠性考慮因素通常也適用于溝槽 MOSFET,盡管其中一些影響的存在和嚴重程度可能有所不同。

圖 1. Wolfspeed SiC 平面 MOSFET 原理圖平面圖、橫截面、顯著特征和代表性故障機制。

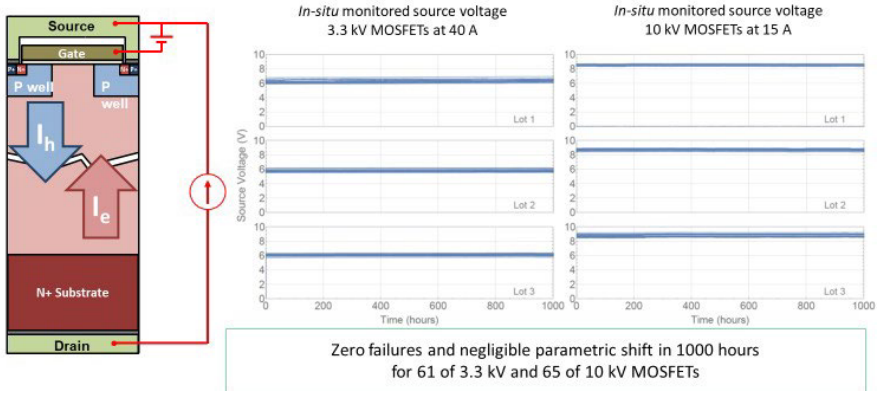

雙極穩定性。基面位錯 (BPD) 處的復合增強堆垛層錯 (SF) 滑移對 SiC MOSFET 中 4H-SiC 雙極器件的可靠運行提出了基本的材料挑戰。這種情況的發生會導致電阻增加和泄漏。然而,現代 4H-SiC 襯底生產實踐已導致基面位錯密度大幅降低,當與適當的生產篩選方法相結合時,可以實現具有極低 BPD 密度的可靠器件,因此該機制的故障率較低。幾乎不關心兩極穩定。雙極性穩定性可以通過體二極管工作壽命(BDOL)應力測試來驗證,在該測試中,恒定電流施加于第三象限模式下的MOSFET。具有足夠的散熱和/或占空比,以將結溫保持在最大額定值內。例如,Wolfspeed, Inc. 發布了額定值為 3.3 kV 和 10 kV 的中壓器件的 BDOL 結果,來自 3 個生產批次的每種類型樣品超過 60 個器件,在 BDOL 應力之前和之后零故障且參數變化可忽略不計(圖. 2)。這一結果成功地證明了生產 MOSFET 的出色雙極穩定性,這可能被認為比低壓器件(例如 (650 – 1200) V)更嚴格,因為 SiC 外延層更厚,因此更有可能發生故障。存在基底面位錯。

圖 2.(左)BDOL 應力配置示意圖、MOSFET 有源單元橫截面以及導致 BPD 轉換為 SF 的電子-空穴復合電流指示(右)3.3 kV 和 10 kV Wolfspeed 資格測試的 BDOL 電流與時間的關系中壓生產 SiC MOSFET。

值得注意的是,如果 SiC MOSFET 一開始就沒有任何 BPD,那么 SF 就無法成核和生長,并且不會發生雙極退化。因此,減少和篩選BPD的發生對于確保SiC MOSFET的第三象限雙極穩定性非常重要。盡管進行了數十年的研究,文獻證據尚未表明如何以良好的方式加速雙極穩定性,以便構建預測壽命模型,例如柵極氧化物磨損模型。幸運的是,大多數或所有雙相穩定性故障發生在相對較短的時間內(BDOL 壓力的幾小時到幾天,而不是幾個月和幾年)。因此,雙極穩定性似乎最好采用早期故障率機制,而不是磨損機制。因此,為了確保采用第三象限操作的應用具有良好的雙極穩定性可靠性,制造商必須依靠低 BPD SiC 外延和充分的篩選,并通過測試大樣本量和大面積器件來證明這一點,幸運的是,測試周期相對較短。BDOL 壓力時間。

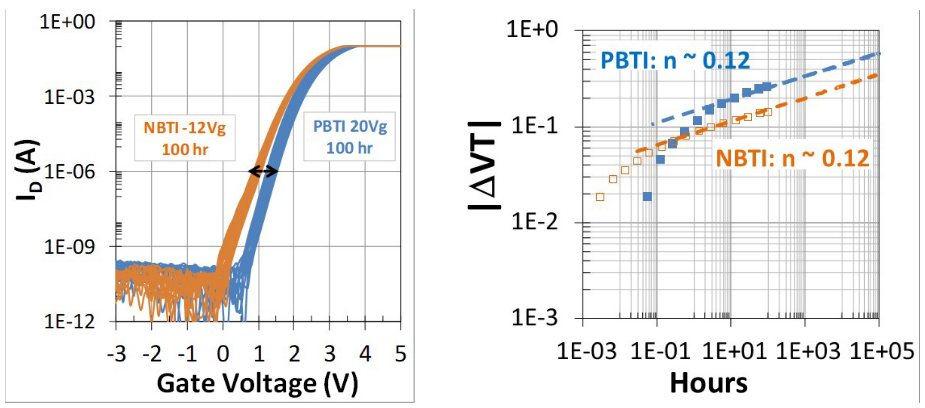

閾值電壓穩定性。柵極偏置會導致 SiC MOSFET 的 VT 穩定性隨時間漂移,從而改變器件的導通狀態和/或阻斷特性。這種效應通常稱為正/負偏壓溫度不穩定性 (PBTI/NBTI)。BTI 可以發生在 Si 以及 SiC MOSFET 中,但這種效應通常在 SiC MOSFET 中更為明顯,因為它們在氧化物界面處及其附近具有更高密度的陷阱,這些陷阱由氧化物電場填充、清空和/或創建。BTI會受到電場和溫度的加速,并隨時間呈現出弱冪律。Lichtenwalner 等人對生產 SiC MOSFET 中 BTI 的示例性表征。顯示出約 0.12 的時間指數(圖 3),這與具有氮化氧化物的 Si 器件(如 SiC)的時間指數相似。這種相似性表明 SiC 和 Si 器件的物理機制是相同的,即氧化物電荷陷阱填充和排空。壽命外推表明,BTI 預計在數千小時內僅漂移數百毫伏,但值得注意的是,與PECS應用中此類器件的典型開關電壓相比,即使如此大的漂移也很小,因此預計不會明顯影響系統性能。

圖 3. 代表性 Wolfspeed Gen3 1200 V SiC MOSFET 的 BTI。(左)在長達 100 小時的累積恒定柵極偏壓應力的應力時間內,漏極電流與柵極電壓曲線隨恒定柵極偏壓而漂移,并具有中間讀出點。PBTI 和 NBTI 的外推預測,在 150 °C 下加速恒定柵極偏置應力數千小時時,漂移僅為數百毫伏。

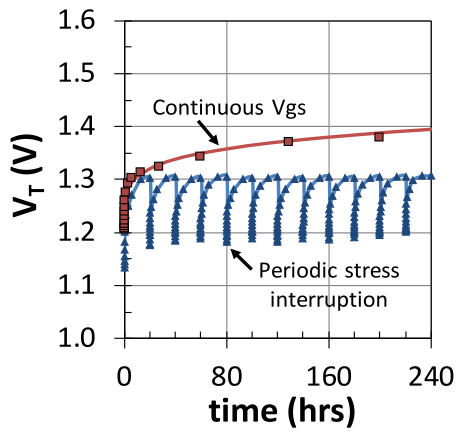

值得注意的是,在柵極偏置應力下觀察到的VT漂移可以由長期VT漂移、瞬態VT變化和VT滯后或滯后變化組成。為了證明這種效應,圖 4 顯示了與中斷偏壓相比,恒定柵極偏壓下 VT 如何隨時間漂移,其中定期消除應力,并且允許器件在恢復應力之前松弛。這些行為之間的差異表明可恢復瞬態效應占主導地位,并且由界面退化引起的 VT 漂移相對較小。這說明在恒定柵極偏壓應力下觀察到的 VT 漂移有多少可能并不代表器件永久性退化,而是反映了臨時參數漂移,這在典型開關應用中可能不太明顯。

圖 4. Wolfspeed Gen3 900 V SiC MOSFET 的 VT 與柵極偏置應力時間關系,顯示了 150 °C 下連續 19 V 應力下的 PBTI,與定期消除應力時的 VT 響應進行了比較。這種差異表明可恢復瞬態效應占主導地位。

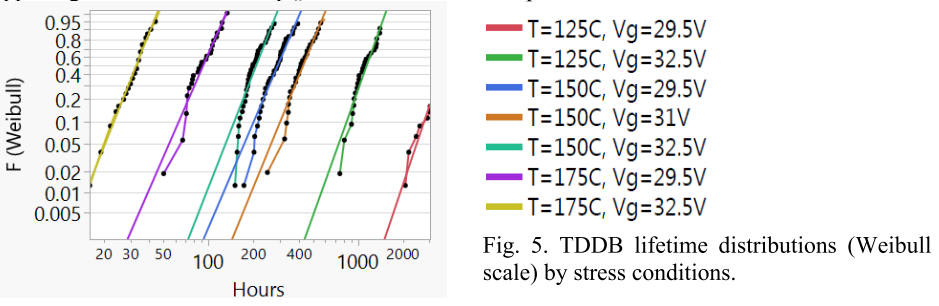

柵極氧化層磨損。SiC MOSFET 柵極氧化物磨損通過時間相關介電擊穿 (TDDB) 測試來表征。Wolfspeed Gen3 1200 V MOSFET 上的 TDDB 數據通過具有高 Weibull beta 值的單個 Weibull 統計分布進行了很好的建模,這表明即使在高度加速條件下也具有良好的內在磨損行為,并且沒有明顯的外在缺陷群(圖 5)。熱化學模型(方程 1)很好地描述了 TDDB 數據與溫度和柵極電壓的關系,該模型已廣泛用于 Si MOSFET,

其中 E 是柵極氧化物電場,T 是溫度,ΔH0 是零施加柵極電場時的 Si-O 鍵強度,peff 是有效 Si-O 偶極矩。

圖 5. 按應力條件劃分的 TDDB 壽命分布(威布爾標度)。

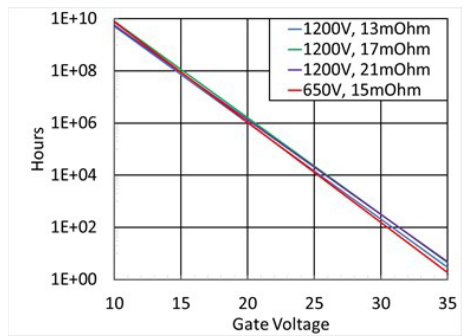

將此模型應用于多個 1200 V 和 650 V 完整生產器件,可得出所有器件在 175 °C、15 V 連續柵極偏壓下的固有壽命預測約為 1E8 小時。這表明 Wolfspeed 器件的柵極氧化物壽命對于不同尺寸和電壓等級是一致的(圖 6),由于柵極結構和晶圓制造工藝的相似性,這是預期的。所得模型擬合參數與 Si 器件的相似,這表明 SiC 和 Si MOSFET 的柵極氧化物磨損機制相似。

圖 6. 多個 Gen3 1200 V 和 650 V SiC MOSFET 的 TDDB 固有壽命外推。

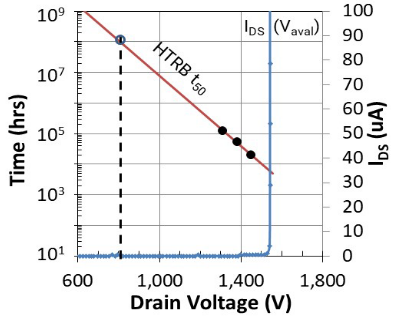

高溫反向偏壓 (HTRB)。在某些器件設計屬性允許的情況下,SiC MOSFET 在阻斷條件下的壽命可以通過加速 HTRB 測試 (ALT-HTRB) 來表征。SiC MOSFET 在雪崩電壓下表現出相對較低的漏電。器件的設計通常在雪崩電壓和器件的額定電壓之間留有一定的余量,以確保針對高漏極偏置電壓(尤其是瞬態過壓)的可靠性和魯棒性。該裕度可以在高于額定電壓但低于雪崩電壓的情況下加速漏極偏置測試。在這種情況下,器件 JFET 間隙中的氧化物電場可能足夠高,足以引起柵極氧化物磨損。恒定偏壓 ALT-HTRB 測試表明,器件顯示相對較低的柵極和漏極泄漏,直到發生突然的柵源短路故障,幾乎沒有前兆信號,類似于 TDDB 中發生的情況。

圖 7.(左軸)150 °C 下 ALT-HTRB 壽命中值與漏極偏置的關系,外推至 800 V 下約 1E8 小時。(右軸)代表性器件的漏極電流與電壓的關系,顯示雪崩電壓 > 1450V。

圖 7 顯示了 Wolfspeed Gen3 1200 V SiC MOSFET 的 ALTHTRB 測試結果。ALTHTRB 壽命數據使用 Weibull 統計數據和線性 V 模型進行擬合,如上文針對 TDDB 所述。結果表明,在 175 °C 和 800 V(這是典型高可靠性 PECS 應用中經常使用 1200 V 器件的總線電壓)下,預計平均壽命約為 1E8 小時。

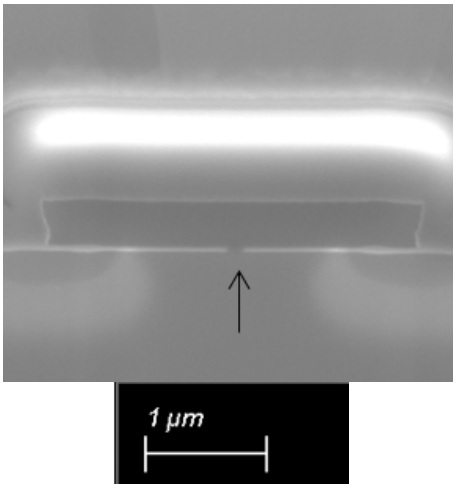

圖 8. 在 ALT-HTRB 應力測試中已達到壽命終點的 Wolfspeed SiC MOSFET 失效部位的 FIB 橫截面的掃描電子顯微鏡圖像。箭頭突出顯示了加速壽命應力測試期間發生的氧化物擊穿的位置。

失效分析表明,ALT-HTRB 失效機制是 JFET 間隙中心的柵極氧化層擊穿(圖 8)。這是預料之中的,因為這是反向偏壓下柵極氧化物電場最高的位置。失效分析沒有發現邊緣終端擊穿或 SiC 擊穿的證據(圖 9),這表明柵極氧化物磨損是影響反向偏壓可靠性的唯一失效機制。這支持使用線性 V(在本例中為漏極電壓,與柵極電壓直接相關)模型進行 ALT-HTRB 壽命預測,如上所述。

圖 9. Wolfspeed SiC 平面 MOSFET 的橫截面示意圖,表明故障分析表明 ALT-HTRB 應力期間發生的唯一故障機制是柵極氧化物擊穿,而不是邊緣終端擊穿或 SiC 擊穿。

標準化

SiC PECS 器件的這些有趣的可靠性方面一直在推動行業聯盟緊急發布可靠性測試和鑒定的指南和標準,盡管方法論正在積極開發并且新數據正在發布。國際電工委員會(IEC)發布了關于雙極退化和偏置溫度不穩定性的國際標準可靠性測試方法文件。JEDEC 已發布有關偏置溫度不穩定性評估的文件、測量 SiC MOSFET 的閾值電壓、代表數據表中 SiC MOSFET 的開關損耗,以及最近用于評估 dV/dt 魯棒性的文件。歐洲電力電子中心 (ECPE) 修訂了其關于機動車輛電力電子轉換器單元中使用的功率模塊資格的文件,現在包含關于基于 SiC 的功率模塊資格的附件部分,其中包括功率循環的具體指南、高溫柵極偏壓、高溫反向偏壓、動態反向偏壓等。

即使對這些文件進行粗略的審查也表明,這些聯盟之間尚未在可靠性壓力程序的某些主要方面達成一致,當然也沒有在 AEC-Q101 或 JEDEC JESD47K 等標準資格指南方面實現一致。然而,可以肯定的是,這些和其他行業聯盟將繼續非常積極地致力于修訂現有的 SiC PECS 指南和標準并發布新的指南和標準。JEDEC 小組委員會 JC-70.2“SiC 電力電子轉換半導體標準”正在積極制定有關雙極穩定性、柵極氧化物可靠性和 HTRB 的文件。從歷史上看,標準組織首先發布指南,然后發布標準。這種做法的優點是,首先更容易就指南達成廣泛共識,然后可以作為調整標準(例如資格)的基礎。在制造商和客戶之間實現廣泛的一致具有挑戰性,但對于建立信心至關重要,因為 SiC 繼續在高可靠性和大批量應用中令人印象深刻地廣泛采用。

總結

高可靠性應用中對 SiC PECS 器件的需求快速增長,加上 SiC 中的高芯片數量、惡劣的工作條件和獨特的可靠性考慮因素,導致對徹底的可靠性表征和行業聯盟標準化的需求非常高。SiC 的關鍵失效機制,包括 BTI、雙極穩定性和柵極氧化物(在柵極偏壓和反向偏壓下),已被制造商和其他研究人員充分表征。在應力程序、壽命建模和對現場可靠性影響的協調方面正在取得良好進展。幾個行業聯盟已經發布了許多指南和標準,并且很快還會發布更多指南和標準。下一個挑戰將是這些聯盟之間更廣泛的協調——需要做更多的工作,而且即將完成。

審核編輯:湯梓紅

-

MOSFET

+關注

關注

147文章

7156瀏覽量

213142 -

半導體

+關注

關注

334文章

27286瀏覽量

218073 -

肖特基二極管

+關注

關注

5文章

927瀏覽量

34805 -

功率器件

+關注

關注

41文章

1758瀏覽量

90416 -

SiC

+關注

關注

29文章

2804瀏覽量

62606

原文標題:SiC 功率器件的可靠性和標準化

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么是失效分析?失效分析原理是什么?

未來發展導向之Sic功率元器件

SiC功率器件概述

淺析SiC功率器件SiC SBD

SiC功率器件SiC-MOSFET的特點

【羅姆SiC-MOSFET 試用體驗連載】SiC MOSFET元器件性能研究

SiC器件中SiC材料的物性和特征,功率器件的特征,SiC MOSFET特征概述

SiC功率器件中的失效機制分析

SiC功率器件中的失效機制分析

評論