集成電路發(fā)展趨勢

隨著物聯(lián)網(wǎng)移動終端的需求日益增長,對便攜式設(shè)備與長續(xù)航能力的追求促使低電壓和低功耗的芯片設(shè)計變得尤為重要。降低電路功耗而不犧牲其他性能指標是設(shè)計中的一大挑戰(zhàn)。因此,想盡辦法”壓榨“電路中未能完全利用的電流,從而提高電流效率成為一種低功耗的設(shè)計思路。

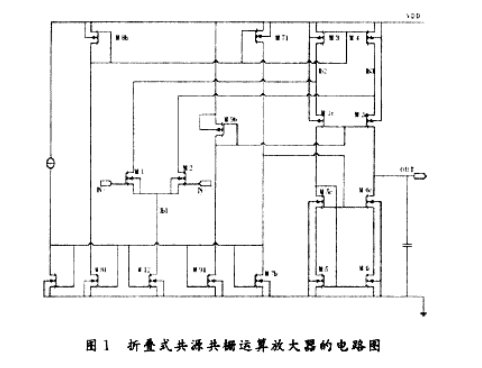

折疊式共源共柵運算放大器

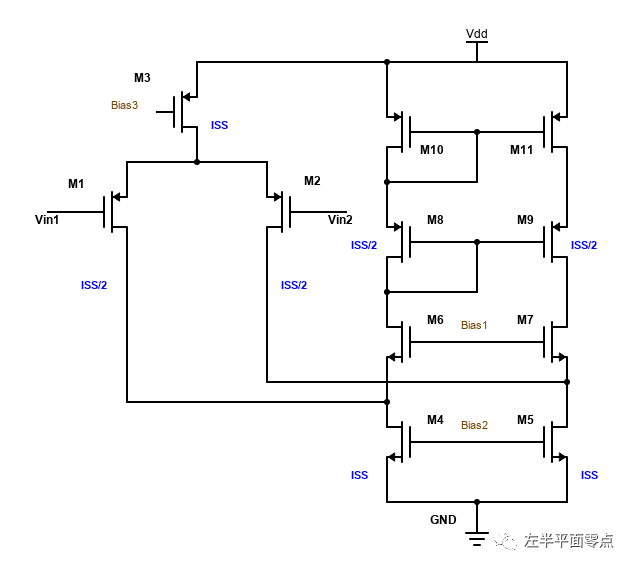

圖1先看我們熟悉的折疊式共源共柵放大器,如圖1。其中M4、M5作為電流源均提供了ISS大小的電流。但M4、M5僅充當電流源的角色,大電流的特點雖使得M4、M5本身有很大的跨導(dǎo),但無法作用到增益上,造成電流的”浪費“。

電流倍增技術(shù)

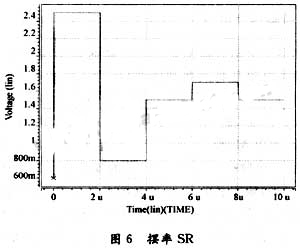

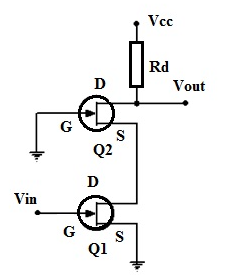

圖2

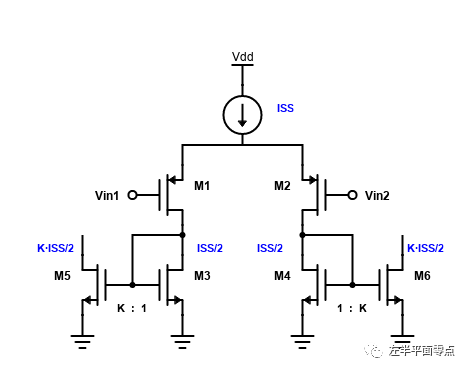

如圖2,該電路實現(xiàn)了電流倍增:M3-M6組成了兩對電流鏡,將電流倍增至K倍。如果單純通過這樣的電流鏡進行倍增后,再接上后級負載,等效跨導(dǎo)確實大了,但這不是多了兩路K倍的電流嗎?功耗反而增大了 ......貌似好像沒什么用哦?別急,妙的在后面。

圖3

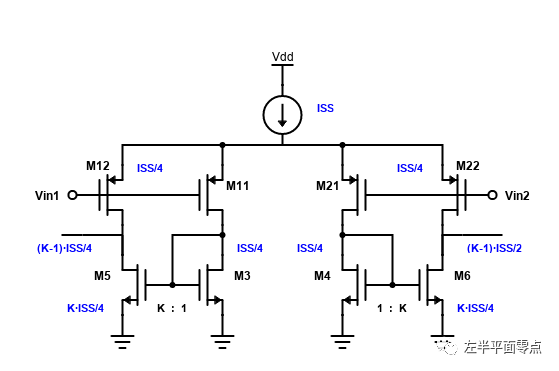

如圖3,稍微改一下輸入差分對M1、M2,把他倆拆成四個晶體管分別為M11、M12、M21、M22。現(xiàn)在,每個差分晶體管的電流均為ISS/4。再通過電流鏡將差分晶體管”耦合“起來,形成反饋。現(xiàn)在,M11、M21通過電流鏡實現(xiàn)了倍增了K倍的小信號電流,因此M11、M21的等效跨導(dǎo)也倍增了K倍。

圖4

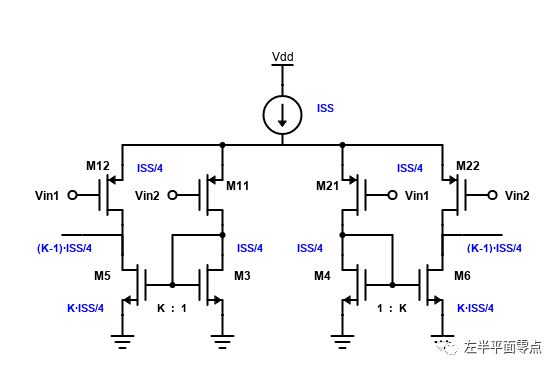

但往往實際上不會使用圖3的接法(可以想想為什么),比較好的是圖4的接法。嘶......這有區(qū)別嗎?兄dei你是不是放錯圖了?看清楚咯,Vin1與Vin2接哪里去啦?終于看到了?沒錯,這是一種交叉耦合的方式。同樣,M11、M21的等效跨導(dǎo)倍增了K倍。假設(shè)差分晶體管均具有相同的尺寸,并且設(shè)其自身跨導(dǎo)為gm,那么整個電路的等效跨導(dǎo):

Gm=gm+K·gm=(1+K)·gm

沒有采用電流復(fù)用技術(shù)的原電路的跨導(dǎo)僅僅為2gm,而采用電流復(fù)用技術(shù)后,通過調(diào)整不同的電流鏡比例,可以實現(xiàn)不同倍數(shù)的等效跨導(dǎo)。假設(shè)取K=3,那么電路的等效跨導(dǎo)與原來相比倍增了2倍,而電路總的電流卻沒有變化,仍然是2ISS。所以說,電流復(fù)用技術(shù)提高了電路的電流效率,狠狠地"壓榨"電流!

當然啦,這個電路最后有了增益帶寬積、轉(zhuǎn)換速率等等指標的提升,但功耗沒有變化,代價就是電路的復(fù)雜程度上升、版圖面積增加、對匹配的要求更高等等。

-

運算放大器

+關(guān)注

關(guān)注

215文章

4964瀏覽量

173343 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1026瀏覽量

54960 -

低功耗

+關(guān)注

關(guān)注

10文章

2417瀏覽量

103822 -

共源共柵

+關(guān)注

關(guān)注

0文章

23瀏覽量

10392

發(fā)布評論請先 登錄

相關(guān)推薦

一種低壓低功耗CMOS折疊-共源共柵運算放大器的設(shè)計

折疊共源共柵運算放大器原理及設(shè)計

增益增強共源共柵放大器的設(shè)計

折疊式共源共柵運算放大器電路分析

折疊式共源共柵運算放大器電路分析

評論