SDF文件是在VCS/NC-Verilog后仿真運行時將STD/IO/Macro門級verilog中specify的延遲信息替換為QRC/Star-RC抽取的實際物理延時信息,所以如果SDF文件的條件信息在verilog的specify中沒有的話,就會報SDFCOM_INF的warning,意思是IOPATH not found。

本文解析SDF的Header Section信息、Cell Entries信息,尤其重點講解Cell Entries的Delay Entries信息。

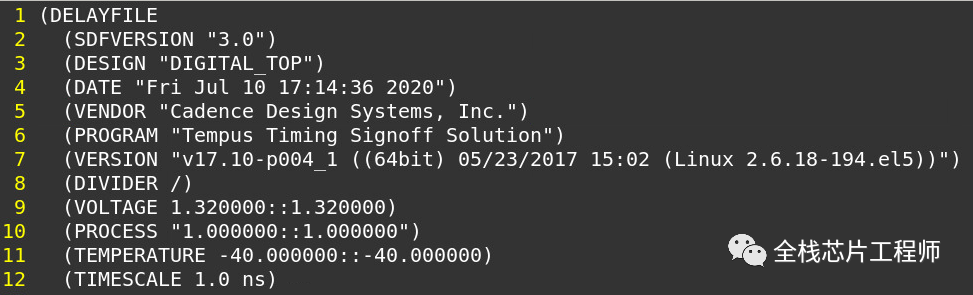

下文先講SDF文件的第一部分Header Section

SDF Version Entry,包括1.0、2.1、3.0,SDF3.0是1995年release。

Design Name Entry,設計頂層名

Date Entry,SDF生成日期,PT或Tempus產生

Vendor Entry,Vendor信息,如下圖

Program Version Entry

Hierarchy Divider Entry

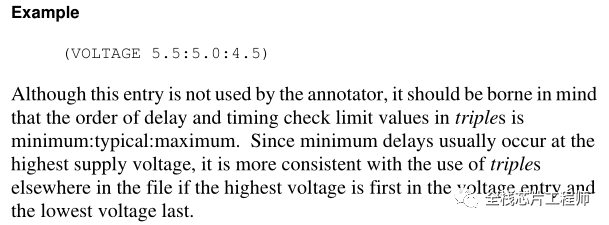

Voltage Entry,SDF3.0官方解釋如下

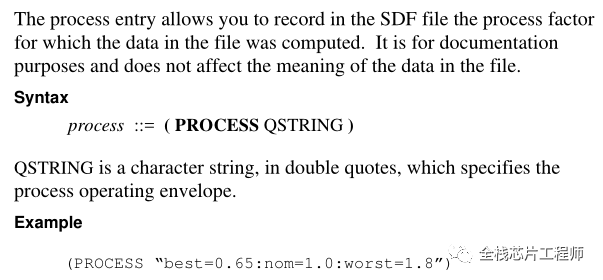

Process Entry,SDF3.0官方解釋如下

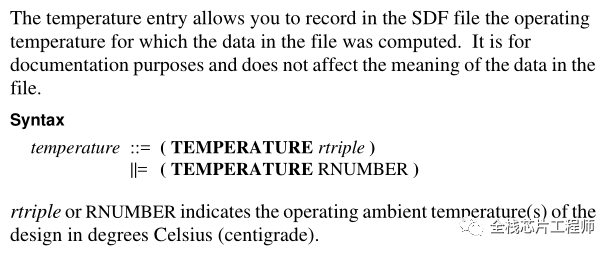

Temperature Entry,SDF3.0官方解釋如下

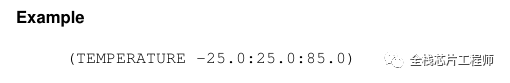

Timescale Entry,SDF3.0官方解釋如下

下文繼續講解SDF文件的第二部分Cell Entries:

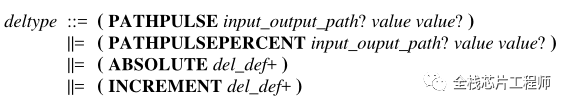

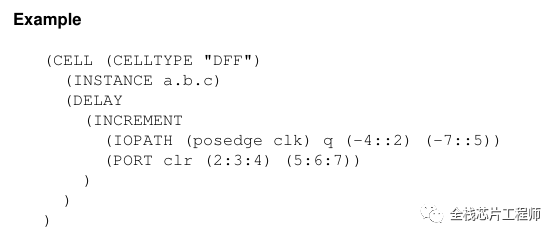

完整的Delay Entries信息格式如下:

完整的Delay Entries信息格式如下:

PATHPULSE

PATHPULSEPERCENT

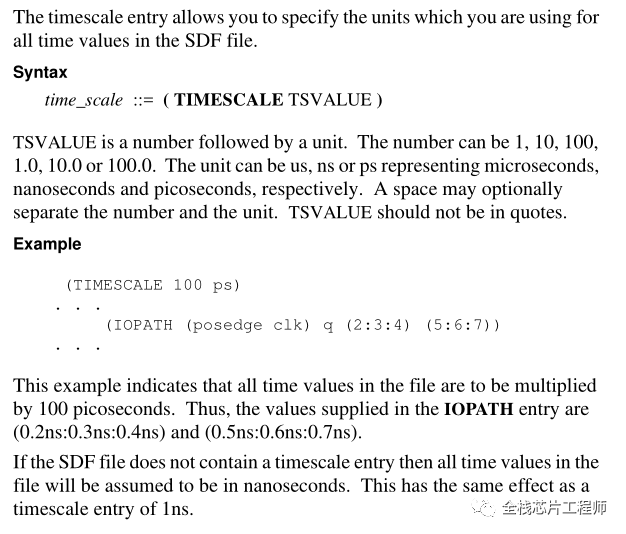

ABSOLUTE Delays

INCREMENT Delays

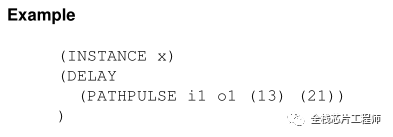

1. PATHPULSE 舉例說明:

當從i1到o1輸出的低電平脈沖小于13ns時,該低電平脈沖直接被忽略;

當從i1到o1輸出的低電平脈沖介于13ns~21ns時,輸出為X態;

當從i1到o1輸出的低電平脈沖大于21ns時,正常輸出低電平;

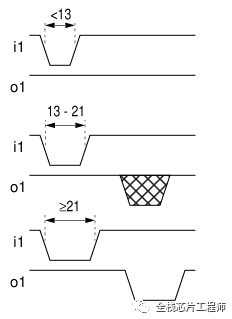

2. PATHPULSEPERCENT 本質上和PATHPULSE是一回事,只不過是按照path延時比例來計算什么時候丟棄輸入脈沖寬度不足的信號(pulse rejection limit),什么時候將輸入脈沖寬度不足的信號顯示為X態(X limit)。比如:

2. PATHPULSEPERCENT 本質上和PATHPULSE是一回事,只不過是按照path延時比例來計算什么時候丟棄輸入脈沖寬度不足的信號(pulse rejection limit),什么時候將輸入脈沖寬度不足的信號顯示為X態(X limit)。比如:

以上圖為例,the high-to-low delay is 37, 因此,the pulse

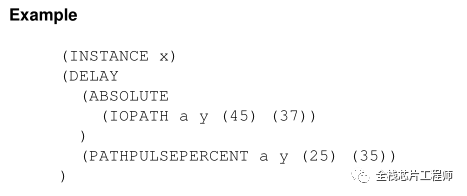

rejection limit is 25% of 37 and the X limit is 35% of 37. 3. ABSOLUTE Delays ABSOLUTE Delays中的物理延時數據就是用來替換verilog specify中的延時數據的。

4. INCREMENT Delays

用來疊加在verilog specify中的延時數據上的,INCREMENT Delays是存在負數的情況的,疊加后的延時若是負數的話,某些EDA工具可能不支持或直接強制延時為0。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50965瀏覽量

424857 -

仿真

+關注

關注

50文章

4102瀏覽量

133737 -

Verilog

+關注

關注

28文章

1351瀏覽量

110163

原文標題:芯片后仿之SDF 3.0解析(一)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

我后仿出現了10種警告。。。求助

運行后實現時序仿真后重新生成sdf文件

如何將PT產生的SDF文件反標設計進行后仿真?

NodeMCU V3.0 Arduino開發之點燈測試程序

NodeMCU V3.0 Arduino開發之點燈

STM8S全解析之系列文章3---STM8S芯片配置,軟件框架搭建

ZigBee3.0數據包解析

Python在IC中的應用——文本處理

解析SDF的Header Section信息與Cell Entries信息

詳解芯片SDF文件 MCU芯片全流程設計

芯片后仿真要點

芯片后仿之SDF 3.0解析

芯片后仿之SDF 3.0解析

評論