電氣系統(tǒng)中電源分配網(wǎng)絡(luò)(PDN)的各個(gè)部分都有自己的環(huán)路電感,這將增加電路結(jié)構(gòu)的總阻抗。

各種元件的環(huán)路電感會導(dǎo)致 PDN 阻抗譜中出現(xiàn)諧振和反諧振。

設(shè)計(jì)人員應(yīng)認(rèn)真計(jì)算 PDN 阻抗,以便更好地了解電源軌上的紋波。

由于擺放著器件、走線、過孔、焊盤、平面等,PCB 都具有復(fù)雜的幾何形狀。使用了多層平面、電源軌、通向器件的過孔以及去耦電容器,PCB 中的 PDN 可能相當(dāng)復(fù)雜。其中每個(gè)元素都會對結(jié)構(gòu)的總阻抗產(chǎn)生一定的 PDN 環(huán)路電感,因此,作為電源完整性設(shè)計(jì)的一部分,電感對于總阻抗的影響十分重要,值得關(guān)注。

這塊 PCB 上的 PDN 阻抗譜將非常復(fù)雜,有多個(gè)環(huán)路電感峰值

目前還無法用一個(gè)公式就能確定 PDN 環(huán)路電感或阻抗。與用公式來確定 PDN 中的電感和阻抗相比,通過測量和使用場求解器來確定這些值更為精確,有助于更好地理解 PDN 上的瞬態(tài)行為。確定這些值之后,設(shè)計(jì)人員就可以采用傳遞函數(shù)的方法來了解 PDN 阻抗,并預(yù)測不同器件產(chǎn)生的紋波噪聲。在確定阻抗之前,首先我們需要了解電感對阻抗的影響。

1

PDN 環(huán)路電感對阻抗的影響

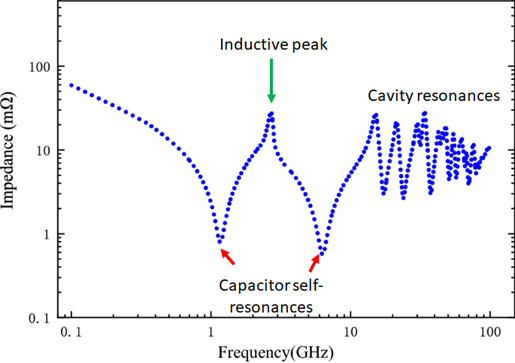

觀察一下 PDN 的阻抗譜就會發(fā)現(xiàn),它并不是一直處于低位。PDN 阻抗的頻譜非常復(fù)雜,頻率范圍廣泛,且存在多個(gè)諧振和反諧振。電容和電感是影響 PDN 阻抗的主要因素,決定了典型 PDN 阻抗譜的形狀。PDN 環(huán)路電感和電容器中的有效串聯(lián)電感 (Effective Series Inductance, ESL) 將決定阻抗譜的峰值,如圖1所示:

圖1:PDN 阻抗譜示例

觀察一下高速 PCB 中 PDN 的結(jié)構(gòu)就會發(fā)現(xiàn),一個(gè)典型的 PDN 結(jié)構(gòu)包含相鄰的電源和接地平面,它們就像一個(gè)超大型電容器。相鄰平面的電容和電路板上的去耦電容共同構(gòu)成了一個(gè)大型電荷庫,可在開關(guān)期間向數(shù)字元件提供電荷。但不要忽略 PDN 結(jié)構(gòu)中的某些電感源,它們會產(chǎn)生圖1中顯示的諧振。這些電感源包括:

電容器中的有效串聯(lián)電感,在高頻時(shí)會產(chǎn)生電容器自諧振和非理想行為。

過孔和走線,它們有自己的環(huán)路電感。

電源平面和接地平面的組合。

器件上的連接線和焊盤,它們有自己的阻抗,會在器件輸入端造成引腳封裝延遲。

在設(shè)計(jì) PDN 的阻抗時(shí),我們的目標(biāo)不是計(jì)算單個(gè)電感并試圖達(dá)到特定的設(shè)計(jì)值,而是確定在哪些位置添加去耦電容,有效針對阻抗譜中的特定峰值,從而保持整體阻抗較低。通過將 PDN 阻抗保持在較低的水平,可將電源總線上的紋波電壓控制在可接受的范圍內(nèi)。

此外,還需要對阻抗進(jìn)行量化,并預(yù)測阻抗對電源總線上的瞬態(tài)紋波響應(yīng)有何影響。為此,可以通過測量標(biāo)準(zhǔn) PDN 阻抗和計(jì)算脈沖響應(yīng)來實(shí)現(xiàn)。

2

測量 PDN 阻抗

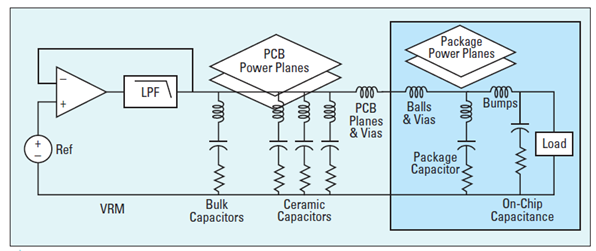

如下列電路圖所示,PDN 的結(jié)構(gòu)實(shí)際上是一組并聯(lián)的非理想電容器,它們通過寄生電感連接在一起。這種現(xiàn)象模型的阻抗無需計(jì)算,可以在測試板上通過 TDR 測量、脈沖響應(yīng)測量或網(wǎng)絡(luò)分析儀(Z 參數(shù)或 S 參數(shù))進(jìn)行測量。

用于描述 PDN 阻抗的電路模型示例。[來源:Signal Integrity Journal《信號完整性期刊》]

只有電容器中的元素是已知的,其他電感器元素則代表 PDN 環(huán)路電感。實(shí)際情況中,在上述模型中確定具體電感值毫無意義。只要明確阻抗譜,設(shè)計(jì)人員就可以放置一個(gè)自諧振頻率與阻抗譜中的電感峰值相匹配的去耦電容器。

3

預(yù)測 PDN 上的瞬態(tài)波形

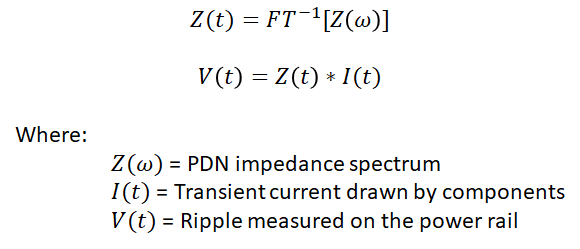

確定 PDN 阻抗后,就可以使用卷積定理計(jì)算 PDN 上的脈沖響應(yīng)。為此,只需知道 PDN 阻抗譜函數(shù)和輸入 PDN 的瞬態(tài)電流時(shí)域波形(通常以方波形式建模)。可通過以下傅立葉變換和卷積積分來定義:

計(jì)算開關(guān)期間在 PDN 上測量到的紋波電壓的脈沖響應(yīng)。注意"*"是卷積運(yùn)算

4

計(jì)算 PDN 環(huán)路電感與阻抗的方法

我們無法使用公式來確定 PDN 的總環(huán)路電感,也不能簡單地將 PDN 建模為只有一個(gè)等效環(huán)路電感。因此,也不能使用 SPICE 仿真直接根據(jù) PDN 的結(jié)構(gòu)和 PCB layout 來計(jì)算 PDN 阻抗;因?yàn)檎麄€(gè)系統(tǒng)的幾何結(jié)構(gòu)非常復(fù)雜。PDN 的復(fù)雜結(jié)構(gòu)會產(chǎn)生一個(gè)非常高階的濾波器,這不僅僅是一個(gè)具有多個(gè)極點(diǎn)和零點(diǎn)的大型 RLC 電路。雖然阻抗是決定 PDN 電源總線紋波的重要因素,但不能簡單地認(rèn)為阻抗可以直接計(jì)算,這是一種錯(cuò)誤的電源完整性設(shè)計(jì)方法。

正確做法是直接根據(jù)麥克斯韋方程計(jì)算電磁場、電勢和電流,并使用歐姆定律計(jì)算 PDN 阻抗。要獲得阻抗譜,需要使用有限差分頻域 (Finite-difference Frequency Domain, FDFD) 數(shù)值方法,并將歐姆定律與計(jì)算出的電勢和電流相結(jié)合,得出 PDN 阻抗。高級的 PCB layout 工具會提供一個(gè)功能強(qiáng)大的 3D 電磁場求解器,可用于執(zhí)行這些計(jì)算以及電氣系統(tǒng)中其他的重要分析任務(wù)。

Cadence Allegro X 軟件中集成了Clarity 3D Solver 工具,這是一款 3D 電磁(EM)仿真軟件工具,用于設(shè)計(jì) PCB、IC 封裝和 IC(SoIC)系統(tǒng)設(shè)計(jì)的關(guān)鍵互連。Clarity 3D Solver 采用領(lǐng)先的分布式多重運(yùn)算技術(shù),能夠提供近乎無限制的求解容量和 10 倍的求解速度,從而高效解決更龐大、復(fù)雜的結(jié)構(gòu)問題。它創(chuàng)建的高精度 S 參數(shù)模型,可用于高速信號完整性 (SI)、電源完整性 (PI)、高頻射頻/微波應(yīng)用和電磁兼容性 (EMC) 分析,甚至在 112Gbps+ 的數(shù)據(jù)傳輸速度上,其仿真結(jié)果與實(shí)際測量也能高度吻合。更可以根據(jù)設(shè)計(jì)規(guī)模的大小,有效匹配可用的計(jì)算資源,實(shí)現(xiàn)真正的整體 3D 結(jié)構(gòu)設(shè)計(jì)。

-

電感

+關(guān)注

關(guān)注

54文章

6136瀏覽量

102298 -

紋波

+關(guān)注

關(guān)注

6文章

153瀏覽量

20697 -

PDN

+關(guān)注

關(guān)注

0文章

83瀏覽量

22703

發(fā)布評論請先 登錄

相關(guān)推薦

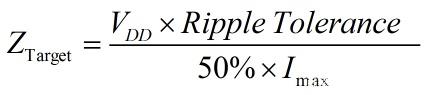

電源分配網(wǎng)絡(luò)(PDN)與目標(biāo)阻抗的計(jì)算方法

搞定電源完整性,不如先研究PDN!

電容電感對EMC有何影響?

輸出電壓紋波來源和抑制

PDN設(shè)計(jì)的目的

PDN設(shè)計(jì)

什么是電感的直流電阻呢?電感的直流電阻與交流電阻有何關(guān)系?

PDN 元件對阻抗的影響

PDN 環(huán)路電感對紋波和總阻抗有何影響?

PDN 環(huán)路電感對紋波和總阻抗有何影響?

評論