如何優(yōu)化晶振布局與連接

晶振是電子設(shè)備中常見的元件之一,用于提供時鐘信號和穩(wěn)定的頻率參考。在進(jìn)行晶振布局和連接時,需要考慮一系列的因素以確保其工作穩(wěn)定可靠。本文將詳細(xì)介紹如何優(yōu)化晶振布局和連接,從而提高系統(tǒng)的性能和可靠性。

一、晶振布局優(yōu)化

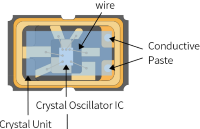

1. 位置選擇:晶振應(yīng)盡量靠近主要使用它的電路,縮短傳輸距離,減少信號的干擾和損耗。同時應(yīng)盡量遠(yuǎn)離干擾源,如高頻電路、開關(guān)電源等。

2. 地址線和控制線的分離:保持晶振的引腳布局遠(yuǎn)離地址線和控制線,避免共享引腳帶來的干擾。

3. 引腳長度匹配:如果晶振的輸出和輸入信號線長度不匹配,可能會導(dǎo)致信號失真和干擾。盡量確保輸入和輸出信號的引腳長度相等,或者采用地線匹配方式來緩解這個問題。

4. 地線布局:晶振的地線應(yīng)盡量短而粗,與晶振引腳連接處的地線應(yīng)連接到主系統(tǒng)的地線上,以確保良好的地線連接和減少地線回流帶來的噪聲干擾。

二、晶振連接優(yōu)化

1. 降低噪聲:使用低噪聲設(shè)計的晶振可以減少接收到的干擾信號,提高設(shè)備的可靠性。選擇低噪聲晶振和降低其供電線和引腳與其他高頻信號線的交叉和共享,可有效減小噪聲。

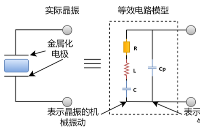

2. 使用濾波電路:在晶振的供電線上添加適當(dāng)?shù)臑V波電路,可以有效地濾除電源線上的高頻噪聲。濾波電路可以采用電容、電感等元件構(gòu)成,使得晶振供電線更穩(wěn)定,減少噪聲干擾。

3. 引腳復(fù)用:為了節(jié)省空間和降低成本,有時候需要將晶振引腳與其他功能引腳共享。在設(shè)計時,需特別注意共享引腳的電氣特性和信號干擾,避免共享引腳帶來的問題對晶振產(chǎn)生影響。

4. 連接線路保護(hù):晶振連接線應(yīng)采用合適的線材和布線方式,避免線路的過長、過細(xì)、過曲折造成的信號衰減和噪聲干擾。使用屏蔽電纜可以有效避免外部電磁干擾的影響。

三、系統(tǒng)測試和優(yōu)化

1. 穩(wěn)定性測試:在最終布局和連接完成后,對系統(tǒng)進(jìn)行穩(wěn)定性測試,驗證晶振的工作是否穩(wěn)定可靠。測試過程中可以通過觀察晶振輸出的波形、頻率穩(wěn)定性和相位噪聲等參數(shù)來評估系統(tǒng)性能。

2. 噪聲測試:使用專業(yè)的測試設(shè)備對晶振進(jìn)行噪聲測試,了解其產(chǎn)生的噪聲水平和頻譜特性。如果發(fā)現(xiàn)噪聲水平較高,可以根據(jù)測試結(jié)果對晶振布局和連接進(jìn)行優(yōu)化調(diào)整。

3. 電磁兼容性測試:進(jìn)行電磁兼容性測試,確保晶振布局和連接不會引起系統(tǒng)的電磁干擾或受到外部電磁干擾。

四、注意事項

1. 參考數(shù)據(jù)手冊:在設(shè)計晶振布局和連接時,需要詳細(xì)閱讀晶振的數(shù)據(jù)手冊,了解其工作參數(shù)、引腳定義和使用要求,以便正確布局和連接。

2. 考慮環(huán)境因素:晶振的工作可受環(huán)境溫度、濕度和電磁場等因素的影響。在布局和連接時需要考慮環(huán)境因素,選擇適用于工作環(huán)境的晶振和合適的保護(hù)措施。

3. 上電和下電順序:晶振的上電和下電順序很重要,應(yīng)按照數(shù)據(jù)手冊的要求進(jìn)行操作,避免不當(dāng)?shù)纳舷码娦蛄袑д癞a(chǎn)生損害。

通過優(yōu)化晶振的布局和連接,可以提高系統(tǒng)的性能和可靠性,減少噪聲干擾和失真,保證晶振的穩(wěn)定運行。在設(shè)計過程中,要注意參考數(shù)據(jù)手冊、進(jìn)行穩(wěn)定性和噪聲測試,同時也要充分考慮環(huán)境因素和電磁兼容性。

-

濾波電路

+關(guān)注

關(guān)注

47文章

650瀏覽量

70386 -

晶振

+關(guān)注

關(guān)注

35文章

3205瀏覽量

69622 -

信號衰減

+關(guān)注

關(guān)注

0文章

57瀏覽量

9085

發(fā)布評論請先 登錄

晶振頻率測試儀 測晶振的方法有哪些 晶振測試儀

晶振家族大揭秘:從石英晶振到陶瓷晶振,各具神通

無源晶振和有源晶振的區(qū)分方法

固定頻率石英晶振有什么優(yōu)勢

晶振在pcb布局中注意事項

晶振的總頻差解析:調(diào)整頻差與溫度頻差的綜合影響

晶振的抗干擾設(shè)計:確保系統(tǒng)時鐘的穩(wěn)定性

評論