圖像降噪處理主要分為2D(空域)與3D降噪(時域/多幀),而2D降噪由于相關的實現算法豐富,效果各異,初學入門有著豐富的研究價值。理解2D降噪算法的流程,也對其他的增強算法有很大的幫助,因此本文將再啰嗦一次,詳解從均值濾波到非局部均值濾波算法的原理及實現方式。

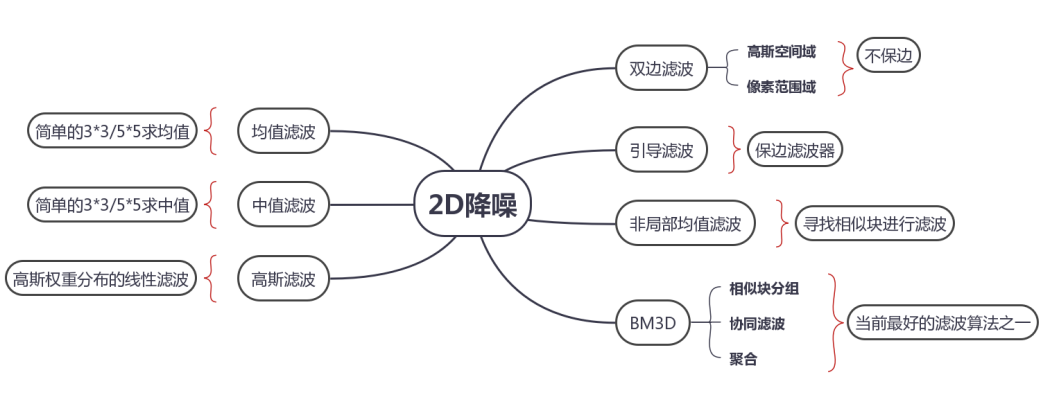

細數主要的2D降噪算法,如下圖所示,從最基本的均值濾波到相對最好的BM3D降噪,本文將盡量用最同屬的語言,詳解這些算法的實現流程,并給予一定的FPGA加速實現的實現思路。其中BM3D由于篇幅較大,后面再補上。

1.1.均值/中值濾波

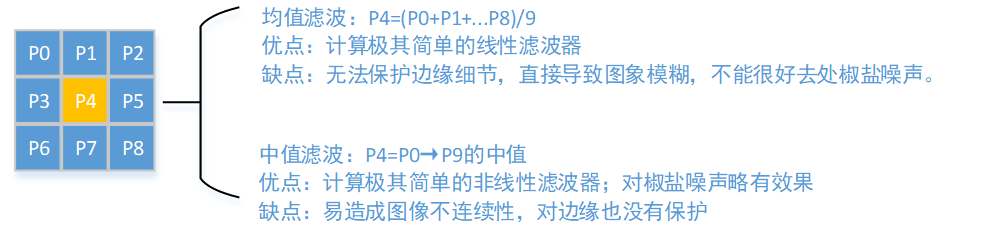

首先所有濾波算法都是通過當前像素周邊的像素,以一定的權重來計算濾波的像素值。因此主要涉及兩個變量:窗口的大小,以及窗口內像素的權重。以最簡單的均值濾波/中值濾波,3*3窗口為例,計算及優缺點如下:

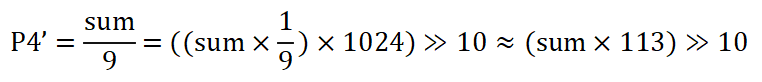

對于FPGA的硬件加速實現,過程還好,唯一頭疼的就是涉及了除法,由于除法計算時鐘周期長且耗費LE,我們需要升級改造下,因此優化公式如下(sum為9個像素累加的結果),將除法巧妙變成乘法:

因此實現的流程如下

1)sum1=P0+P1+P2; sum1=P3+P4+P5; sum3=P6+P7+P8,即先求每行3像素累加

2)sum=sum1+sum2+sum3,即求三行9像素累加

3)sum*144,取結果的[17:10],即為均值濾波的結果。

4)以上過程流水線,最終每個clk輸出一個計算結果。

備注:這里1024/9取了floor,這樣保證不會溢出。

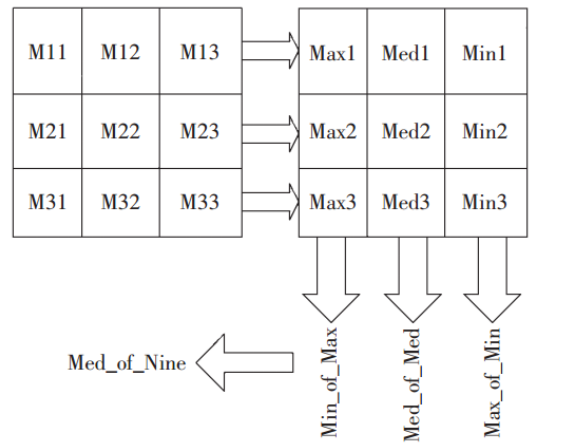

對于中值濾波而言,本身計算并不復雜,就看怎么取巧最快得到中間數,網上流傳了一個三步法,即如下圖所示,

那么FPGA硬件加速實現,流程如下:

1)計算每行3個像素的最大中、中值、最小值

2)計算三個最大值的最小值,中間值的中間值,以及最小值的最大值。

3)對上述三個值求得中間值。

4)以上過程流水線,最終每個clk輸出一個計算結果。

中值濾波計算相對均值濾波稍微復雜一點,但是好處是只用了比較器,沒用乘法器,比均值濾波更省資源。

對于椒鹽圖像的均值濾波、中值濾波計算效果對比,如下所示,分別為椒鹽圖像、均值濾波、中值濾波結果。

1.2.高斯濾波

1)

前面講的均值/中值濾波,對于窗口內每個像素的權重都是一樣的,噪聲在圖像當中常表現為一引起較強視覺效果的孤立像素點或像素塊,那么他必然不是平均分布。

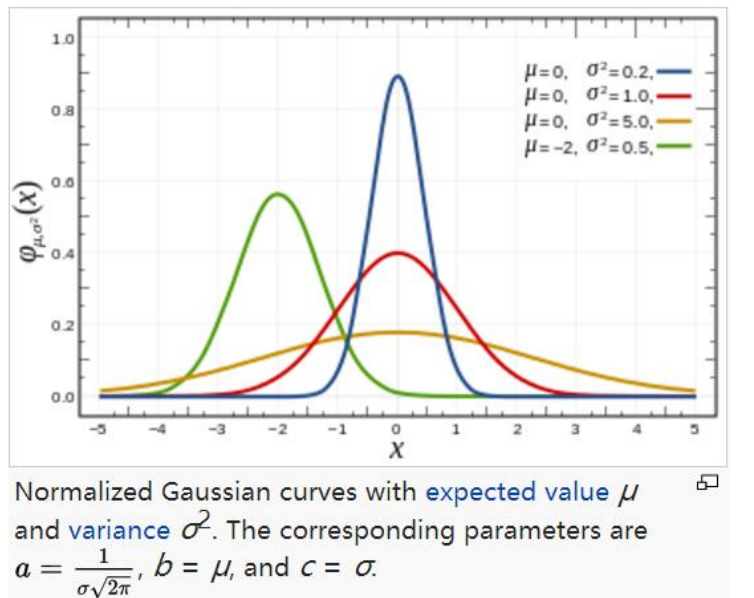

正態分布是最重要的一種概率分布,相關概念上是由德國的數學家和天文學家Moivre與1733年首次提出的,但由于德國數學家Gauss率先將其用于天文學研究,因此也叫做高斯分布。在正態分布里,人為中間狀態是常態,過高和過低都屬于少數,因此正態分布具有相當的普遍性,典型的比如升高、壽命、血壓、成績、測量誤差等都遵從正太分布。

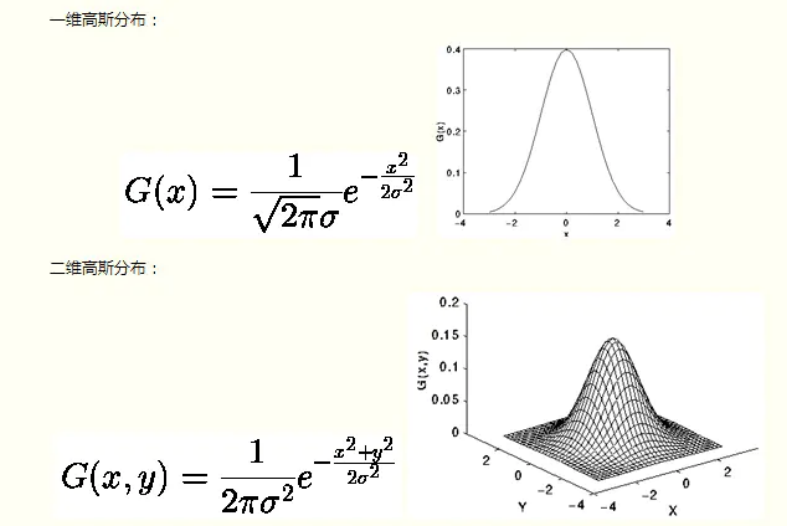

因此以概率論及中心極限定理(https://wiki.mbalib.com/wiki/中心極限定律)猜想,大部分噪聲應該也符合正態分布/高斯分布(高斯白噪聲),所以也就有了高斯濾波,及根據正態分布進行權重計算的濾波方法。上圖曲線是高斯分布的一維函數,而圖像應該是二維的,圖解如下二維高斯分布:

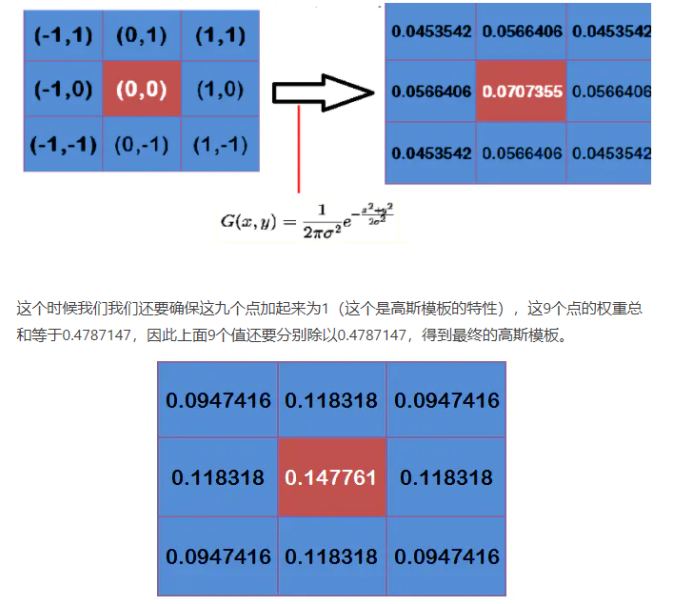

既然已經得到二維高斯分布函數,那么根據窗口到目標像素的距離,就可以是計算出周邊像素的權重——高斯模板。均值濾波每個像素的權重都是1/9,再通過卷積后計算得到結構,而高斯濾波就是根據正態分布,去計算當前像素相對距離的權重值,假定σ=1.5(σ就是濾波的強度),3*3的高斯模板計算計算過程如下:

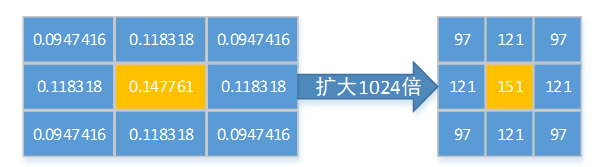

但是這還不夠,畢竟我們的目標是直接上FPGA,那必須頂定點化,因此假設擴大1024倍,則3*3的高斯模板定點化如下:

對于33或者55,選定的σ,高斯模板那么,現在計算就簡單了,卷積后再縮小1024倍即可,采用FPGA計算,過程如下:

1)計算9個像素的對應卷積參數的乘法

2)9累加9個乘法結果

3)右移10bit或取結果的[17:10],即為高斯濾波的結果。

4)以上過程流水線,最終每個clk輸出一個計算結果。

備注:當然實現還可優化,比如只用3個乘法器,算一行累加一行,也就4個時鐘算完。

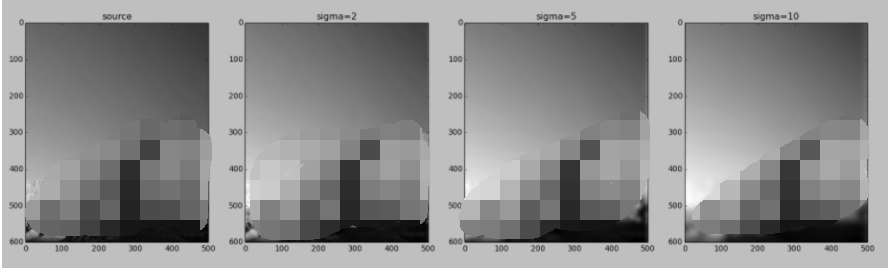

最后,暫且盜用別人針對不同σ的3*3高斯濾波效果圖,如下(σ越大越模糊):

精彩推薦 至芯科技FPGA就業培訓班——助你步入成功之路、12月30號西安中心開課、歡迎試聽! AXI總線協議總結 基于FPGA及模擬電路的模擬信號波形的實現掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:詳解從均值濾波到非局部均值濾波算法的原理及實現方式

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1645文章

22034瀏覽量

617947

原文標題:詳解從均值濾波到非局部均值濾波算法的原理及實現方式

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于Matlab與FPGA的雙邊濾波算法實現

藍牙信標RSSI濾波算法

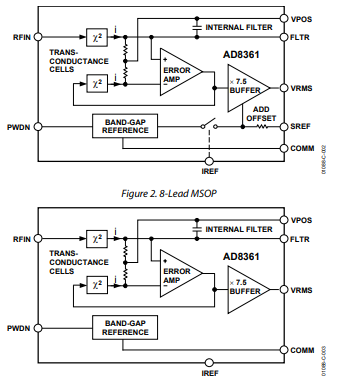

AD8361均值響應功率檢波器技術手冊

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+閱讀濾波器章節部分筆記

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+內容簡介

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+介紹基礎硬件算法模塊

STM32的ADC采樣及各式濾波算法實現

評論