AMD Vitis 軟件平臺是一款開發環境,主要用于開發包括 FPGA 架構、Arm 處理器子系統和 AI 引擎在內的設計。Vitis 工具與 AMD Vivado ML 設計套件相結合,可為設計開發提供更高層次的抽象。

本用戶指南涵蓋了 Vitis 入門、使用 Vitis Unified IDE、Bootgen 工具、Vitis Python CLI、軟件命令行工具、GNU 編譯器工具、嵌入式設計教程以及驅動程序和庫。如果您希望獲取完整版文檔,請至文末掃描二維碼進行下載。

Vitis 軟件平臺包括以下工具

-

Vitis Embedded - 用于開發在嵌入式 Arm 處理器上運行的 C/C++ 應用代碼

-

編譯器和仿真器 - 用于使用 AI 引擎陣列執行設計

-

Vitis HLS - 用于開發基于 C/C++ 的 IP 塊,該 IP 塊主要針對 FPGA 架構

-

Vitis Model Composer 是一種基于模型的設計工具,可在 MathWorks Simulink 環境中進行快速設計探索

-

一系列性能優化的開源庫函數,如 DSP、視覺、求解器、超聲和 BLAS 等,其可采用 FPGA 架構執行,也可使用 AI 引擎執行

工具與庫

Vitis 嵌入式

Vitis Embedded 是一個獨立的嵌入式軟件開發包,主要用于開發運行在嵌入式 Arm 處理器上的主機應用。

Vitis AIE DSP 設計工具

編譯器和仿真器

AMD Versal 自適應 SoC 器件具有 AI 引擎陣列,有助于采用資源和電源都優化的方式實現高性能 DSP 功能。將 AI 引擎與 FPGA 架構資源一起使用,有助于非常高效地實現高性能 DSP 應用。

Vitis HLS

Vitis HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕松創建復雜的 FPGA 算法。

Vitis HLS 工具與 Vivado ML 設計套件(用于綜合、布置和路由)及 Vitis 統一軟件平臺(用于異構系統設計和應用)高度整合。

Vitis Model Composer

Vitis Model Composer 是一款基于模型的設計工具,可在 MathWorks Simulink 環境中實現快速的設計探索。

此外,該工具還允許您使用一系列 AI 引擎和可編程邏輯 (HDL/HLS) 塊對設計進行建模和仿真。

Vitis 庫

性能優化的開源庫,提供開箱即用的加速,對于采用 C、C++ 編寫的現有應用而言,代碼修改極少,甚至不需要修改代碼。

按原樣利用特定領域的加速庫,通過修改適應您的需求,或者在您的自定義加速器中用作算法構建塊。

設計流程

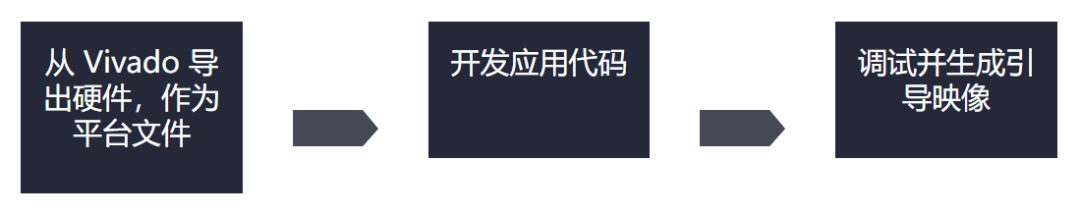

Vitis 嵌入式軟件開發流程

?

?在 AMD 自適應 SoC 中為 Arm 嵌入式處理器子系統開發 C/C++ 代碼的設計人員通常會使用該流程。

-

軟件工程師可將這些硬件設計信息整合到他們的目標平臺中,并可使用 Vitis 嵌入式軟件開發應用代碼。

開發人員可在 Vitis 嵌入式軟件中執行所有系統級驗證,并通過生成引導映像來啟動應用。

2023.2 版本新特性

-

AIE-DSP 設計的新特性:AIE 仿真器和編譯器增強

-

全新獨立 Vitis 嵌入式安裝程序:面向為 PS 子系統編寫嵌入式 C 代碼的設計人員

-

最新 Vitis 統一 IDE (GUI):從 2023.2 版開始,Vitis 將在所有 Vitis 工具中提供一個全新的通用 GUI。

-

配置文件、調試與跟蹤的新特性 — 面向 AMD Versal AIE 器件系列

+

獲取完整版

《Vitis 統一軟件平臺文檔》

請掃描二維碼進行下載

原文標題:Vitis 統一軟件平臺文檔

文章出處:【微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

-

賽靈思

+關注

關注

32文章

1794瀏覽量

131246 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121301

原文標題:Vitis 統一軟件平臺文檔

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

統一視頻平臺融合通信可視指揮調度平臺smarteye與國標GB28181平臺的異同與關聯

AMD Vitis Unified Software Platform 2024.2發布

ov華米聯手打造OneLink統一鏈接平臺

統一多云管理平臺怎么用?

一個更適合工程師和研究僧的FPGA提升課程

在Windows 10上創建并運行AMD Vitis?視覺庫示例

AMD Vitis? Embedded嵌入式軟件開發套件的功能和特性概述

Vitis2023.2使用之—— updata to Vitis Unified IDE

Vitis2023.2使用之—— classic Vitis IDE

Vitis2023.2全新GUI的功能特性介紹

Vitis 統一軟件平臺文檔

Vitis 統一軟件平臺文檔

評論