1 推動FPGA調試技術改變的原因

進行硬件設計的功能調試時,FPGA的再編程能力是關鍵的優點。CPLD和FPGA早期使用時,如果發現設計不能正常工作,工程師就使用“調試鉤”的方法。先將要觀察的FPGA內部信號引到引腳,然后用外部的邏輯分析儀捕獲數據。然而當設計的復雜程度增加時,這個方法就不再適合了,其中有幾個原因。第一是由于FPGA的功能增加了,而器件的引腳數目卻緩慢地增長。因此,可用邏輯對I/O的比率減小了,參見圖1。此外,設計很復雜時,通常完成設計后只有幾個空余的引腳,或者根本就沒有空余的引腳能用于調試。

圖1 Lattice FPGA的LUT/可用I/O

第二,現在設計的復雜性經常需要觀察許多信號,而不是幾個信號。常用的技術是實現較寬的內部總線,以便在較大的FPGA中達到高的系統吞吐量。如果懷疑內部的32位總線里有壞的數據,則難以用幾個I/O引腳來確定問題所在。

第三,通常需要在系統中測試復雜的功能。在這種情況下,在系統中調試時訪問一些I/O也許是有限的。新類型的包還限制訪問FPGA引腳。系統速度也是個問題,因為探針的連接可能會引起性能或者噪聲信號降低。

最后,推動FPGA調試方法改變的關鍵因素是有了新的工具,這些工具采用內部或者嵌入式邏輯分析儀。

擁有這些工具可得到最佳的結果,而不是用與先前工具相同的方法。資源、靜態參數和動態參數通常約束了內部邏輯分析儀和外部邏輯分析儀。本文對這兩種類型工具的約束進行了比較,考察如何最佳地利用內部邏輯分析儀。

2 外部邏輯分析儀受到的限制

外部邏輯分析儀已經用了幾十年了。外部邏輯分析儀的最大優點是能夠存儲大量的信號信息,或者用來跟蹤數據。配置在不斷變化,但大多數外部邏輯分析儀可以存儲兆字節的數據。為了對FPGA使用外部邏輯分析儀,數據信號必須引到片外。可用兩種方法中的一種來做。第一種方法是直接把信號送到用于觀察的I/O引腳。取決于FPGA 的封裝類型,接觸I/O引腳 可能會有困難。 針對用這種方法進行調試的電路板 設計 要用連接器,例如與FPGA相連的MICTOR連接 器。然而這種方法不是很有效, 因為每個信號都需要一個I/O引腳。

第二種方法是插入能把信號引到I/O的核。這種方法的優點是這個核設計成能多路復用信號至I/O引腳,允許引腳共享。這種方法的局限是信號要被外部的邏輯分析儀實時捕獲,多路復用大大降低了快速捕獲信號的可能性。由于這個原因,通常使用2x 或者 4x多路復用方案。這意味著現在32 個I/O引腳可以支持64個或128個信號。這樣得到了很大的改進,但是仍然有限制,例如要調試寬總線的情況。一旦信號連接到外部的邏輯分析儀,然后就設置觸發和數據捕獲條件。

使用外部邏輯分析儀設置的約束是有限的信號、高速觸發邏輯和大量的跟蹤存儲器。大多數邏輯分析儀使用狀態機觸發機制。用戶指定一個值等待這個信號,然后捕獲這個數據,或者進入另一個狀態,尋找不同的情況。這些信號本身是靜態的,但各種情況是動態的,會在任何時候發生變化。給定約束后,這個方法很有效。因為限制了信號的數目,在信號組合的情況下減少了操作數。但是跟蹤的存儲器相對較大,試圖找到一個接近的觀察點是很普通的事,然后捕捉大量的數據以找到問題所在。

3 使用內部邏輯分析儀

用內部邏輯分析儀能與外部邏輯分析儀一樣對FPGA進行功能調試。內部邏輯分析儀使用嵌入在FPGA設計中的一個或多個邏輯分析儀核。設計者使用PC在軟件中設置觸發條件,通過JTAG訪問FPGA。一旦邏輯分析儀軟核捕獲了數據,通過JTAG將信息返回PC,然后設計者對這些數據進行觀察。觸發信號的復雜性和跟蹤存儲器的大小對信號數目有限制。大多數情況下,設計者可以觀察成百上千個信號。

觸發資源受FPGA限制,即未使用的邏輯和RAM。跟蹤存儲器有些實現需要RAM。有些則需要RAM或者LUT。然而,所需要的跟蹤存儲器比用外部邏輯分析儀大大減少,通常為數千位與數百萬位之比。觸發和數據捕獲以設計的全速進行,因為信號不需要在FPGA片外復用。

用外部邏輯分析儀時,信號必須靜態定義。改變信號經常需要FPGA再次執行,盡管有些工具提供只增加FPGA布線來改變部分或全部連接信號的能力。在調試期間,大多數實現部分或所有觸發條件動態地改變。然而,觸發的復雜性的變化取決于所用的工具。信號差別越多,所能提供的存儲器就越小。為了獲得最佳的結果,不同的觸發選項驅動了使用內部邏輯分析儀的需要。

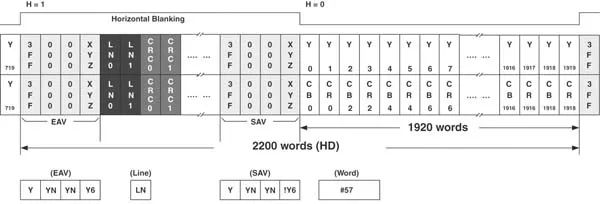

復雜調試的一個例子是在SMPTE SDI HD顯示中尋找一個特別的像素。在特殊的情況下,找到EAV (end active video)時序是必須的,然后尋找與數據相關的特別線數,再尋找SAV (start active video)時序。最后根據線中對應的像素,計算字節數目,參見圖2。

圖2 SDI HD數據流實例

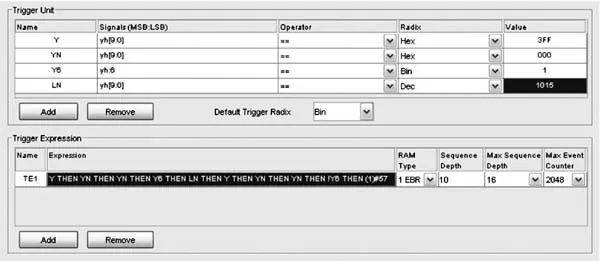

為了調試找到這種數據需要尋找值的時序,再找特殊值,然后結束序列,最后在捕獲數據前數時鐘的數目。為了理解是如何做的,必須查看具體的實現過程。萊迪思的Reveal硬件調試器使用觸發單元和觸發表示以決定觸發點。觸發單元是一個比較器,觸發表示允許觸發單元和序列值組合在一起。

對于這個SDI實例,用3個觸發單元來定義EAV和SAV序列,另外的觸發單元用于線數,最后在發現數據前的一個計數聲明用于等待。觸發建立的實例如圖3所示。這個設置可以用來尋找任何要求的線數和像素,因為線數觸發的值和計數可以動態地改變。

圖3 觸發設置的實例

4 結論

工程師將繼續使用外部邏輯分析儀,因為用它分析系統級功能時是很有價值的。但是用于內部FPGA調試需要連接到電路板,信號的數目受到了限制。而內部邏輯分析儀在可用信號數目方面提供了很大的自由度,但是在觸發邏輯和跟蹤存儲器方面受到約束。然而小心地使用觸發選項使內部邏輯分析儀在精確的時間開始捕獲數據,要最大化可用的資源。這個例子中,需要分析在SDI視頻信號里特殊的像素(線和字)的復雜實現被分解成簡單的元素,這種方法提高了效率。這個例子只是瀏覽了內部邏輯分析儀的使用和應用。由于FPGA設計復雜性不斷增加,針對功能驗證和調試,內部邏輯分析儀和類似的工具受到了設計者的青睞。

精彩推薦 至芯科技FPGA就業培訓班——助你步入成功之路、12月30號西安中心開課、歡迎試聽! 詳解從均值濾波到非局部均值濾波算法的原理及實現方式 中國市場FPGA產業競爭格局現狀分析掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:如何用內部邏輯分析儀調試FPGA?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603012

原文標題:如何用內部邏輯分析儀調試FPGA?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

利用EVM對ADS1299進行內部產生方波的測試,如何才能從邏輯分析儀上獲得正確的輸出?

4457示波器-H01邏輯分析儀選件

Keysight 頻譜分析儀(信號分析儀)

multisim中邏輯分析儀怎么連接

邏輯分析儀multisim的應用

邏輯分析儀可以當示波器用嗎

邏輯分析儀主要工作方式是什么

24M的邏輯分析儀怎么用的

邏輯分析儀的主要用途是什么

邏輯分析儀的使用說明

邏輯分析儀的常見故障及原因

邏輯分析儀的基本原理、結構組成及關鍵技術

音頻分析儀的原理

淺析FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

如何用內部邏輯分析儀調試FPGA?

如何用內部邏輯分析儀調試FPGA?

評論