在調(diào)試FPGA電路時(shí)要遵循必須的原則和技巧,才能降低調(diào)試時(shí)間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。

1、在焊接硬件電路前,首先要測(cè)試電路板的各個(gè)電源之間,各電源與地是否短路;最好是每一塊板子都進(jìn)行測(cè)試,這樣板子焊好后如果出現(xiàn)電源和地短路的情況也可以首先排除是板子本身的問(wèn)題。

2、在焊接硬件時(shí),首先先焊接電源部分,然后測(cè)試,排除電源短路等情況后,上電測(cè)量電壓是否正確;對(duì)于電源要求比較高的某些電路要測(cè)試電源芯片的輸出電壓是否處于正常工作要求的范圍之內(nèi)。

3、然后焊接FPGA及相關(guān)的下載電路。再次測(cè)量電源地之間有沒(méi)有短路現(xiàn)象,上電測(cè)試各電壓是否正確;將手排除靜電后觸摸FPGA有無(wú)發(fā)燙的現(xiàn)象。

a.如果出現(xiàn)短路,通常是去耦電容短路造成的,所以在焊接時(shí)通常先不焊去耦電容。FPGA的管腳粘連也可能造成短路,這時(shí)需要比較電路圖和焊接仔細(xì)查找有無(wú)管腳粘連。

b.如果出現(xiàn)電壓值錯(cuò)誤,通常是電源芯片的外圍調(diào)壓電阻焊錯(cuò),或者電源的承載力不夠造成的。若是后者,則需要選用負(fù)載能力更強(qiáng)的電源模塊替換。假如FPGA的I/O管腳與電源管腳粘連,也可能出現(xiàn)電壓值錯(cuò)誤的現(xiàn)象。

c.如果出現(xiàn)FPGA發(fā)燙,通常是出現(xiàn)總線(xiàn)沖突的現(xiàn)象。這種情況下需要自行檢驗(yàn)外圍總線(xiàn)是否可能出現(xiàn)競(jìng)爭(zhēng)疑問(wèn)。特別是多片存儲(chǔ)器共用總線(xiàn)時(shí)刻。比如SRAM和FLASH芯片復(fù)用一套總線(xiàn),如果片選信號(hào)同時(shí)有效就出現(xiàn)總線(xiàn)沖突。

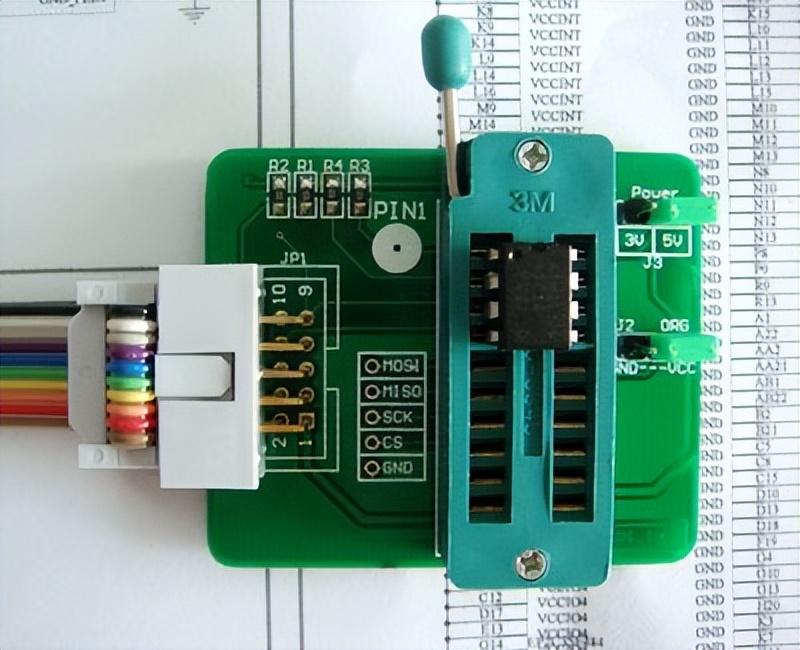

4、以上完成后,將電路板上電運(yùn)行。將下載線(xiàn)接到JTAG口上,看是否能正確檢測(cè)到FPGA。

5、分別將測(cè)試程序?qū)懭氲絊RAM和PROM,確定FPGA的配置電路是否正確。

精彩推薦 至芯科技FPGA就業(yè)培訓(xùn)班——助你步入成功之路、12月30號(hào)西安中心開(kāi)課、歡迎試聽(tīng)! 浮點(diǎn)LMS算法的FPGA實(shí)現(xiàn) 詳解從均值濾波到非局部均值濾波算法的原理及實(shí)現(xiàn)方式掃碼加微信邀請(qǐng)您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:FPGA硬件電路的調(diào)試必備原則和技巧

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009

原文標(biāo)題:FPGA硬件電路的調(diào)試必備原則和技巧

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

玩轉(zhuǎn)FPGA必備的基礎(chǔ)知識(shí)

如何進(jìn)行硬件調(diào)試?

MQTT調(diào)試助手中文版(物聯(lián)網(wǎng)開(kāi)發(fā)必備)

上海 10月25日-26日《硬件電路設(shè)計(jì)、調(diào)試與工程案例分析》公開(kāi)課即將開(kāi)始!

組成放大電路的基本原則是什么?

如何在服務(wù)器上調(diào)試本地FPGA板卡

FPGA與SRIO調(diào)試步驟

fpga是硬件還是軟件

fpga仿真器是什么?它有哪些優(yōu)勢(shì)?

fpga軟件是什么意思

fpga是硬件還是軟件

FPGA與AISC的差異

fpga是什么 fpga用什么編程語(yǔ)言

淺析FPGA的調(diào)試-內(nèi)嵌邏輯分析儀(SignalTap)原理及實(shí)例

FPGA硬件電路的調(diào)試必備原則和技巧

FPGA硬件電路的調(diào)試必備原則和技巧

評(píng)論