原理圖設計

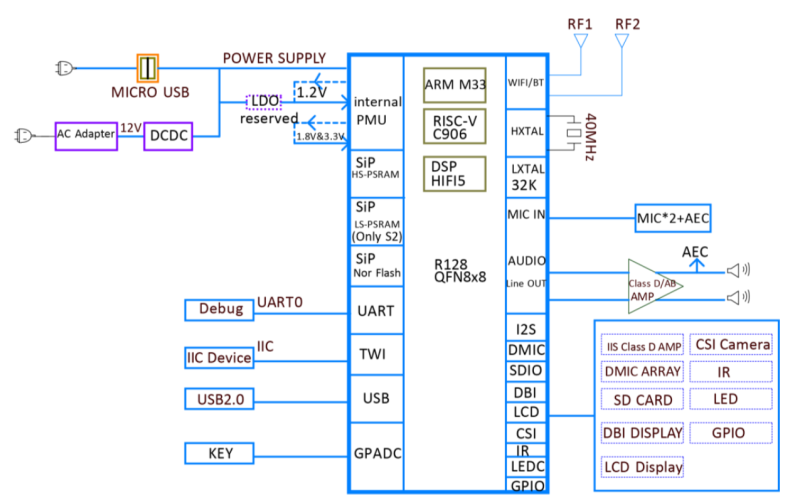

硬件系統框圖

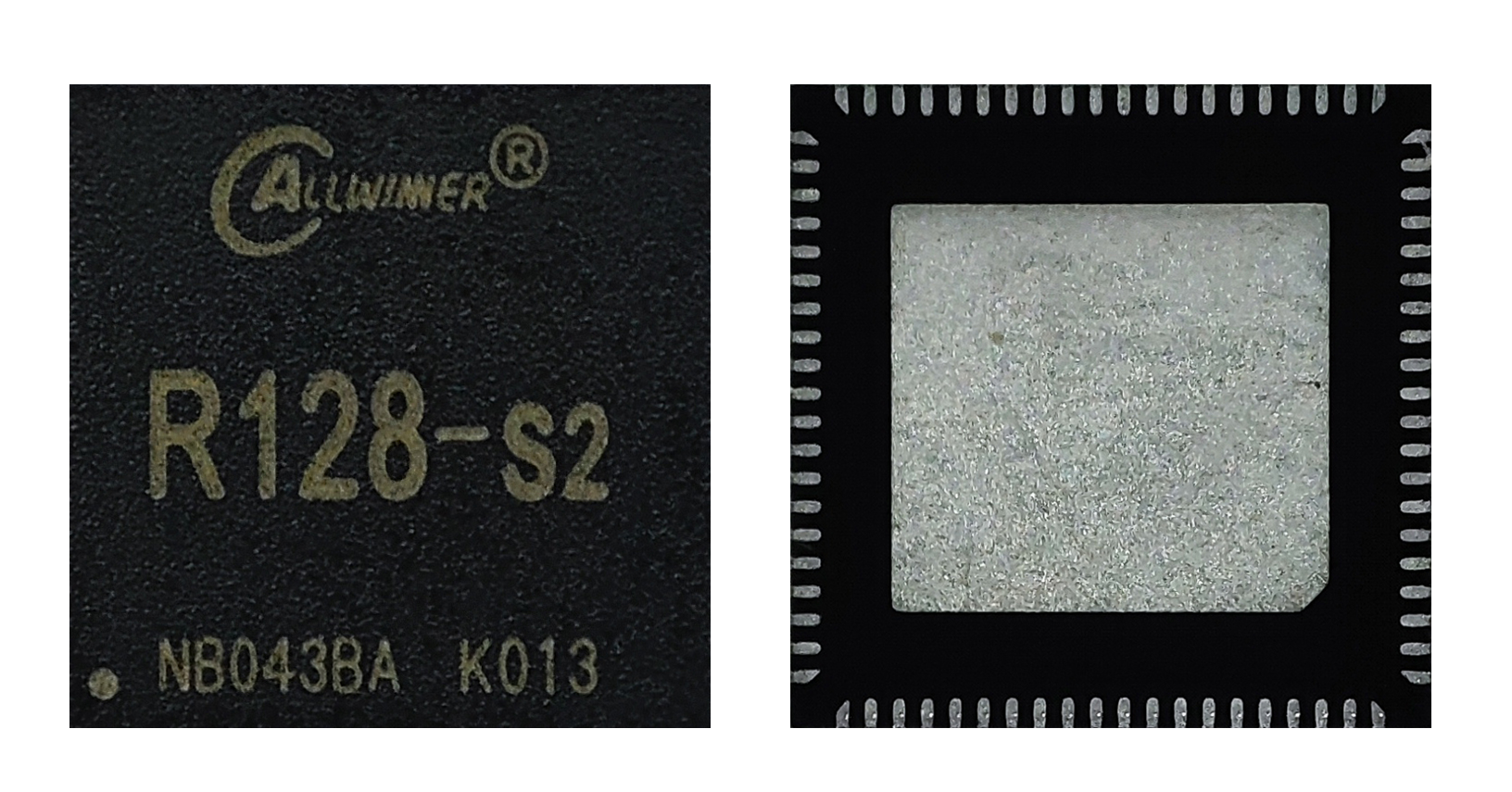

R128是一顆專為“音視頻解碼”而打造的全新高集成度 SoC,主要應用于智能物聯和專用語音交互處理解決方案。

- 單片集成 MCU+RISCV+DSP+CODEC+WIFI/BT+PMU,提供生態配套成熟、完善的用于系統、應用和網絡連接開發的高效算力;

- 集成 8MB/16MB/32MB PSRAM,為音視頻解碼、大容量存儲、掃碼以及網絡連接提供充裕的高容量、高帶寬的內存支持;

- 擁有豐富的音頻接口 IIS/PCM、OWA、DMIC、LINEOUT、MICIN 以及通用通訊接口 IIC、UART、SDIO、 SPI、ISO7816卡接口;同時支持 U 盤、SD卡、IR-TX/RX;

- 內置 LDO、GPADC、LEDC,簡化系統方案設計,降低 BOM成本。

硬件系統基本工作原理

R128硬件系統基本工作流程如下:

- 硬件系統正常上電,主控復位之后,CPU開始執行 BROM固化代碼,對系統資源和關鍵外設進行配置及初始化,包括電源,時鐘,總線,復位,存儲接口等。

- 根據配置,在 BROM階段將系統初始化信息(串口、PSRAM等)從存儲介質讀取到系統 SRAM,進行芯片及系統的進一步詳細配置和初始化工作;執行完 Boot0 程序后進入 boot 階段。

- 從外部存儲介質中讀取下一階段需要的軟件代碼,啟動操作系統,并對系統資源和外設進行管理。

- 操作系統啟動之后,根據產品不同需求加載相關啟動,比如 USB、音頻、WIFI、顯示、藍牙等模塊,最終完成開機啟動,進入普通操作界面。

- 系統支持 watchdog 應用監視系統的運行,當程序跑飛或者發生死循環時,watchdog模塊會發出一個復位信號,使 SOC復位,軟件系統重新啟動。

R128硬件系統組成如下表:

| 系統 | 說明 |

|---|---|

| CPU小系統 | 時鐘,復位,中斷,系統配置 |

| 存儲系統 | PSRAM,SPI NAND/SPI NOR/EMMC/SD CARD |

| 音頻系統 | MIC IN、FMIN、IIS/PCM/TDM、DMIC、LINEOUT |

| 輸入輸出子系統 | RGB、SD CARD、USB OTG/HOST、TWI、UART、PWM、GPADC、TPADC、CSI、 IR TX/RX 等 |

| 電源系統 | DCDC、LDO |

| 無線 | WIFI/BT |

| 其他 | 功放、LED |

CPU小系統

R128 CPU小系統包括時鐘系統,系統配置 PIN、復位系統和 Debug 部分。

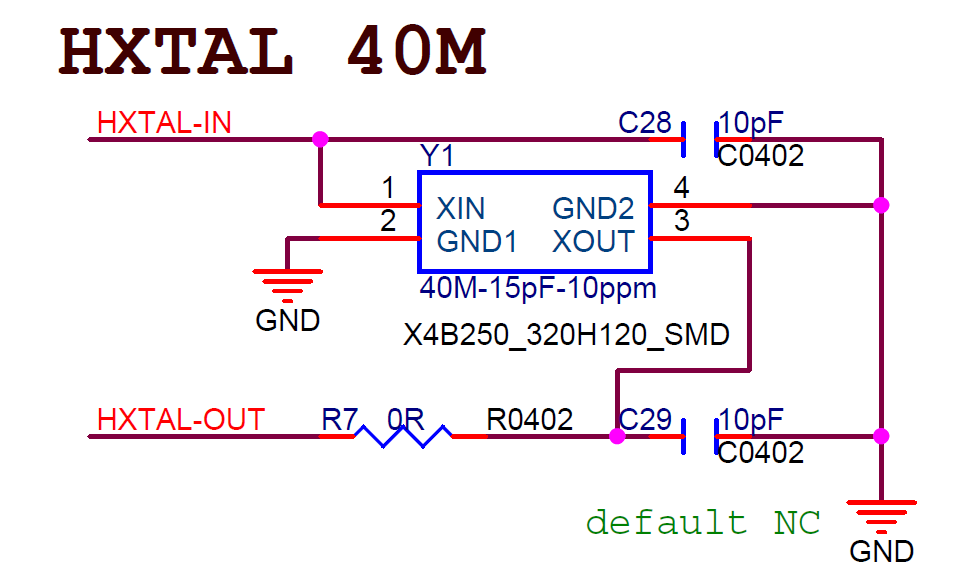

時鐘系統信號PIN說明

R128 硬件系統包含 DCXO 40M/RTC 32.768K 兩個時鐘,對應時鐘信號說明如表所示。

| 信號名 | 信號描述 | 應用說明 |

|---|---|---|

| HXTAL_IN | DCXO晶振輸入 | 默認使用 40M晶振,頻率誤差為 10PPM; |

| HXTAL_OUT | DCXO晶振輸出 | 默認使用 40M晶振,頻率誤差為 10PPM; |

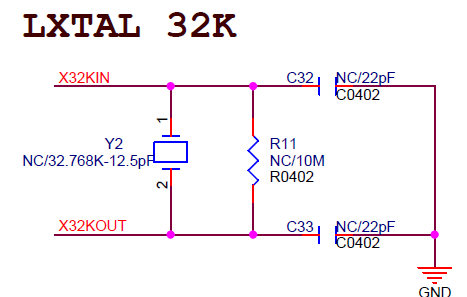

| LXTAL_IN | 32K晶振輸入 | 32.768K晶振電路,頻率誤差為 20PPM |

| LXTAL_OUT | 32K晶振輸出 | 32.768K晶振電路,頻率誤差為 20PPM |

RTC 32.768K時鐘可以從內部 RC振蕩電路產生,可不使用外部 32K晶振。

小系統配置說明

R128小系統配置 PIN說明如表所示。

| 信號名 | 信號說明 | 應用說明 |

|---|---|---|

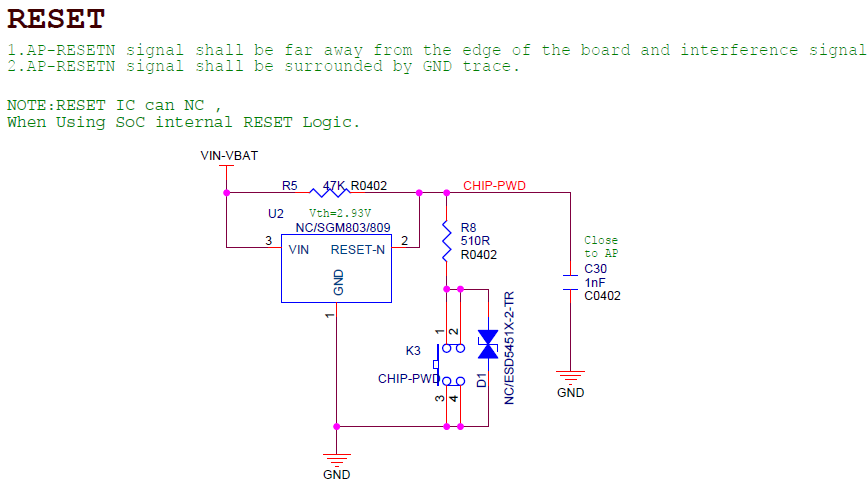

| RESET | system reset | 1,系統復位 PIN 2,Watchdog 輸出 PIN |

| CHIP-PWD | Chip power down/System reset | 1,內部 PMU 下電控制 pin; 2,系統復位 pin |

| PA1/FEL0 | FEL功能選擇 pin 0 | 當[FEL0,FEL1]= 00時,SOC進入 FEL升級狀態 |

| PA2/FEL1 | FEL功能選擇 pin 1 | 當[FEL0,FEL1]= 00時,SOC進入 FEL升級狀態 |

- RESET和 CHIP-PWD均可實現系統復位功能,但 CHIP-PWD包含 R128內部 PMU掉電控制功能,可讓R128實現上電復位功能。

- RESET/CHIP-PWD信號上接下地電容默認為 1nF,用于濾波和增強 ESD 防護能力

- 為避免 SOC啟動時誤進入升級狀態,PA1/FEL0和 PA2/FEL1 不能同時接下拉電阻。

主晶振電路

- R128 DCXO模塊推薦使用 40M 晶振以獲得更好的射頻性能。

- 晶振選型參考如下:

- R128集成 WIFI/BT功能,為獲得更好的射頻性能,建議晶振選型頻率容限與頻率穩定性均≤ 10ppm

- 晶體負載電容指標 CL,建議 CL≥10pF。CL過小會導致晶體溫飄過大

- 晶體驅動能力 DL,建議典型值 100uW,最大不超過 200uW。取值過小會影響晶體壽命。

- 外掛匹配電容大小根據晶振規格和 PCB而定,要求匹配電容+板級雜散電容總值等于晶振規格要求的負載電容大小。

- 串接電阻需要預留位置,便于調試振蕩幅度處理 EMI 問題。

晶振參數不得隨意更改,需保證晶體自身負載電容、外掛匹配電容、PCB走線負載電容三者匹配。

32.768K時鐘電路

- 支持內部 RCOSC時鐘,支持 HOSC校準,滿足 32.768K時鐘輸出。

- 外掛 32.768K 晶振時,外掛匹配電容大小根據晶振規格和 PCB而定,要求匹配電容+板級雜散電容總值等于晶振規格要求的負載電容大小。

- LXTAL_IN/LXTAL_OUT 之間并接的電阻,必須保留,用于對頻率微調。

晶振參數不得隨意更改,需保證晶體自身負載電容、外掛匹配電容、PCB走線負載電容三者匹配。

復位電路設計

R128可以選擇使用外部復位 IC提供復位信號,也可以使用內部復位源。

- 內部上電復位觸發門檻:VBAT爬升至約 2.4V;

- 內部下電復位觸發門檻:VBAT跌落至 3.0V/2.9V/2.8V/2.7V/2.6V/2.5V(軟件可配置),詳見 R128用戶手冊;

- 使用外部復位 IC 復位,時長不得低于 64ms;

- RESET Pin放置 1nF電容。

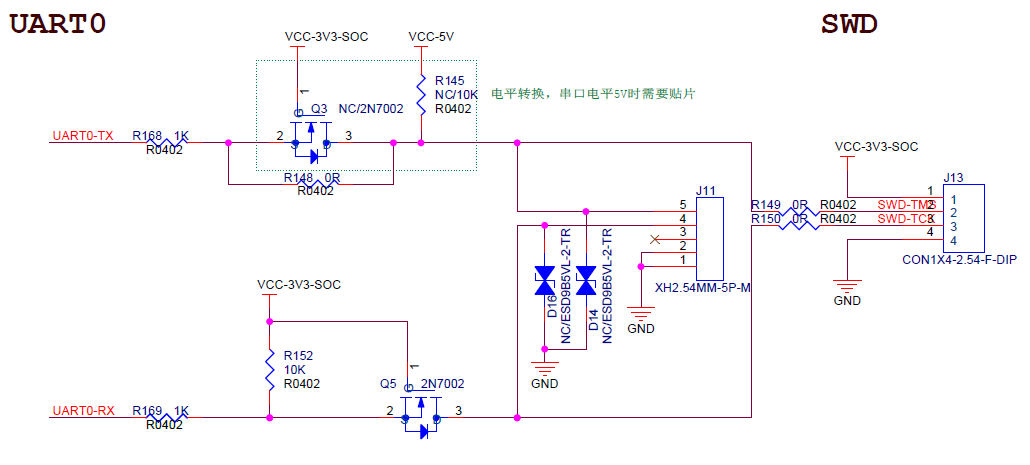

DEBUG電路設計

R128支持 USB(OTG)、UART、JTAG與 SWD 等多種調試方式,客戶可根據需要選擇合適的調試方式,建議在設計時對相應的調試接口預留測試點方便后續調試驗證。

電源系統設計

SOC端電源質量要求

R128集成 PMU,外部僅需提供 VBAT 電源即可滿足 R128 電源應用需求,其他電源由內部 PMU 產生。

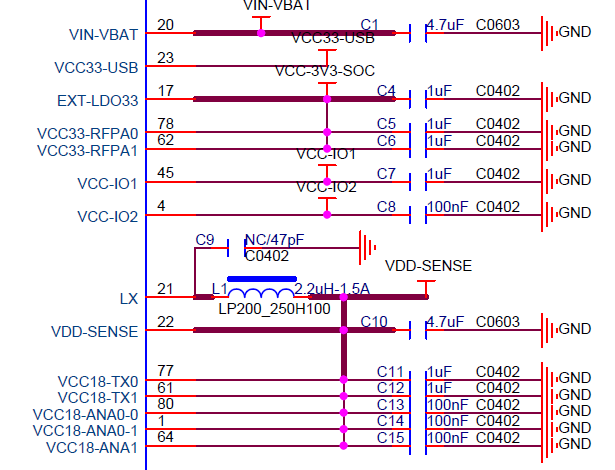

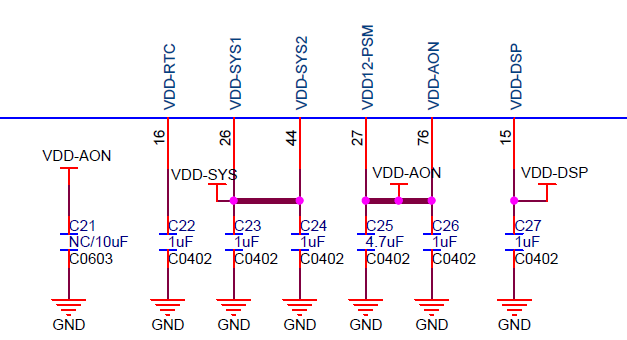

SOC端電源電容設計

R128 SOC端各電源要求濾波電容容值如下:

- VDD_LX管腳建議預留放置 1個 2.2uF電容;

- VDD_SENSE管腳建議放置 1個 4.7uF電容;

- VDD_CLK、VDD18_ANA1、VDD18_TX1、VDD18_ANA2、VDD18_TX2電源 pin建議各放置 1個 100nF電容,靠近管腳放置;

- VDD_DSP建議放置 1個 1uF電容,靠近管腳放置;

- VDD_RTC建議放置 1個 1uF電容,靠近管腳放置;

- VDD_SYS1、VDD_SYS2建議各放置 1 個 1uF電容,靠近管腳放置;

- VDD_AON建議放置 1個 1uF電容,VDD12_PSM 建議放置 1 個 100nF 電容,靠近管腳放置;

- VDD_3V3建議放置 1個 1uF電容, VDD33_LB1、VDD33_LB2 建議各放置 1 個 100nF 電容,靠近管腳放置;

- VDD_IO1、VDD_IO2、VDD_IO_5VTOL建議各放置 1 個 100nF 電容,靠近管腳放置;

- AVDD電源與 AGND之間至少 1個 2.2uF電容,靠近引腳放置。

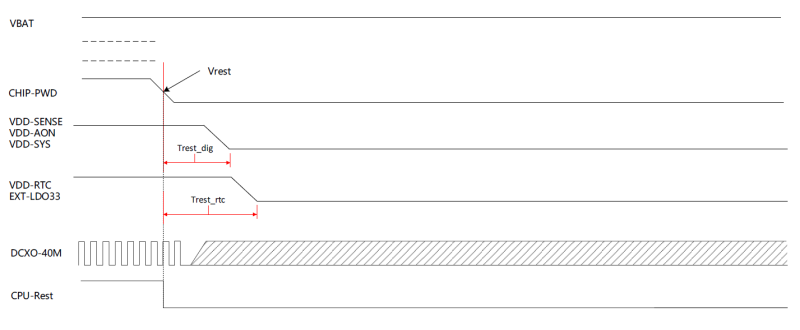

上電時序設計

R128各模塊供電采用內部 PMU,其上電時序如圖所示,時序描述如下:

- VBAT為 SOC外部電源輸入,其上電至 2.4V附近觸發內部 POR復位;

- 完成 POR 復位后,PMU各路 DCDC、LDO按照下圖所示時序進行上電;

當使用外部 DCDC 或 LDO為 R128 的 VDD_IO1、VDD_IO2和 VDD_IO_5VTOL進行供電時,為避免電源從 IO漏電導致 SOC啟動失敗,建議使用 EXT_LDO(pin VDD_3V3)對外部 DCDC或 LDO 進行時序控制。

下電時序設計

R128下電時序如圖所示,時序描述如下:

- R128內部集成掉電復位功能,通過檢測 VBAT電壓觸發復位,可軟件使能掉電復位功能和配置門檻電壓,詳見 R128 用戶手冊描述;

- 復位信號拉低后,DXCO、RCOSC停止振蕩,各路 DCDC、LDO停止輸出。

PSRAM 電路設計

R128內置 PSRAM,無需外部電路,只需滿足 R128 電源設計要求即可。

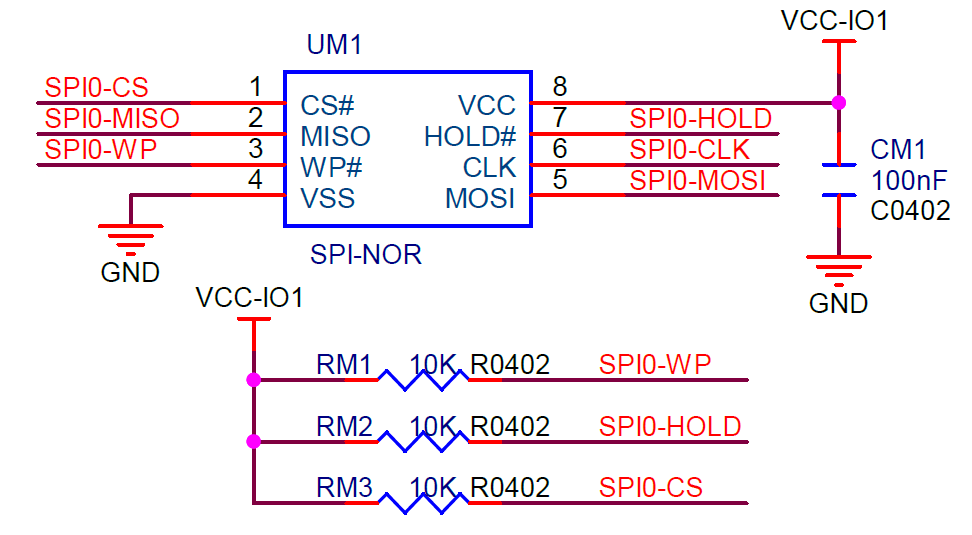

Flash 電路設計

R128支持合封 SPI Nor FLSAH,支持外掛 SPI Nand/Nor、eMMC,設計說明如下:

- 使用合封 SPI Nor FLASH 時,VDD-IO1必須使用 3.3V電源;

- 使用外掛 SPI Nand/Nor、eMMC 器件時,可選擇從 PA24-PA29、PB4-PB7&PB14/15、PA2-PA7 三個地方啟動;

- 啟動介質選擇支持 Try 與 eFuse Select 兩種方式;

- Try 方式啟動順序為 SDC0->SPI NOR->SPI NAND->EMMC,該模式僅支持輪詢 PA 口的啟動介質

- eFuse Select方式啟動順序由 eFuse決定,具體啟動順序及燒碼值可定制

SPI NOR/NAND 參考設計

GPIO 電路設計

R128 有PA/PB 2 組GPIO,GPIO 邏輯電平與供電電壓有關。

- 未使用的GPIO 優先建議接地或者Floating,軟件設定為disabled 狀態;

- IO 上拉電阻上拉電壓選擇IO 所在電源域。

| GPIO 分組 | 控制器電源域 | IO電源域 | IO電壓 |

|---|---|---|---|

| PA0~PA14 | VDD-SYS | VDD-IO2 | 3.3V/1.8V |

| PA18~PA23 | VDD-SYS | VDD-IO2 | 3.3V/1.8V |

| PA16~PA17 | VDD-SYS | VDD-IO-5VTOL | 5V/3.3V/1.8V |

| PA15 | VDD-SYS | VDD-IO1 | 3.3V/1.8V |

| PA24~PA29 | VDD-SYS | VDD-IO1 | 3.3V/1.8V |

| PB0~PB15 | VDD-SYS | VDD-IO1 | 3.3V/1.8V |

LED電路設計

R128集成 LEDC功能,可以直接驅動集成式 LED。

集成式 LED一般供電范圍是 3.5~5.3V,Vih必須大于 0.7*VDD,如 WS2812C。當 VDD為 5V供電時,Vih必須大于 3.5V,已超出 SOC IO輸出電壓范圍。解決方案:

- 5V供電串聯 1N4148二極管,降低 VDD電壓,理論 VDD電壓為 4.3V,此時 Vih 大于 3V 即可;

- 市場已有 5V 供電且支持 3.3V邏輯控制的集成式 LED,如 WS2128B-V4/V5。

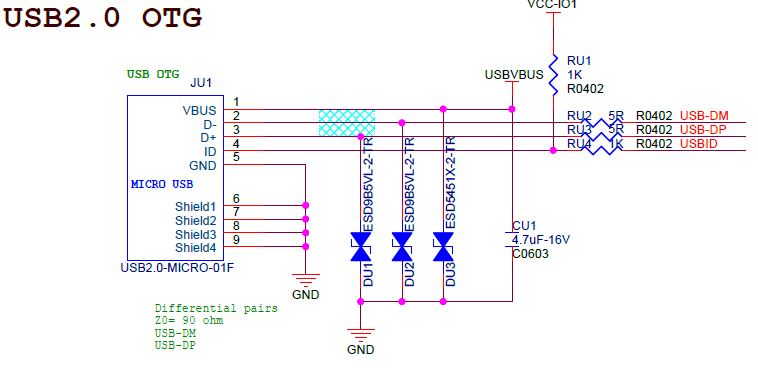

USB電路設計

R128 USB接口具有 HOST和 OTG功能,在產品功能定義上需要注意區別。

- 若使用 Micro USB 供電,建議在 VBUS上放置限流和防倒灌 IC、TVS 保護器件;

- USB-ID 信號為 OTG 檢測信號,上拉電壓選擇 USB-ID Pin所在電源域;

- USB-ID 信號到 SOC端的 GPIO 串接 1K~1.5K電阻提升 ESD性能;

- 建議在 VBUS 上放置穩壓管和 TVS保護器件;

- D+/D-信號線為高速信號線,并接的 TVS 要求低容值,否則影響數據傳輸,以小于 4pF 為宜;串接預留 5 電阻。

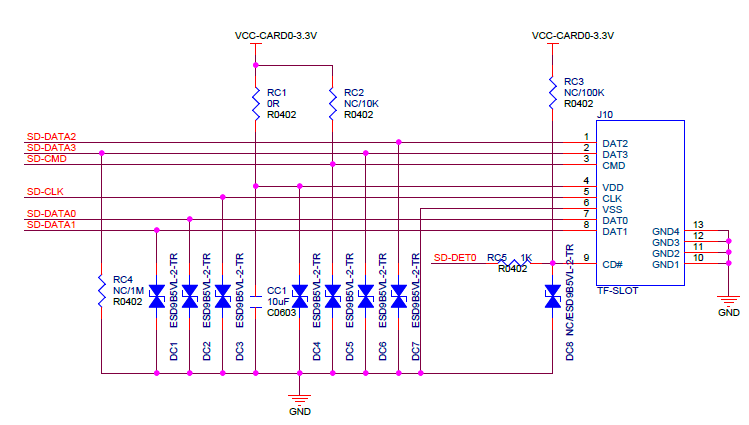

SD Card 電路設計

- SDC0-CLK串接 33R電阻,靠近 SoC擺放;

- SDC0-CMD和 SDC0-DET Pin芯片內部集成 15K上拉電阻,外部 10K上拉默認 NC;

- SDC0-DET串接 1K電阻,減緩信號下沖和提供 IO ESD能力;

- 靠近 SD 卡座,每個信號 Pin放置 ESD器件。

- SD卡座電源 VDD預留串聯 0R電阻,防止卡插入時,瞬間大電流燒卡。

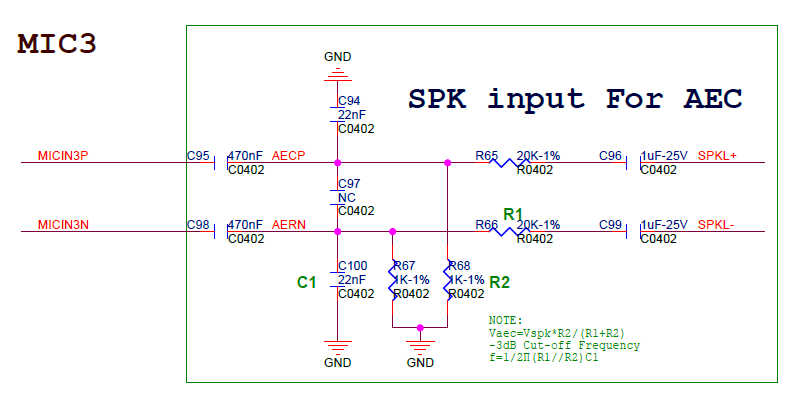

音頻電路設計

- 3個 ADC,可支持 3 個差分 MIC 輸入;

- 2個 DAC,R128-S1/S2可支持差分立體聲輸出,R128-S3可支持單聲道差分音頻輸出;

- 支持 1 套 I2S/PCM 接口,支持 TDM模式,支持主從模式;

- 支持 OWA 輸出,兼容 SPDIF 協議;

- 支持 DMIC 8 聲道輸入。

音頻設計建議如下:

- AVDD對地電容為 2.2uF;VRA1對地電容為 470nF;VRA2對地電容為 470nF;MBIAS對地電容為 2.2uF;

- AVDD/VRA1/VRA2的 AGND通過 0R電阻單點到 GND;

- MIC1-3建議組合成 2MIC+1AEC 電路;

MIC和 AEC參考設計如圖所示。AEC 回路電阻電容參數與功放輸出幅度和算法公司要求有關,參數以實際開發環境為準。

ADC電路設計

支持 1 路 GPADC 接口,12bit采樣分辨率,9bit采樣精度,單通道最高采樣率為 1MHz,最大支持 8 通道,可以用作按鍵功能或采集電池電壓使用。

- GPADC 量程范圍為 0~2.5V,應用時建議使用 0.2~2.3V作為輸入檢測電平;

- 按鍵按鍵分壓電阻,請使用推薦的阻值,如 5 個按鍵以下,推薦使用 1%精度電阻。添加按鍵時保證按鍵按下后,ADC網絡電壓范圍為 0~1.08V,最小間隔大于 200mV。

LCD電路接口

R128 支持一路 RGB屏接口和一路 SPI屏接口。其中 RGB屏接口可支持并行 RGB666 模式(1024x768@60fps)、串行 RGB模式(800x480@60fps)和 i8080模式(800x480@60fps),各種模式下管腳功能描述如下表。

SPI屏支持以下幾種模式:

| 3 線 1 DATA | 3 線 2 DATA | 4線1 DATA | 4線2 DATA | 2 DATA Lane |

|---|---|---|---|---|

| DBI-CSX | DBI-CSX | DBI-CSX | DBI-CSX | DBI-CSX |

| / | / | DBI-DCX | DBI-DCX | / |

| DBI-SCLK | DBI-SCLK | DBI-SCLK | DBI-SCLK | DBI-SCLK |

| DBI-SDA | DBI-SDO | DBI-SDA | DBI-SDO | DBI-SDA |

| / | DBI-SDI | / | DBI-SDI | WRX |

| DBI-TE | DBI-TE | DBI-TE | DBI-TE | DBI-TE |

DBI接口與SPI1復用關系

| SPI | DBI |

|---|---|

| SPI1-CS | DBI-CSX |

| SPI1-CLK | DBI-SCLK |

| SPI1-MOSI | DBI-SDO/SDA |

| SPI1-MISO | DBI-SDI(WRX)/TE/DC X |

| SPI1-HOLD | DBI-DCX/WRX |

| SPI1-WP | DBI-TE |

CSI電路接口

| PIN腳 | CSI接口 | 說明 | DVP |

|---|---|---|---|

| PA18/PB0 | NCSI0-HSYNC | 攝像頭行同步 | HSYNC |

| PA19/PB1 | NCSI0-VSYNC | 攝像頭場同步 | VSYNC |

| PA20/PB14 | NCSI0-PCLK | 攝像頭像素時鐘 | PCLK |

| PA21/PB15 | NCSI0-MCLK | 攝像頭主時鐘 | MCLK |

| PA22 | NCSI0-D0 | Parallel CSI Data | Y2 |

| PA23 | NCSI0-D1 | Parallel CSI Data | Y3 |

| PA27 | NCSI0-D2 | Parallel CSI Data | Y4 |

| PA26 | NCSI0-D3 | Parallel CSI Data | Y5 |

| PA29 | NCSI0-D4 | Parallel CSI Data | Y6 |

| PA25 | NCSI0-D5 | Parallel CSI Data | Y7 |

| PA24 | NCSI0-D6 | Parallel CSI Data | Y8 |

| PA28 | NCSI0-D7 | Parallel CSI Data | Y9 |

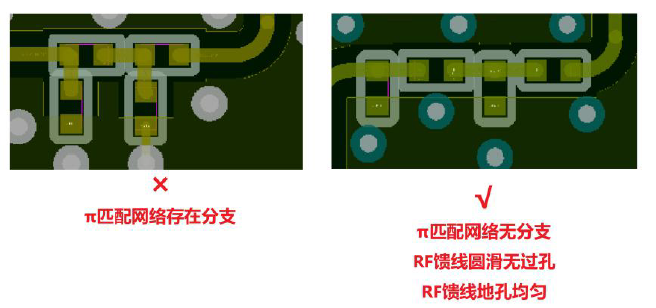

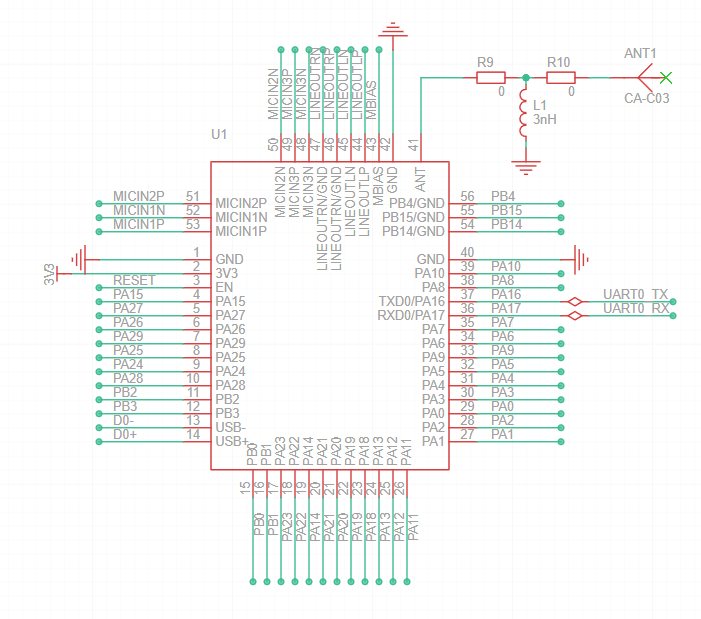

射頻端口設計

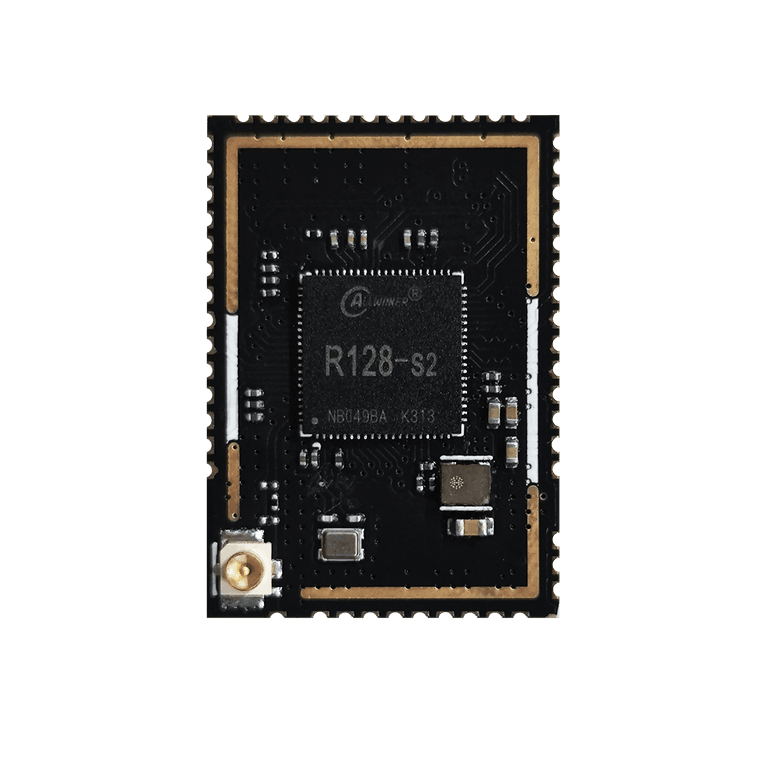

射頻輸出端口(ANT pin)無需匹配電路,但可預留天線 PI 型匹配電路。如上圖所示。為了方便天線PI型匹配電路調試,需在射頻輸出端口與天線間預留 0Ω電阻 WR1。如圖所示。

因 R128 芯片射頻前端已設計濾波器用于射頻認證時濾除諧波雜散,因此,硬件方案端只需要預留一個PI型匹配電路用于匹配天線,無需額外多預留一個 PI型濾波網絡用于濾除諧波雜散。

原理圖設計其他

- I2C/TWI 最大支持 400Kbit/s 的傳輸速率,總線上加上拉電阻,推薦值為 2.0K~4.7K,上拉電源為對應 GPIO電源域,各設備地址不得有沖突;

- GPIO分配時,請確保電平相匹配,上拉的電壓域必須為此 GPIO的電源域,以防外設向 SOC漏電情況發生;

- 串口調試電路 TX/RX 信號要加防倒灌電/隔離保護電路。可以選擇 MOS管或二極管方案,二極管方案必須選擇肖特基二極管。加工生產時為節約成本,MOS管和二極管隔離保護電路可以 NC,但板級至少要串接 100Ω電阻。

PCB設計

疊層設計

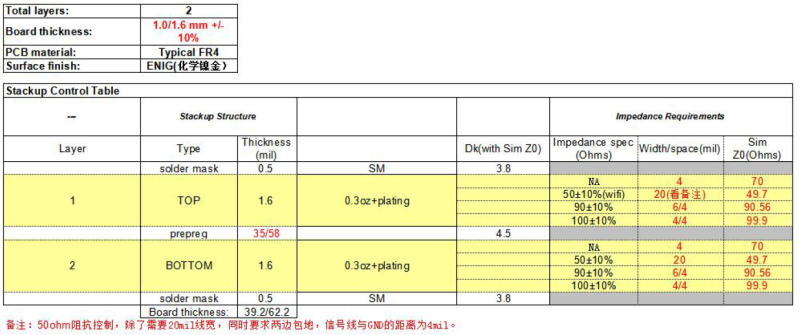

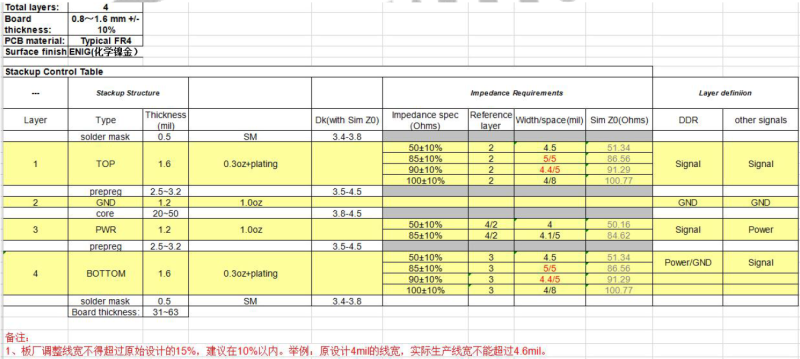

R128采用兩層板或四層板設計。

2層板設計參考

4層板設計參考

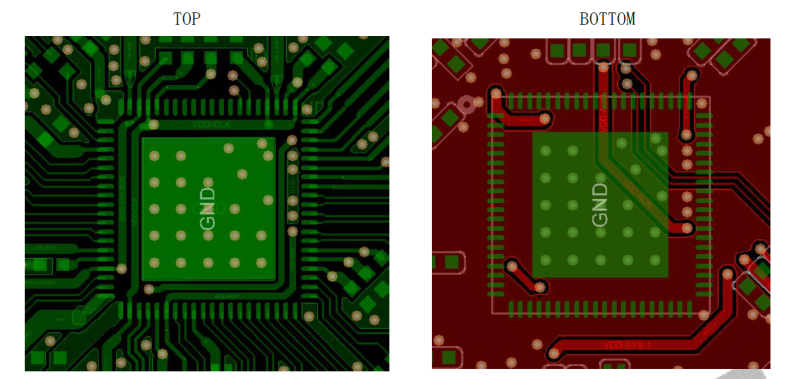

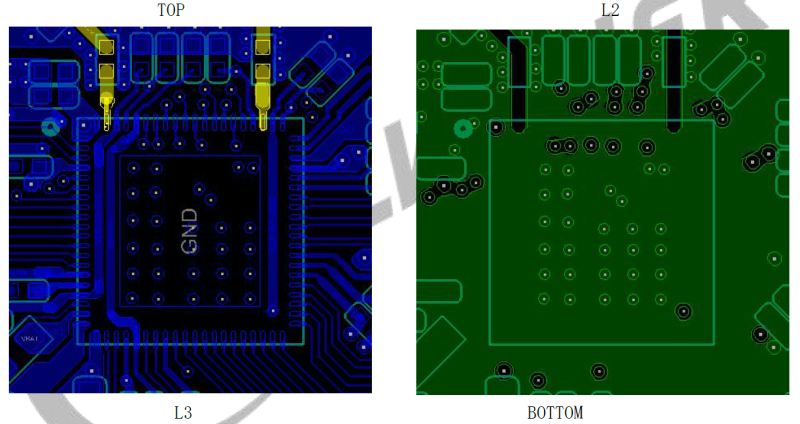

SoC Fanout

R128封裝采用 8x8mm QFN設計,0.35mm ball pitch,0.17mm ball size,可支持 2 層板方案與 4 層板方案。

兩層板 Fanout 建議

- 盡量保證 SOC 背面 GND 完整;

四層板 Fanout 建議

小系統 Layout 設計建議

時鐘系統Layout設計

R128 40Mhz 時鐘建議 Layout 采用以下原則:

- 晶振盡量靠近 IC 擺放,使 HXTAL-OUT/HXTAL-IN 走線長度小于 400mil,減少 PCB走線寄生電容,保證晶振頻偏精度;

- 晶體必須和 SOC放置同一面。避免換層過孔,增加雜散電容而引起頻率偏移;

- 晶振的匹配電容必須靠近晶振管腳擺放;

- 晶振及其走線區域的外圍和相鄰層,用 GND屏蔽保護,禁止其它走線;

- 晶體下方不允許走線,內層或另一面無法避開時不能與時鐘線平行走線。

復位和系統配置Pin Layout 設計

復位和系統配置PIN 建議Layout 采用以下原則:

- SOC 復位信號上拉電阻靠近SOC,復位信號兩邊包地,對地1nF 電容靠近SOC 放置,提高ESD 性能;

SOC 電源Layout 設計

SOC 端電源建議Layout 采用以下原則:

- 每1A 電流對應40mil 線寬(銅厚1oz),電源換層盡量多打Via 孔,保證連接性;

SPI FLASH Layout 設計

- SPI FLASH應靠近主控擺放,走線長度≤2000mil;

- 走線間距≥2倍線寬,CLK 單獨包地處理;

- CLK信號串接電阻靠近主控擺放,串阻與主控連接走線距離≤300mil;

- DATA信號串接電阻為兼顧讀寫方向信號匹配,建議靠近鏈路中間放置。

EMMC Layout 設計

- EMMC與主控間走線長度≤2000mil;線間距≥2W;D0

D3、DS 相對 CLK等長控制+/-300mil 以內;且 D0D3 上使用過孔的數量盡量相同; - 除 Reset 外,保證所有信號線控制阻抗 50? ;

- 電源走線線寬不小于 12mil;

- CLK和 DS 信號盡量包地處理,包地通過過孔與 GND 平面連接。如果不能包地,則保持線間距≥3倍線寬,所有信號避開高頻信號;

- VCCQ, VCC, VDDi的所有去耦電容均靠近 eMMC擺放;

- CLK信號串接電阻靠近主控擺放,串阻與主控 CLK連接走線距離≤300mil;

- DS信號下拉電阻靠近 eMMC擺放。下拉電阻引入樁線長度≤200mil;

請注意:

- eMMC NC/RFU等保留引腳都懸空,不可為了走線方便將這些信號與電源、地、或其他 eMMC信號連接在一起。如果確實走線有困難,可適當修改 eMMC PCB 封裝,去掉一些 NC/RFU 的 ball。

- 如果期望eMMC運行在較高頻率,則建議只使用eMMC,保證主控IO與eMMC點對點連接。如果NAND/eMMC雙 Layout時,走線采用菊花鏈方式,將 eMMC 作為走線的終點,盡量減少分叉線長度

SDIO Layout 設計

SDIO 建議 Layout 采用以下原則:

- CLK串接電阻靠近主控擺放;

- D0~D3相對 CLK等長控制<500mil;

- 走線盡量避開高頻信號,信號線走線參考平面完整;

- 2層板設計時,CLK信號走線要求包地處理。

USB Layout 設計

USB建議 Layout 采用以下原則:

- 阻抗要求:差分 90ohm

- 等長需求:差分對內長度差 50mil內,總長度控制在 4000mil以內;

- USB-5V 按照電流要求走線;

- USB-DM/USB-DP走線的過孔不超過 2個;

- USB-DM/USB-DP建議與其它信號的間距大于 10mil,保證 USB信號參考平面完整,避免走線走在器件下面或者與其他信號交叉;

- TVS器件需要靠近 USB座子擺放;

- USB座子金屬外殼接地管腳 TOP面建議全鋪接地。

音頻 Layout 設計

SOC端音頻部分建議 Layout 采用以下原則:

- AVCC/HPVCC/VRA1/VRA2/AGND接地電容、電阻依次靠近主控擺放;

- PCB走線 AVCC、VRA1、VRA2線寬≥10 mil;線長≤300mil,遠離高速干擾信號;

- AGND走線線寬盡量大,空間允許情況下增加大片覆銅,若耳機座遠離 SOC,建議 AGND 分別在 SOC端和耳機座端放置 0 ohm電阻到地,連接到 GND平面的過孔≥2個。

MIC 建議 Layout 采用以下原則:

- ESD 器件必須靠近 MIC 擺放,從 MIC 引出來的走線必須先經過 ESD器件,在連接其他器件;

- MICxP、MICxN,類差分走線,線寬 4mil,線距 4mil,包地。如果 MIC的濾波電容接地點是 EARCOM,則用 EARCOM 包地;

LCD Layout 設計

RGB建議 Layout 采用以下原則:

- RGB、行場同步、DE等信號參考時鐘做等長處理≤500mil;

- 時鐘信號包地,串電阻靠近主控;

CSI Layout 設計

CSI建議 Layout 采用以下原則:

- PCLK的對地電容靠近主控,串聯電阻靠近模組;

- MCLK的對地電容靠近模組,串聯電阻靠近主控;

- PCLK/MCLK信號包地處理,如空間受限,需保持該信號線在間距≤15mil 空間內無其他走線,盡量與 DATA 線拉開距離;

- 連接時保證較少的換層(MCLK、PCLK換層過孔≤2 個);

- 走線間距大于 2 倍線寬;

- CSI接口走線長度要求控制在 4000mil以內;

- DATA、HSYNC、VSYNC 參考 PCLK做 500mil的組內等長,PCLK盡量不要因為追求等長而走蛇形線;

- PCLK包地需延長到 sensor和 IC近端。PCLK 兩邊不要出現 CSI_DATA 線,遠離高速翻轉的信號線,或用地線隔離。如果 PCLK 和 DATA的 BALL相鄰,則 PCLK和 DATA在出線時就往不同層走。

WIFI 和天線 Layout 設計

WIFI 建議 Layout 采用以下原則:

- 射頻端口盡量靠近天線或天線接口,射頻走線遠離電源、LCD電路、攝像頭、馬達、HPOUT、USB等易產生干擾的模塊;

- 天線饋線阻抗控制 50ohm,為了增大線寬減少損耗,通常饋線相鄰層挖空,隔層參考參考平面需要是完整地,同層地距離天線饋線距離保持一致,兩邊多打地過孔;

- 射頻線需要圓滑走線,不能換層,并進行包地處理,兩邊均勻的打地過孔,射頻線需要遠離時鐘線的干擾;

- 合理布局天線饋線的匹配電容電阻,使饋線平滑,最短,無分支,無過孔,少拐角,避免阻抗突變;

- 如使用 PCB走線作天線,請確保天線走線附近區域完全凈空,凈空區大于 50mm2,天線本體至少距周圍的金屬 1cm以上;

熱設計

熱工作條件

- 熱設計的最主要目的是確保電子設備中元器件的工作溫度低于其最大的許可溫度。

- 元器件的最大許可溫度根據可靠性要求及失效率確定。對于半導體器件和集成電路,主要是控制結溫 Tj,熱設計要保證 Tj≤0.9*Tjmax,其中 Tjmax 是器件的最大許可結溫。

- 對于 R128而言,其 Tjmax=125℃,設計應保證 Tj 應小于 112℃。

散熱設計參考

布局布線的熱設計原則

- 大功耗器件盡量靠近 PCB板上的大面積地層銅箔,借助銅箔散熱;QFN芯片的中間 EPAD是專門設計來散熱的,因此一定要接到地層上;

- PCB 板上功耗大的器件,放在出風口附近;熱敏感器件,放在進風口附近;不要將發熱器件相互靠得太近,更不要將高的元器件擋在功耗大的器件前面;對于功率密度高的器件,建議不要靠壓在PCB 的銅箔上散熱,而要立起來,用散熱器散熱,功耗大的器件立起來自然散熱時,建議將面積大的散熱面與空氣流動方向平行;

- PCB板上的元器件加散熱器時,要注意使散熱器的肋片方向與氣流方向平行,對于確實無法保證這點的,可以使用對氣流方向不敏感的指型散熱器;

- 對模塊內部不能夠吹到風的 PCB 板,在布置元器件時,元器件與元器件之間,元器件與結構件之間應保持一定距離,以利空氣流動,增強對流換熱。

- 在 PCB上布置各種元器件時,應將功率大、發熱量大的元器件放在 PCB邊沿和頂部(重力 top面),以利于散熱;

- 應將不耐熱的元件(如電解電容)放在靠近進風口的位置,而將本身發熱而又耐熱的元件(如電阻,變壓器等)放在靠近出風口的位置;

- 在 PCB上布置各種元器件時,應將功率大、發熱量大的元器件放在出風口的位置;

- 對熱敏感元件,在結構上應采用“熱屏蔽”方法解決:

- 盡可能將熱通路直接連接到熱沉;

- 減少高溫與低溫元器件之間的輻射耦合,加熱屏蔽板,形成熱區和冷區;

- 盡量降低空氣的溫度梯度;

- 將高溫元器件安裝在內表面高黑度,外表面低黑度的機殼中。

- 要保證印制線的載流容量,印制線的寬度必須適于電流的傳導,不能引起超過允許的溫升和壓降。

- 較大的焊盤及大面積銅皮對管腳的散熱十分有利,但在過波峰焊或回流焊時由于銅皮散熱太快,容易造成焊接不良,必須進行隔熱設計,如 GND 花接等,常見的隔熱設計方法如圖所示。

散熱器選擇原則

- 選擇合適的散熱器,不僅與散熱器的大小有關,而且和地域、環境、溫度(季節)、通風條件及安裝密度,模塊工作電流大小等因素有關。

- 接觸面:要求發熱件與散熱器要有良好接觸,盡可能降低接觸熱阻,所以最好有大的接觸面,接觸面還需要有較高的光潔度,為了彌補因接觸面的粗糙而導致的貼合不良,可以在中間涂抹導熱脂,可以有效降低接觸熱阻;

- 導熱材料:銅、鋁都有較好的導熱性能,銅的導熱系數雖然優于鋁,但銅有密度太高、價格貴的缺點,所以實際應用中鋁材是應用最多;

- 固定方式:這個也是比較重要的一環,如果不能把發熱件與散熱片良好接觸,也是無法有效把熱量傳導到散熱器上的,應用中有直接用螺絲釘緊固的,也有用彈簧片壓固的,可以根據需要選擇設計;

- 形狀:包括頁片與基材的形狀尺寸,要有盡可能加大散熱表面積,這樣散熱片的熱量才能快速與周圍空氣對流,比如說增加頁片數目,在頁片上做波浪紋都是好辦法;基材要厚一些比較好,長而薄的散熱片效率很差,在遠端基本上是不起作用的了自然對流:發熱器件或者散熱片的熱量可以是依靠;

- 自然對流散熱:在使用功率器件時最重要的是如何使其產生的熱量有效地散發出去,以獲得高可靠性。散熱的最一般方法是把器件安裝在散熱器上,散熱板將熱量輻射到周圍的空氣中去,以及通過自然對流來散發熱量。

器件安裝的原則

- 元器件的安裝應盡量減少元器件殼與散熱器表面間的熱阻,即接觸熱阻;

- 為盡量減小傳導熱阻,應采用短通路,即盡可能避免采用導熱板或散熱塊把元器件的熱量引到散熱器表面,而元器件直接貼在散熱器表面則是最經濟、最可靠、最有效的散熱措施;

- 為了改善器件與散熱器接觸面的狀況,應在接觸面涂導熱介質,常用的導熱介質有導熱脂、導熱膠、導熱硅油、熱絕緣膠等;

- 對器件須與散熱器絕緣的情況,采用的絕緣材料應同時具有良好的導熱性能,且能夠承受一定的壓力而不被刺穿;

- 把器件裝配在散熱器上時,應控制安裝壓力或力矩進行裝配,壓力不足會使接觸熱阻增加,壓力過大會損壞器件;

- 將大功率混合微型電路芯片安裝在比芯片面積大的散熱片上;

- 對于多層印制線路板,應利用電鍍通孔來減少通過線路板的傳導熱電阻。這些小孔就是熱通路或稱熱道;

- 當利用接觸界面導熱時,采用下列措施使接觸熱阻減到最小。

- 盡可能增大接觸面積;

- 確保接觸表面平滑;

- 利用軟材料接觸;

- 扭緊所有螺栓以加大接觸壓力(注意不應殘留過大應力);

- 利用合理的緊固件設計來保證接觸壓力均勻。

功耗管理參考建議

- 提高電源轉換效率,對于小型化的產品或者對熱設計要求較高的產品,電路設計時推薦采用 DCDC代替 LDO 供電,盡量少用高壓差的 LDO;

- 軟件優化場景功耗,不使用的內部模塊或者外設,可以通過軟件關閉相應模塊的供電;

- 軟件根據應用場景和 VF表實時選擇合適的 CPU工作電壓,以降低芯片功耗;

- 實時監控芯片內部溫度 Sensor,限定芯片最高工作溫度,保護芯片。

EMC設計

ESD設計

原理圖 ESD設計建議參考如下:

- 系統掛死與 IO的抗 ESD能力有關,提高各接口輸入 PIN的 ESD 能力有助于提高系統 ESD,如USB-ID/CARD-DET檢測 PIN到 SOC端串接電阻提高 ESD性能;

- 各接口均要根據接口類型在電源和信號上預留合適的 ESD保護器件;

- Reset信號建議增加 1nF電容接地,電容靠近主控擺放 ;電容接地端需用過孔加強連接;Reset走線需要全程用 GND走線保護;

- 對于模組上的 reset 信號,需在模組上靠近芯片管腳的位置增加 1~100nF 電容接地;

- 關鍵敏感電源采用 LC 濾波設計。

PCB ESD設計建議參考如下:

- PCB層疊設計必須保證比較完整的 GND平面,所有的 ESD泄放路徑直接通過過孔連接到這個完整的GND平面;其他層盡可能多的鋪 GND。

- POWER平面要比 GND平面內縮不少于 3H(H指 POWER平面相對 GND平面的高度)。

- 在 PCB四周增加地保護環。

- 關鍵信號(RESET/Clock等)與板邊距離不小于 5mm,同時必須與走線層的板邊 GND銅皮距離不小于 10mils。

- CPU/晶振等 ESD敏感的關鍵器件,離外部金屬接口的距離不小于 20mm,如果小于 20mm,建議預留金屬屏蔽罩,并且距離其他板邊不小于 5mm。

- 關鍵信號(RESET/Clock等)盡量避免與外部接口信號或經過 IO附近的走線相鄰并行走線;如果不可避免,相鄰并行的走線長度不超過 100mils;IO保護地下方盡量不要走線,在必須走線的情況下建議走內層。

- 無論外部接口信號還是內部信號,走線必須避免多余的樁線。

- 必須保證外部連接器金屬外殼接地良好,在板邊直接通過過孔連接 GND平面,每個 GND焊盤與 GND平面之間的連接過孔不少于 3 個。

- 對于部分 ESD 整改難度較大的 IO,可將 IO GND獨立出來,與主 GND 用磁珠連接以防止靜電能量進入主 GND(需在信號質量可接受的范圍內)。

- 外部接口信號必須連接外部 ESD 器件,進行 ESD保護。如下圖所示,外部接口信號 ESD 器件放置位置盡可能靠近外部連接器,與連接器間避免過孔;ESD器件接地端直接通過過孔連接到 GND平面,而且過孔數量不少于 3 個;從外部接口進來,必須最先看到 ESD器件;ESD器件的信號端與外部信號端必須盡可能短,盡可能寬,建議直接搭接在信號走線上。

軟件 ESD 設計建議參考如下:

- 把不用的 IO 口設置為低電平;

- 加看門狗,對保護的目標狀態位進行檢測。

結構 ESD 設計建議參考如下:

- 建議在 PCB板雙面四周均勻留出多個不小于 25mm2 的 GND裸露銅皮(此銅皮直接通過過孔與 GND平面相連),并通過導電棉與金屬平面相連接;

- 把端口的地與金屬殼相連接而加大 ESD的泄放空間。

- 如果結構允許,建議增加屏蔽罩,對關鍵電路進行屏蔽,同時必須保證屏蔽罩的各邊良好接地;

- (避免屏蔽罩電荷積累,對內部信號放電);

- 螺絲釘要避免伸入機構成為天線;

- 塑膠內層噴導電漆屏蔽。

EMI設計

產品設計設計當初,應了解硬件系統有哪些時鐘信號,對這些信號加以防護,以提高產品 EMI性能,減少后續 DEBUG 成本。

R128 各模塊主時鐘頻率如表所示。

| 接口 | 時鐘 | 時鐘頻率 | 是否支持展頻 |

|---|---|---|---|

| TWI | TWI-SCK | 100K~400 KHz | 支持 |

| IIS | IIS-MCLK | 24.576MHz、22.5792MHz | 支持 |

| SDIO | SDC-CLK | 50MHz、100MHz、150MHz | 支持 |

| SPI | SPI-CLK | 50MHz、100MHz | 支持 |

| USB | DP/DM | 12Mbps、480Mbps | 不支持 |

EMI設計建議參考如下:

- 各接口按照各模塊原理圖和 PCB 設計要求進行。

- 多層板設計時,硬件系統上高速時鐘線建議走內層;且較高速的單端的時鐘線上均要預留 RC濾波電路,抑制高頻分量,對于各模塊時鐘線進行包地處理。

- 差分對信號進行按照差分對要求走線,若無空間,需要滿足 3W 原則。

- 排線座子合理布局,排線下方盡量不要有元器件和 PCB 走線;

- 若受結構限制,排線必須拉得很長,則建議排線座子信號線采用兩兩包地方式,排線必要時要采用帶屏蔽線。

- PCB 背面預留一些空白地位置,使用導電泡棉與機殼金屬接觸,改善地回路;

- 喇叭線采用雙絞線。

Checklist

原理圖設計Checklist

| 模塊 | 序號 | 檢查內容 | 級別 |

|---|---|---|---|

| BLOCK DIAGRAM | 1 | BLOCK DIAGRAM 頁請根據實際產品進行更新 | 建議 |

| POWER TREE | 1 | POWER TREE紅色部分電源具有默認的電壓和上電時序,SOC部分的電源分配不能調整。 | 必須遵守 |

| 2 | 確保FLASH/LCD/TP/EPHY/WIFI等外設的電壓與DCDC、LDO電源電壓匹配。 | 建議 | |

| 3 | 確保DCDC、LDO各路電源的負載能力滿足外設的需求。 | 必須遵守 | |

| 4 | POWER TREE 頁請根據實際產品進行更新 | 建議 | |

| POWER (DCDC、LDO) | 1 | DCDC、LDO選型可以參考原理圖;若使用原理圖選型,電容按推薦設計,不要隨意更改。 | 必須遵守 |

| 2 | DCDC電源電感選型必須滿足該路電源的電流需求。 | 必須遵守 | |

| 3 | 評估好各路電源的工作電壓和最大工作電流,并必須在各路DCDC、LDO電源上標注清楚,以便PCB layout設計走線。 | 必須遵守 | |

| 4 | VDD_IO1、VDD_IO2、VDD_IO_5VTOL在使用外部DCDC/LDO進行供電時,為避免時序錯誤造成IC漏電,必須使用VDD_3V3電源對外部DCDC/LDO進行時序控制。 | 必須遵守 | |

| 5 | VDD_DSP電源建議預留一路外部LDO進行供電。 | 建議 | |

| 6 | 若有其特殊待機場景或者供電需求,請列出讓全志FAE確認。 | 必須遵守 | |

| SOC | 1 | 晶振部分的電路設計必須符合參考設計,串并接電阻不能刪除,并聯電容不能隨意更改。 | 必須遵守 |

| 2 | 選用的晶振工作溫度必須符合產品設計工作溫度。 | 建議 | |

| 3 | SOC部分的電源濾波電容必須與參考設計相同,不能修改容值,也不能刪減個數,且要備注靠近SOC pin放置。 | 必須遵守 | |

| 5 | CHIP-PWD和RESET信號上必須接1nF下地電容,靠近SOC PIN放置。 | 必須遵守 | |

| 6 | 為避免SOC啟動時誤進入升級狀態,PA1/FEL0和PA2/FEL1 不能同時接下拉對地電阻。 | 必須遵守 | |

| 7 | SOC的系統功能配置腳必須正確無誤,無特殊需求可以保持與標案設計一致。 | 必須遵守 | |

| 8 | GPIO口使用時,需確保GPIO口電平匹配,若需要加上拉電阻,需保證上拉電壓為其供電電壓域,防止有漏電情況發生。 | 必須遵守 | |

| FLASH | 1 | R128-S1/S2默認使用內置FLASH,此時VDD-IO1必須使用3.3V電源。 | 必須遵守 |

| 2 | R128-S3無內置FLASH,必須使用外置FLASH、EMMC器件,建議使用PB口作為存儲介質啟動端口。 | 建議 | |

| 3 | R128可通過boot_sel燒碼選擇不同的啟動介質與啟動端口,具體燒碼值建議聯系全志FAE。 | 建議 | |

| 4 | FLASH、EMMC的物料選型必須采用全志AVL支持列表里面的型號。 | 建議 | |

| RGB | 1 | R128支持RGB接口,使用時需保證LCD的IO電壓與SOC端的IO電壓保持一致,若不一致,必須做電平轉換處理,建議使用3.3V IO電平。 | 必須遵守 |

| 2 | 確保LCD的背光電路與LCD的規格匹配,反饋電路必須采用精度為1%的電阻,電流采樣電阻精度必須為1%,封裝滿足功率需求。 | 必須遵守 | |

| 3 | 確保LCD的正負壓電源與LCD的規格匹配。 | 必須遵守 | |

| 4 | 必須在原理圖中標注清楚LCD部分電源的工作電壓和最大工作電流,以便PCB layout設計。 | 建議 | |

| CTP | 1 | CTP的I2C必須接上拉電阻,CTP與SOC的IO電平必須匹配。 | 必須遵守 |

| 2 | CTP的供電合理,不能存在漏電情況。 | 必須遵守 | |

| AUDIO | 1 | AVCC/VRA1/VRA2的AGND通過0R電阻單點到GND | 必須遵守 |

| 2 | Audio codec所有外圍電阻以及電容的參數不能修改。 | 必須遵守 | |

| 3 | 所有喇叭、LINEIN、MIC接口必須接ESD器件,且靠近座子擺放。 | 建議 | |

| 4 | 單喇叭的默認使用LINEOUTLP/N信號。 | 必須遵守 | |

| 5 | MIC單端或差分配置是否正確。 | 必須遵守 | |

| 6 | 功放的使能腳必須要有下拉電阻,推薦值為100K。 | 必須遵守 | |

| 7 | 建議在原理圖中標注清楚AUDIO部分電源的工作電壓和最大工作電流,以便PCB layout設計。 | 建議 | |

| USB | 1 | USB接口支持OTG/HOST功能,USB電源建議通過限流開關進行控制。 | 建議 |

| 2 | USB接口必須掛ESD器件,USB D+/D-必須使用容抗小于5PF的ESD器件。 | 必須遵守 | |

| 3 | USB-DP/DM建議預留串接電阻位置,建議阻值5Ω。 | 建議 | |

| 4 | USB具有OTG功能,USB-ID的設計必須參考標案原理圖設計。 | 建議 | |

| 5 | 必須在原理圖中標注清楚USB信號線的走線阻抗要求,以便PCB layout設計。 | 建議 | |

| 6 | 必須在原理圖中標注清楚USB電源的最大工作電流,以便PCB layout設計。 | 建議 | |

| CARD | 1 | SDC0-CLK信號需串接33R電阻,并靠近SOC擺放。 | 必須遵守 |

| 2 | SDC0所有信號都不需要外接上拉,禁止使用外部上拉。 | 建議 | |

| 3 | SD接口所有信號需掛ESD器件,若支持SD3.0高速模式,其中CLK、CMD、DATA信號的ESD器件容抗必須小于5PF。SD2.0需小于35PF。 | 必須遵守 | |

| 4 | Card-DET信號建議串1K電阻,提高系統ESD | 必須遵守 | |

| 5 | 建議在原理圖中標注清楚TF卡信號線的走線阻抗要求,以便PCB layout設計。 | 建議 | |

| 6 | 建議在原理圖中標注清楚CARD電源的最大工作電流,以便PCB layout設計。 | 建議 | |

| WIFI/BT | 1 | WIFI射頻走線需靠近天線部分,要求平滑走線,遠離電源、LCD電路、攝像頭、馬達、功放、USB等易產生干擾的模塊。 | 必須遵守 |

| 2 | 天線饋線阻抗控制50ohm,為了增大線寬減少損耗,通常饋線相鄰層挖空,隔層參考參考平面需要是完整地,同層地距離天線饋線距離保持一致,兩邊多打地過孔; | 必須遵守 | |

| 3 | WiFi的天線需預留π型濾波電路,便于天線匹配調試。 | 必須遵守 | |

| 4 | 必須在原理圖中標注清楚射頻信號線的走線阻抗要求,以便PCB layout設計。 | 建議 | |

| KEY | 1 | GPADC網絡的采樣范圍為0-1.08V,需保證任意兩個按鍵按下時GPADC電壓差必須>=0.2V。 | 必須遵守 |

| 2 | GPADC按鍵阻值建議和參考設計保持一致,采用1%的高精度電阻; | 必須遵守 | |

| 4 | GPADC按鍵建議保留去抖電容和ESD器件。 | 建議 | |

| 5 | FEL、RESET按鍵建議保留去抖電容和ESD器件。 | 建議 | |

| DEBUG | 1 | UART0調試接口必須保留,建議串接100ohm電阻。 | 必須遵守 |

| 2 | JTAG調試接口預留測試點 | 建議 | |

| ESD | 1 | 復位信號在靠近AP端,必須保留一個對GND的濾波電容,容值固定選擇1nF。 | 建議 |

| 2 | 部分與外部直連或者裸露的接口,如speaker、MIC、耳機、USB、TF、DCIN等,必須加上ESD器件 。 | 必須遵守 | |

| 3 | 所有按鍵必須掛ESD器件。 | 必須遵守 | |

| DRC | 1 | 所有電氣規格檢查必須無ERROR,所有WARNING與QUESTION必須逐一確認合理,不合理的問題項需要優化處理。 | 建議 |

| 2 | 所有物理規格檢查必須無ERROR,所有WARNING與QUESTION必須逐一確認合理,不合理的問題項需要優化處理。 | 建議 |

PCB設計 Checklist

| 模塊 | 序號 | 檢查內容 | 級別 |

|---|---|---|---|

| 基本要求 | 1 | 主控以及配套芯片封裝是否有更改; | 必須遵守 |

| 2 | PCB 的疊層參數與阻抗控制 | 必須遵守 | |

| SOC | 3 | 晶振盡量靠近 IC 擺放,走線長度小于 400mil; | 必須遵守 |

| 4 | 晶振及其走線區域的外圍和相鄰層,用 GND 屏蔽保護。晶振及其走線區域的相鄰層,禁止其它走線; | 必須遵守 | |

| 5 | 所有模塊的CLK串接電阻(SDC0-CLK/CARD-CLK/LCD-CLK)靠近主控擺放,串阻與主控CLK連接走線距離≤300mil; | 必須遵守 | |

| 6 | 關鍵信號(EN,FEL等)單線包地,遠離板邊≥5mm。避免與外部接口信號(USB/SD/等)相鄰并行走線;電容靠近主控擺放。 | 必須遵守 | |

| 電源 | 7 | 電源銅箔盡量寬,換層過孔是否足夠,一般定義1oz銅厚,寬度40mil銅箔可通過1A電流,V8X16的Via過0.5A電流。 | 必須遵守 |

| EMMC | 8 | CLK和DS信號做包地處理,如果不能包地則保持3W間距; | 必須遵守 |

| 9 | D0~D3、DS相對CLK等長控制≤300mil; | 必須遵守 | |

| 10 | CLK 串接 33R 電阻靠近主控擺放,串阻與主控 CLK 連接走線距離≤300mil; | 必須遵守 | |

| 11 | DS 下拉電阻靠近 EMMC 擺放。下拉電阻引入樁線長度≤200mil。 | 必須遵守 | |

| SD-SDIO | 12 | CLK做包地處理,如果不能包地則保持3W間距; | 必須遵守 |

| 13 | D0~D3相對CLK等長控制<500mil; | 必須遵守 | |

| 14 | CLK 串接 電阻靠近主控擺放,串阻與主控 CLK 連接走線距離≤300mil。 | 必須遵守 | |

| USB2.0 | 15 | 去耦電容和濾波電容,需要靠近IC擺放,接口ESD器件靠近連接器端擺放,且ESD器件與連接器的傳輸線長度要小于等于500mils。SS_TX串接的電容應靠近IC端擺放; | 必須遵守 |

| 16 | USB信號線DNDP長度差50mil內,總長度控制在4000mil以內 | 必須遵守 | |

| 音頻 | 17 | AVCC、VRP、VRA1、VRA2和AGND接地電容、電阻靠近主控擺放; | 必須遵守 |

| 18 | ESD 器件必須靠近MIC擺放,從MIC引出來的走線必須先經過ESD器件; | 必須遵守 | |

| 19 | MICxP、MICxN,類差分走線,線寬4mil,線距4mil,包地。 | 必須遵守 | |

| WIFI/BT | 20 | WiFi模組盡量靠近天線或天線接口。遠離電源、LCD電路、攝像頭、SPEAKER等易產生干擾的模塊。 | 必須遵守 |

| 21 | 射頻線需要圓滑,不能換層,并進行包地處理,兩邊均勻的打地過孔,射頻線需要遠離時鐘線的干擾; | 必須遵守 | |

| 22 | 合理布局天線饋線的匹配電容電阻,使饋線平滑,最短,無分支,無過孔,少拐角,避免阻抗突變; | 必須遵守 | |

| 23 | 用PCB走線作天線,請確保天線走線附近區域完全凈空,凈空區大于50mm2,天線本體至少距周圍的金屬1cm以上。 | 必須遵守 | |

| SPI/FLASH | 24 | SPI、FLASH應靠近主控擺放,走線長度≦2000mil; | 必須遵守 |

| 25 | 走線間距≧2倍線寬,CLK單獨包地處理; | 必須遵守 | |

| 26 | 時鐘信號串接電阻靠近阻抗擺放,串阻與主控連接走線距離≦300mil。 | 必須遵守 | |

| 27 | 數據信號串接電阻為兼顧讀寫方向信號匹配,建議靠近鏈路中間放置。 | 建議 | |

| 28 | 使用4線FLASH時,要求MISO/MOSI/WP/HOLD信號等長約束控制在300mil以內 | 必須遵守 | |

| CSI | 28 | PLCK對地電容靠近主控,串聯電阻靠近模組; | 必須遵守 |

| 29 | MCLK對地電容靠近模組,串聯電阻靠近主控; | 必須遵守 | |

| 30 | HSync對地電容靠近主控; | 必須遵守 | |

| 31 | VSync、HSync、Data串聯電阻靠近模組。 | 必須遵守 | |

| ESD | 32 | 關鍵信號(RESET/Clock等)單線包地,遠離板邊≥5mm。避免與外部接口信號(USB/SD/等)相鄰并行走線; | 必須遵守 |

| 33 | reset單線包地,1nF電容靠近主控擺放,電容接地端需用過孔加強連接; | 必須遵守 | |

| 34 | 在PCB四周增加地保護環;DDR線束四周建議用GND保護; | 必須遵守 | |

| 35 | 部分與外部直連或者裸露的接口,如speaker、MIC、耳機、USB、SD等,必須加上ESD器件 ,走線路徑為先經過ESD器件再到SOC。 | 必須遵守 |

審核編輯 黃宇

-

mcu

+關注

關注

146文章

17123瀏覽量

350992 -

硬件設計

+關注

關注

18文章

396瀏覽量

44564 -

R128

+關注

關注

0文章

41瀏覽量

105

發布評論請先 登錄

相關推薦

DshanMCU-R128s2-DEVKIT應用開發案例

DshanMCU-R128s2芯片參數

DshanMCU-R128s2芯片手冊與資料

DshanMCU-R128s2 R128 模組

DshanMCU-R128s2 R128 DevKit 開發板

DshanMCU-R128s2 SDK 架構與目錄結構

DshanMCU-R128s2 Hello World!

DshanMCU-R128s2 配置引腳復用

DshanMCU-R128s2啟動與資源劃分

DshanMCU-R128s2硬件設計指南

DshanMCU-R128s2硬件設計指南

評論