硬件術語

| 術語 | 解釋說明 |

|---|---|

| sunxi | 指 Allwinner 的一系列 SOC 硬件平臺 |

| M33 Star | 基于 ARMv8-M 架構 32 位元微處理器單元 |

| C906 | 平頭哥推出的一款 RISC-V 架構的 64 位元處理器單元 |

| HIFI5 | Cadence 推出的 Cadence Tensilica HiFi 5 DSP 32 位處理器單元 |

| R128 | 全志推出的一款包含 M33+C906+HIFI5 處理器的 SoC 平臺 |

| AudioCodec | 芯片內置音頻接口 |

| I2S/PCM | 外置數字音頻接口,常用于外接codec 模塊。 |

| AHUB | 音頻集線器,內部集成I2S 接口及DAM 混音器,可實現多路輸入播放及硬件混音功能 |

| S/PDIF | 外置音響音頻設備接口,一般使用同軸電纜或光纖接口。 |

| DMIC | 外置數字MIC 接口 |

| MAD | Mic Activity Detector, 語音能量檢測模塊 |

| 同源播放 | 不同音頻模塊同時播放同一份音頻數據 |

| 同步采樣 | 不同音頻模塊同時錄音(可消除線程調度時差影響) |

軟件術語

| 術語 | 解釋說明 |

|---|---|

| FreeRTOS | 一種開源的實時操作系統 |

| gcc | GNU 開發的編程語言編譯器。用于編譯 M33 與 C906 上運行的程序 |

| xcc | Xtensa C/C++ 編譯器。用于編譯在 HIFI5 運行的程序 |

| hwspinlock | 在多核系統中,hwspinlock 提供一種硬件鎖同步機制。 |

| ALSA | Advanced Linux Sound Architecture |

| ASoC | ALSA System on Chip |

| DAPM | 動態音頻電源管理 |

| samplebit | 樣本精度,記錄音頻數據最基本的單位,常見的有 16 位 |

| channel | 通道數,該參數為 1 表示單聲道,2 表示立體聲,大于 2 表示多聲道 |

| rate | 采樣率,每秒鐘采樣次數,該次數是針對幀而言。 |

| frame | 幀,記錄了一個聲音單元,其長度為樣本長度與通道數的乘積。 |

| period size | 每次硬件中斷處理音頻數據的幀數。 |

| period count | 處理完一個 buffer 數據所需的硬件中斷次數。 |

| buffer size | 數據緩沖區大小 (period size * period count) |

| DRC | 音頻輸出動態范圍控制 |

| HPF | 高通濾波 |

| XRUN | 音頻流異常狀態,分為 underrun 和 overrun 兩種狀態。 |

| 交錯模式 | 一種音頻數據記錄模式,數據以連續幀形式存放 (幀 1_L, 幀 1_R, 幀 2_L, 幀 2_R, —)。 |

| 非交錯模式 | 一種音頻數據記錄模式,數據是以連續通道形式存放 (L-幀 1, L-幀 2, —, R-幀 2, R-幀 2, —)。 |

| tinyalsa | 在 Linux/RTOS 內核中與 ALSA 接口對接的庫,可用于基本播錄。 |

| alsalib | 在 Linux/RTOS 內核中與 ALSA 接口對接的庫,可用于基本播錄,并可與常見音頻算法組合使用。 |

審核編輯 黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

mcu

+關注

關注

146文章

17123瀏覽量

350992 -

R128

+關注

關注

0文章

41瀏覽量

105

發布評論請先 登錄

相關推薦

ADC128S052、ADC128S052-Q1模數轉換器數據表

電子發燒友網站提供《ADC128S052、ADC128S052-Q1模數轉換器數據表.pdf》資料免費下載

發表于 07-22 11:12

?0次下載

全志R128 SDK架構與目錄結構

│├── bin# R128 S2 Module 固件,引導等bin│├── configs # R128 S2 Module 配置文件,引腳復用,分區

發表于 01-05 10:05

全志R128硬件設計指南①

Pin放置 ESD器件。

SD卡座電源 VDD預留串聯 0R電阻,防止卡插入時,瞬間大電流燒卡。

音頻電路設計

3個 ADC,可支持 3 個差分 MIC 輸入;

2個 DAC,R128-S1/

發表于 01-04 09:23

全志R128入門編寫HelloWorld

方案選擇r128s2_module_c906

code">$ source envsetup.sh $ lunch_rtos 1

編輯程序打開你喜歡的編輯器

發表于 12-29 09:39

DshanMCU-R128s2 R128 模組

R128-S2-N16R16 R128-S2 Arm Cortex-M33 C906 RISC-V HIFI5 DSP 1MByte 8Mbyte 8Mbyte 16M NOR Flash 2 Audio

DshanMCU-R128s2芯片手冊與資料

: Xplorer Software (SDK) Download Xtensa Xplorer 授權申請: Cadence Tensilica Offerings Xtensa Xplorer 試用申請: request an evaluation license 其余手冊將在R128芯片正式發布后上傳

DshanMCU-R128s2芯片參數

MB LS PSRAM R128 S2)/8 channels (R128 S3) - One LEDC used to control the external intellige

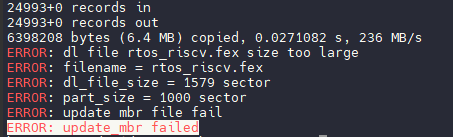

DshanMCU-R128s2常見問題

) copied, 0.0271082 s, 236 MB/sERROR: dl file rtos_riscv.fex size too largeERROR: filename

DshanMCU-R128s2芯片外設支持列表

LCD 顯示屏 廠商 分辨率 型號 接口 FPS 100ask 480 x 320 Dshan_Display Module SPI 60 攝像頭 Sensor 廠商 分辨率 型號 Size 接口 FPS GalaxyCore VGA, 640 x 480 GC0308 1/6.5 DVP 30 GalaxyCore UXGA, 1616 x 1232 GC2145 1/5 DVP 13

DshanMCU-R128s2硬件設計參考

R128 DevKit 開發板 硬件工程開源地址:https://oshwhub.com/gloomyghost/r128-module 電路圖

開源項目!教你如何復刻自平衡賽車機器人、智能家居中控、競技機器人先進模糊控制器等

適配的的Arduino控制板移植為DShanMCU-R128s2-DevKit開發板,與此同時還添加了一些功能,比如自平衡功能、WiFi&藍牙控制、App控制以及語音控制功能,讓平衡

發表于 12-26 09:17

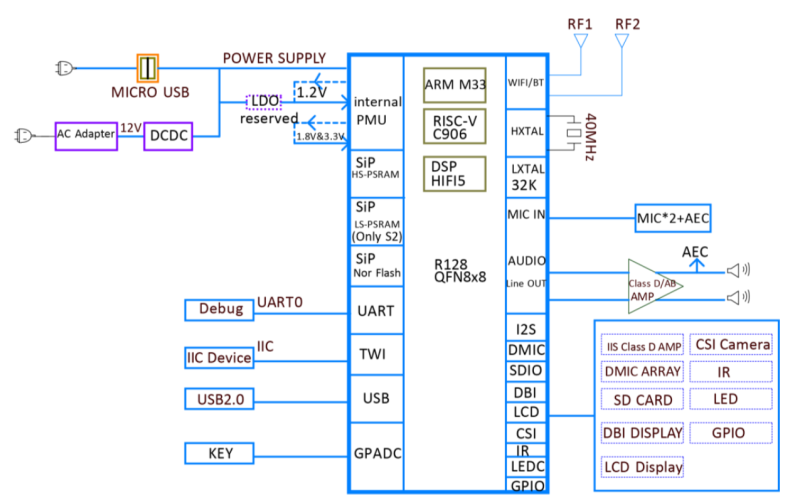

DshanMCU-R128s2硬件設計指南

原理圖設計 硬件系統框圖 R128是一顆專為“音視頻解碼”而打造的全新高集成度 SoC,主要應用于智能物聯和專用語音交互處理解決方案。 單片集成 MCU+RISCV+DSP+CODEC+WIFI

DshanMCU-R128s2術語表

DshanMCU-R128s2術語表

評論