在經歷了近十年和五個主要節點以及一系列半節點之后,半導體制造業將開始從 FinFET過渡到3nm技術節點上的全柵堆疊納米片晶體管架構。

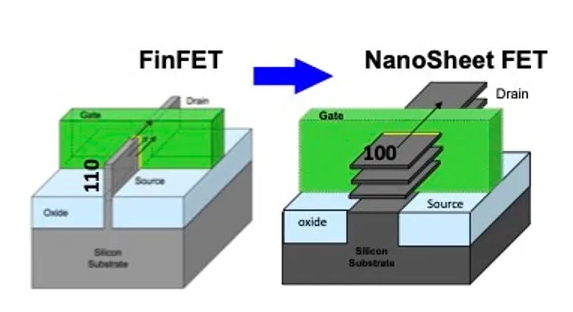

相對于FinFET,納米片晶體管通過在相同的電路占位面積中增加溝道寬度來提供更多的驅動電流(圖1),其環柵設計改善了通道控制并較大限度地減少了短通道效應。

圖1:在納米片晶體管中,柵極在所有側面接觸溝道,可實現比finFET更高的驅動電流

圖1:在納米片晶體管中,柵極在所有側面接觸溝道,可實現比finFET更高的驅動電流從表面上看,納米片晶體管類似于FinFET,但納米片通道與基板平行排列,而不是垂直排列。納米片晶體管制造從沉積Si/SiGe異質結構開始,與襯底隔離以防止寄生傳導。

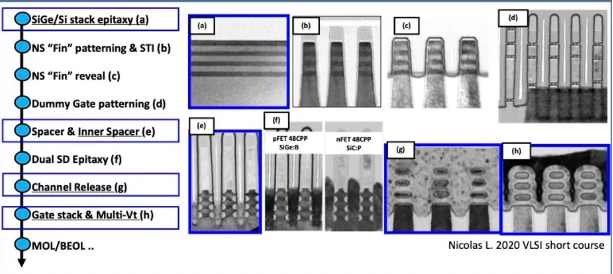

在偽柵極制造之后,內部間隔物蝕刻步驟在SiGe層中切割凹槽。內部間隔蝕刻步驟是一個關鍵的工藝步驟,因為它定義了柵極長度和源/漏結重疊。

構建晶體管支柱

即使SiGe層不是成品器件的一部分,但它們的鍺濃度仍然是一個重要的工藝變量,增加鍺的量會增加SiGe晶格常數,這反過來又會增加硅層中的晶格應變,從而引入缺陷。另一方面,如果我們要在不損壞或侵蝕硅的情況下完全去除SiGe材料,則需要具有高SiGe:Si選擇性的蝕刻工藝。

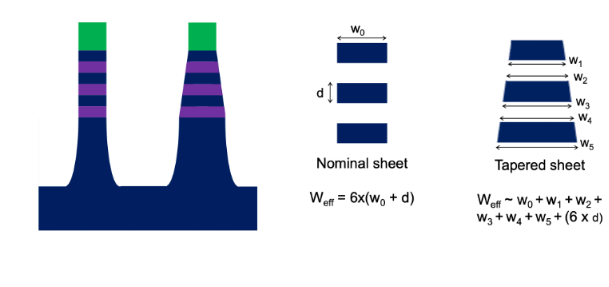

在理想情況下,英思特公司希望盡可能小化納米片之間的間距從而減少寄生電容。因為一旦SiGe消失,納米片之間的空間則需要容納更多的殘留物。在Si/SiGe異質結構沉積之后,各向異性蝕刻需要切割到所需寬度的柱體。

圖2:蝕刻輪廓直接影響晶體管行為和器件操作的一致性定義通道

圖2:蝕刻輪廓直接影響晶體管行為和器件操作的一致性定義通道定義通道

一旦納米片柱被定義,高選擇性各向同性蝕刻就會創建內部間隔凹陷,這個間隔物定義了柵極長度和結重疊,這兩者都是關鍵的晶體管參數,有助于定義器件電阻和電容之間的權衡。濕化學蝕刻工藝往往會留下半月形輪廓,因為兩個相鄰的納米片之間會形成彎月面。在溝道釋放蝕刻期間去除剩余的SiGe可以暴露源極/漏極,并將它們與柵極金屬直接接觸。

圖3:納米片晶體管工藝流程中的關鍵蝕刻步驟

圖3:納米片晶體管工藝流程中的關鍵蝕刻步驟

雖然干法蝕刻工藝沒有留下半月板,但英思特公司仍然觀察到圓形蝕刻前端,并確定了其Si/SiGe柱側壁上的富鍺層。該層顯然是在各向異性柱蝕刻期間形成的,其蝕刻速度更快,導致圓形蝕刻前端。

審核編輯 黃宇

-

晶體管

+關注

關注

77文章

9682瀏覽量

138083 -

蝕刻

+關注

關注

9文章

413瀏覽量

15368

發布評論請先 登錄

相關推薦

TMD或將取代Si,下一代半導體材料來襲

GaN晶體管和SiC晶體管有什么不同

24芯M16插頭在下一代技術中的潛力

下一代晶體管有何不同

下一代晶體管有何不同

評論