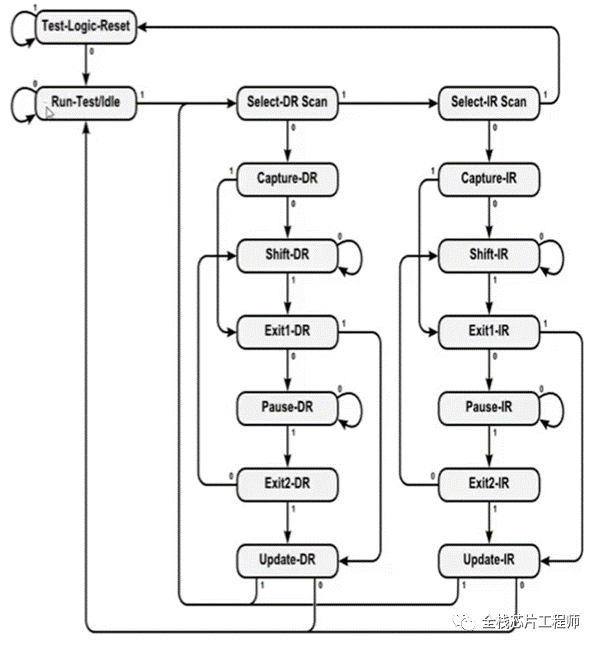

請問,JTAG有5個端口,為什么Trst是可選的復位端口?

請問,JTAG只保留4個端口,沒有Trst,怎么復位?

答:第一個問題,很簡單,因為Trst可以用Tms來替換。那么第二個問題呢?歡迎來知識星球討論。

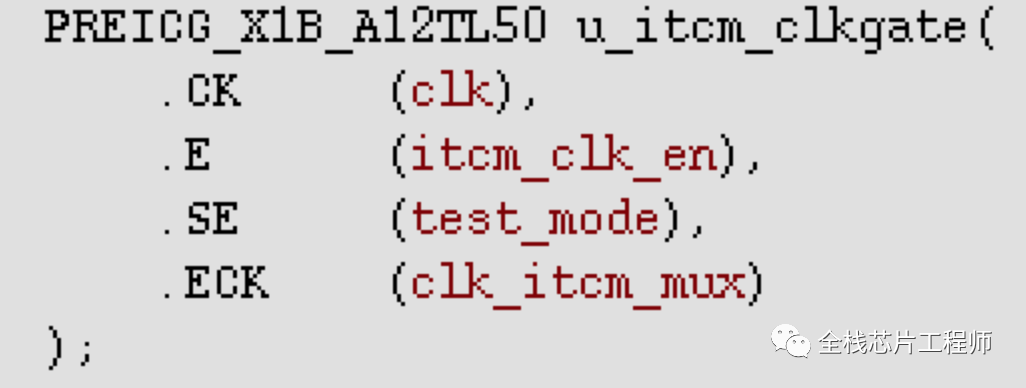

請問,MCU芯片設計添加了mbist、scan chain之后,仿真失敗怎么辦?首先diff代碼,看代碼改動了什么,是否改正確,然后做2-3個formal/lec檢查,保證DFT實現過程不改變function 功能。此外還要注意頂層的dft端口控制信號是否在testbench中正確例化等等,比如注意jtag端口可做cpu debug,可做mbist測試,注意tdo輸出選擇控制。

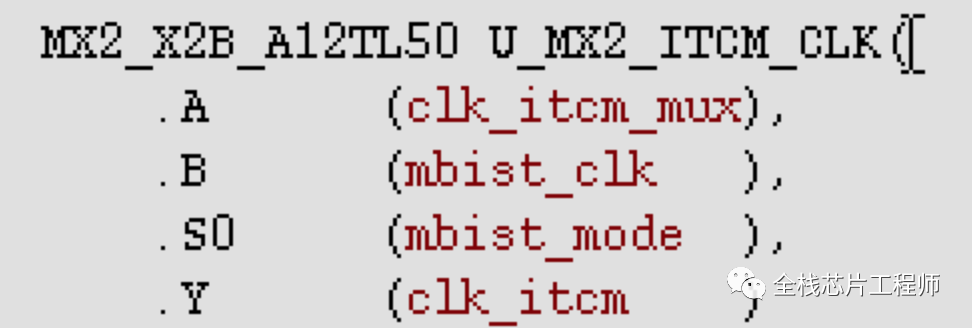

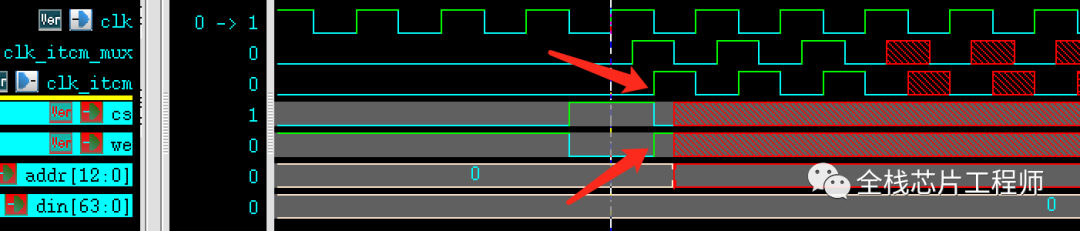

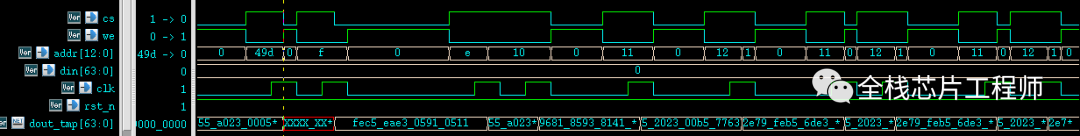

回到正題,DFT插入后,由于增加了大量的mux來完成時鐘、復位可控,導致中端網標中的cell有工藝庫文件指定的delay參數,默認是1ns,那么會造成clk delay,比如插入兩級mux就會形成2ns延時,而我們的mcu運行時鐘是250mhz,時鐘周期4ns,sram時鐘再取個反,剛好易造成sram timing問題,sram輸出x態,cpu取指令失敗。

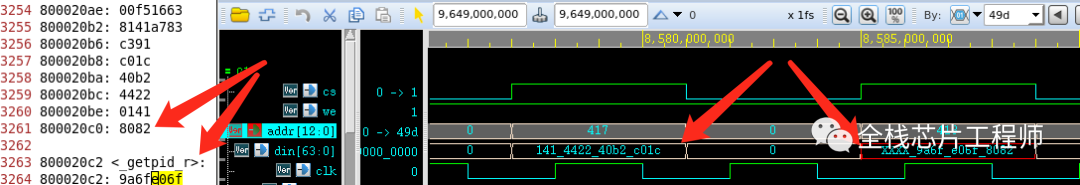

如下,cs/we等sram控制信號剛好和sram的時鐘對齊,造成sram model輸出x態,cpu去取指令失敗,mcu boot失敗。

景芯SoC訓練營得同學都知道,或熟悉DFT仿真得同學都知道,vcs這里仿真應該加一個option,不知道得趕緊找我!

可以先強行force時鐘,選一個可以采樣cs/we等sram控制信號的時鐘給sram,好巧不好,cpu執行了一部分指令,又停止了,繼續定位。

發現程序末尾有x態哦,發現x態,同學們會問,指令為什么會有x態,肯定是bug或timing問題造成的吧,我們接著看:

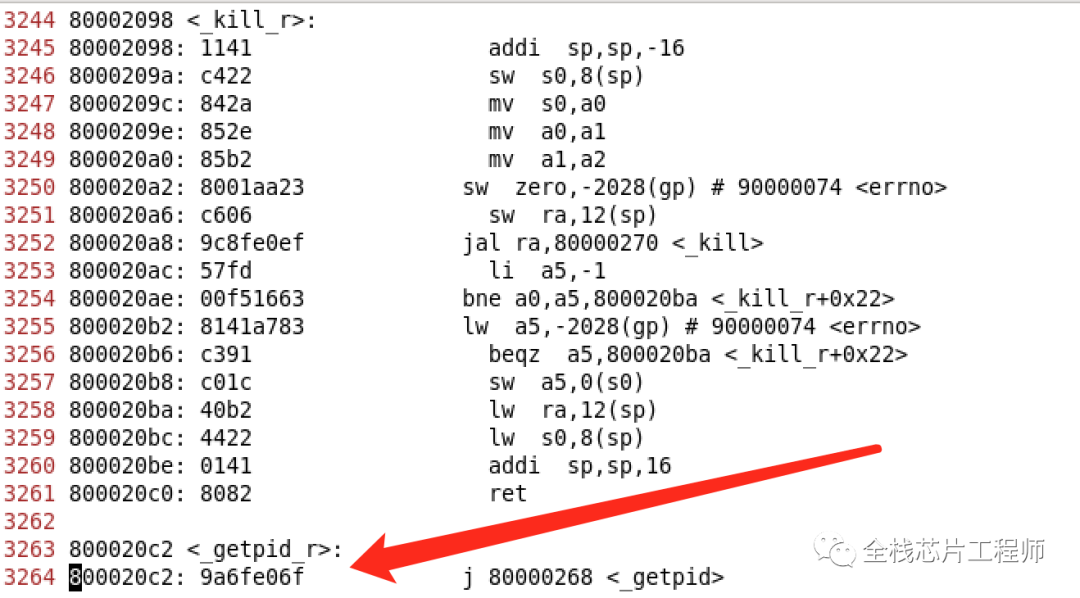

而上面x態是由于cpu有16位指令,并且程序有跳轉,那么為什么cpu執行指令一部分后就停止了呢?是我把cpu取指令模塊改錯了?于是開始看cpu代碼。。。

實際上x態后程序依然能正確執行,本質上是16位指令及程序調轉的原因。接著debug。

接著定位,發現是取指令握手卡住,解決辦法?后仿真怎么確保時鐘對齊的問題?答案參見全棧芯片工程師【知識星球】。

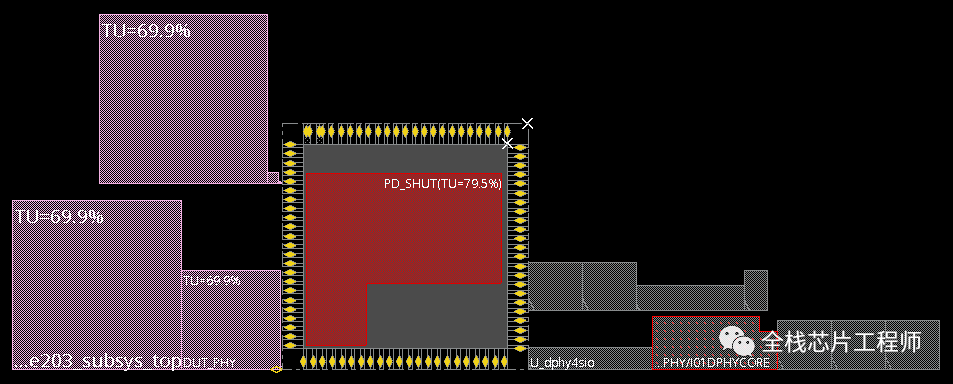

挑戰!全芯片UPF低功耗設計(含DFT設計)

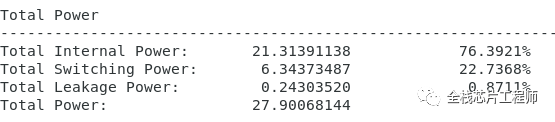

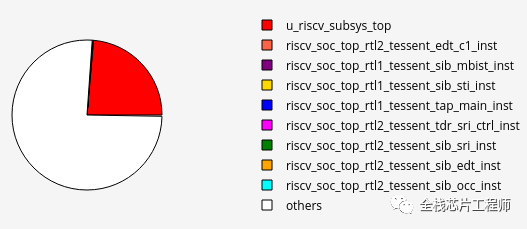

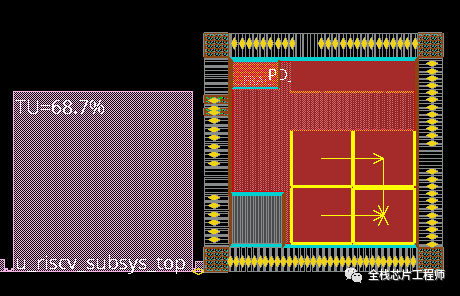

景芯SoC訓練營培訓項目,低功耗設計前,功耗為27.9mW。

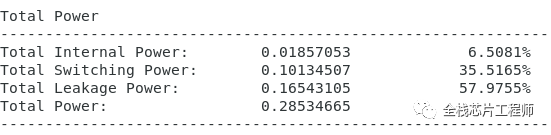

低功耗設計后,功耗為0.285mW,功耗降低98.9%!

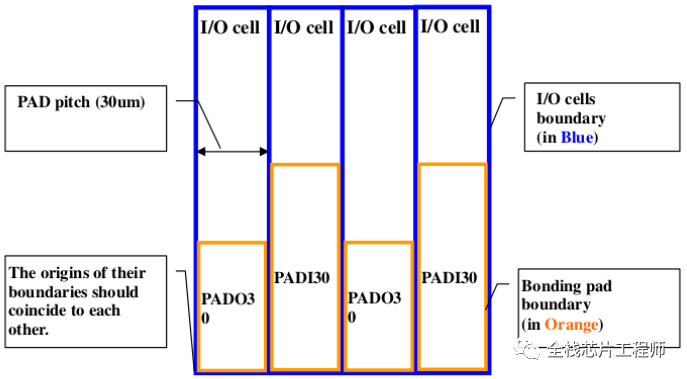

7天沖刺PR訓練營有同學問如何給IO添加PAD?請思考景芯SoC的IO和PAD如何實現最佳?

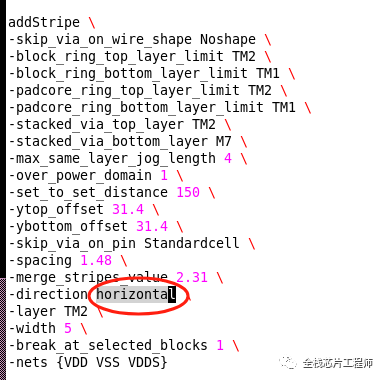

7天沖刺PR訓練營有同學問,同樣的floorplan,有些同學很快跑完,有些同學則遇到大量DRC問題(EDA工具不停iteration)導致工具始終無法跑完,具體什么問題呢?

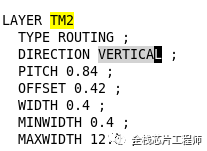

首先,小編發現該同學的stripe把TM2定義為了horizontal,而熟悉景芯工藝的同學知道,TM2的preference direction是VERTICAL。

查詢景芯的lef庫文件也可以確認:

用錯方向有多大影響呢?大家上景芯SoC的后端flow實踐一下吧,實踐出真知。

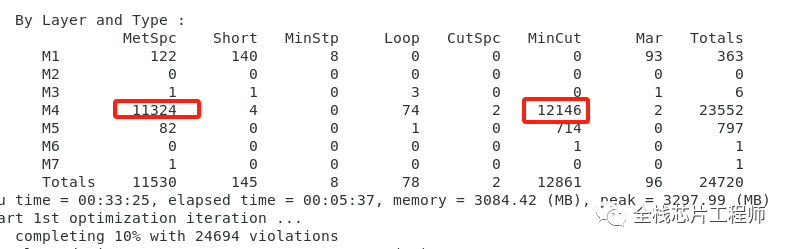

7天沖刺PR訓練營有同學問,為啥PR花了一天一夜24個小時完成布線還大量DRC錯誤?小編已經將設計規模盡可能減小以加速PR設計,實際上2小時就可以跑完routing,為何這么慢?原因就是低功耗單元的走線。具體原因及解決辦法歡迎加入景芯訓練營討論。

其錯誤主要集中在M4上,請思考如何解決。

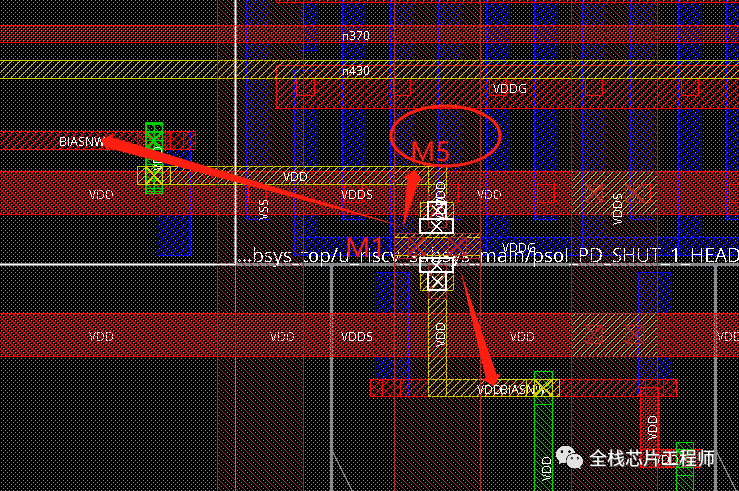

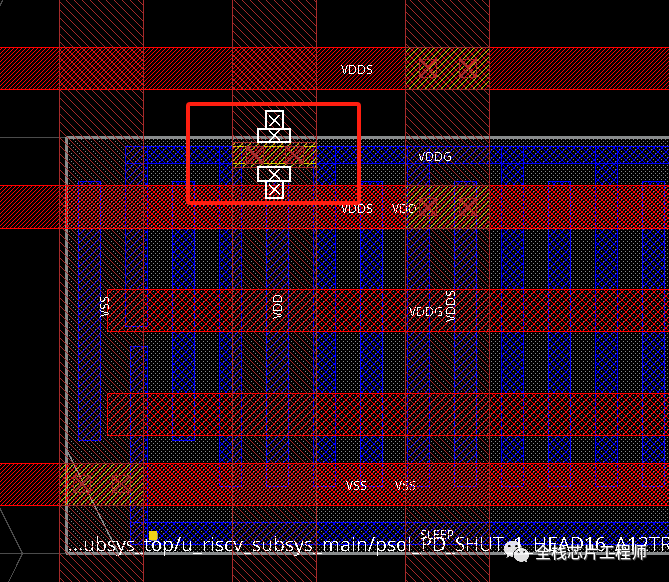

7天沖刺PR訓練營有同學問,power switch cell的secondPG pin(VDDG)從M1接出的,而不是M2, 請思考有什么問題?如何解決?

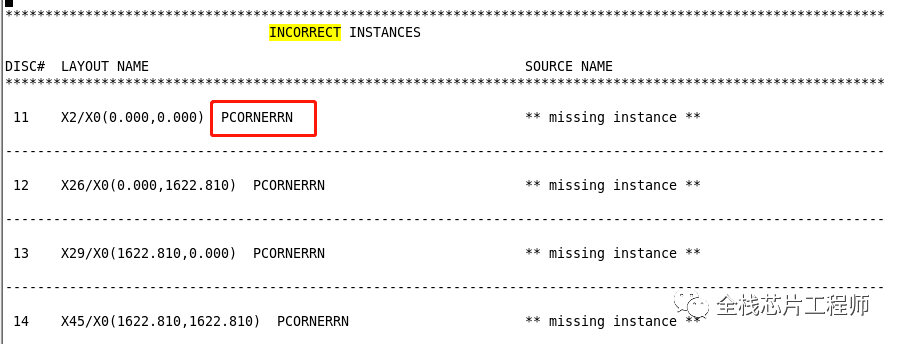

7天沖刺PR訓練營有同學問,景芯SoC培訓營同學遇到Corner Pad LVS不過怎么處理?

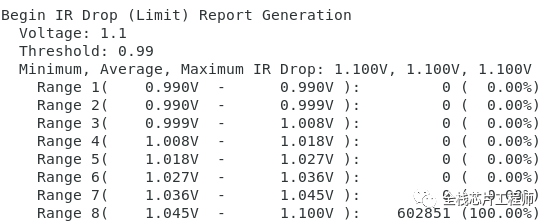

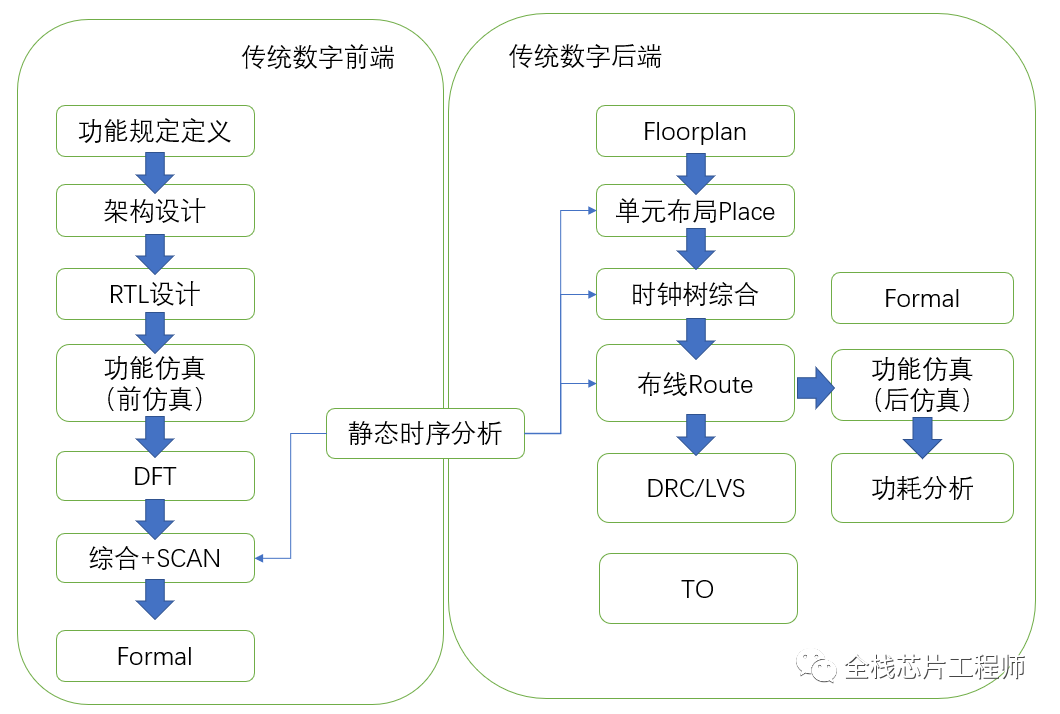

完成景芯SoC培訓的前端設計仿真、DFT后,我們來到后端flow,本教程教你一鍵式跑完數字后端flow。

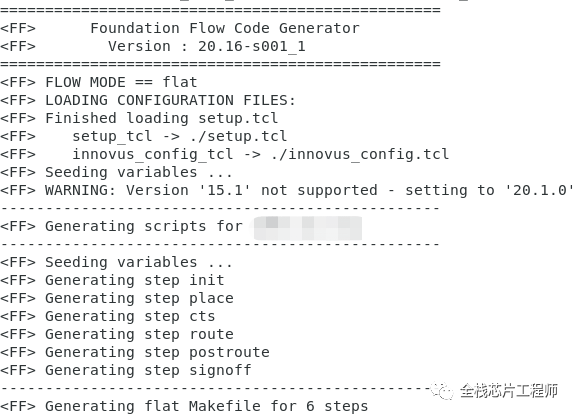

生成腳本命令如下:

tclsh ./SCRIPTS/gen_flow.tcl -m flat all

生成flow腳本之前需要配置setup.tcl等相關參數,具體參見【全網唯一】【全棧芯片工程師】提供自研的景芯SoC前端工程、DFT工程、后端工程,帶你從算法、前端、DFT到后端全流程參與SoC項目設計。

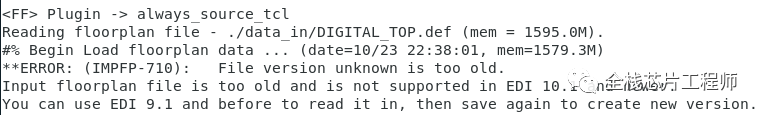

景芯SoC訓練營的同學問,為何innovus讀取做好的floorplandef文件報Error?首先看log:

Reading floorplan file - ./data_in/DIGITAL_TOP.def (mem = 1595.0M).

#% Begin Load floorplan data ... (date=10/23 2201, mem=1579.3M)

**ERROR: (IMPFP-710): File version unknown is too old.

以前EDI的時期,我們可以通過定義fp_file的方式來加載floorplan:

set vars(fp_file) "./data_in/DIGITAL_TOP.def"

但是現在innovus升級并放棄了fp_file的加載方式,當然也可以用老版本的EDI9.1及以前版本來加入fp_file,然后轉存為新版本,這方式明顯沒有必要。正如下log提示所說,檢查log是非常好的工程師習慣。

Input floorplan file is too old and is not supported in EDI 10.1 and newer.

You can use EDI 9.1 and before to read it in, then save again to create new version.

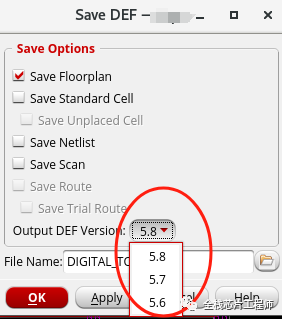

小編的直覺告訴我,先去看看同學保存的def文件是哪個def版本?

同學保存方式如下:

那么請問如何解決?請大家加入景芯訓練營實踐。

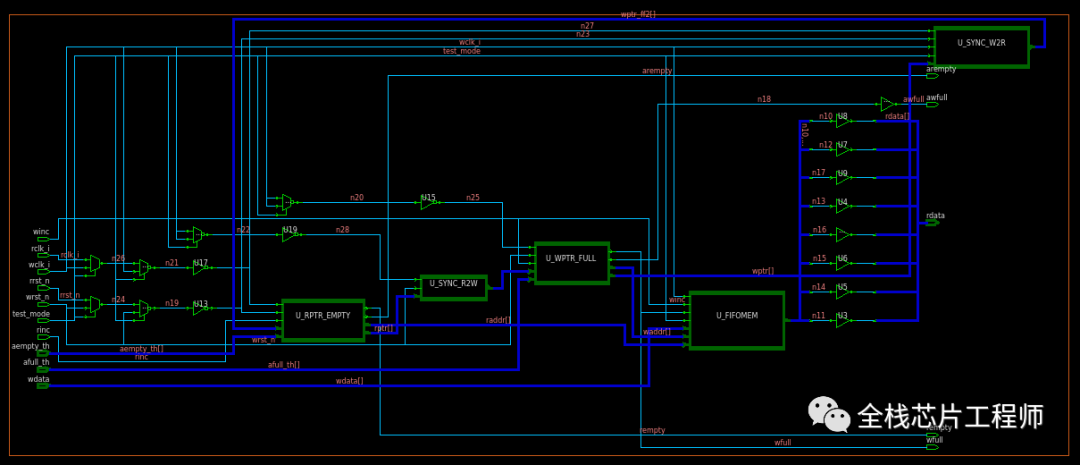

景芯SoC用了很多異步FIFO,關注異步RTL實現的同學,可以抓取異步FIFO出來看一下版圖連線:

查看下所有異步FIFO cell的面積;

dbget [dbget top.insts.pstatus unplaced -p].area

查下所有異步FIFO的cell的名字:

dbget [dbget top.insts.pstatus unplaced -p].name

那么怎么抓出異步路徑來觀察版圖走線呢?如何讓report_timing呢?更多內容參見知識星球和SoC訓練營。

-

mcu

+關注

關注

146文章

17123瀏覽量

350994 -

仿真

+關注

關注

50文章

4070瀏覽量

133552 -

JTAG

+關注

關注

6文章

399瀏覽量

71673 -

端口

+關注

關注

4文章

963瀏覽量

32052

原文標題:JTAG經典問題,ICer不能不懂!

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RCC電路原理與設計及問題解析

模數轉換器的電源去耦問題解析

運算放大器經典問題解析

UART串口與LWIP以太網問題解析

車臺天線的位置和輻射問題解析

康華光《電子技術基礎?數字部分》真題解析

電工學知識要點與習題解析

JTAG經典問題解析

JTAG經典問題解析

評論