對于電子工程師而言,晶體和晶振是電路中不可或缺的關(guān)鍵元件,尤其在涉及到時(shí)鐘信號(hào)和同步操作時(shí)。雖然兩者在功能上有著相似之處,但在實(shí)際應(yīng)用、電路設(shè)計(jì)以及布局布線等方面卻存在著顯著的區(qū)別。本文將詳細(xì)對比晶體和晶振的屬性、特點(diǎn)及應(yīng)用場景,并為大家提供一些實(shí)用的布局和布線建議。

一、晶體與晶振的區(qū)別

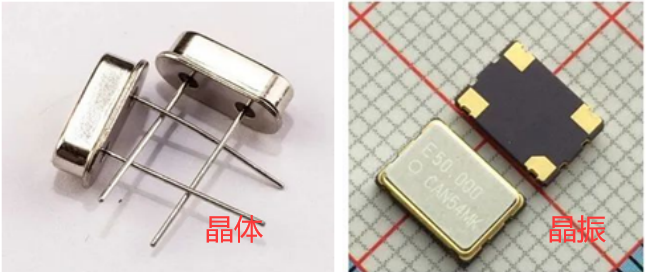

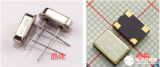

對于許多初入職場的硬件工程師來說,區(qū)分晶體(Crystal,簡稱XTAL)和晶振(Crystal Oscillator,簡稱XO)一直是個(gè)令人頭疼的問題。以下是它們之間的主要差異:

01名稱差異

晶體,通常簡稱為XTAL。

晶振,則被稱為晶體振蕩器,通常簡稱為XO。

電源需求02

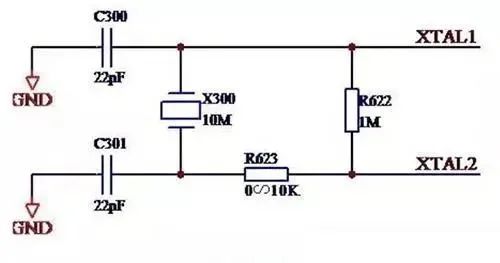

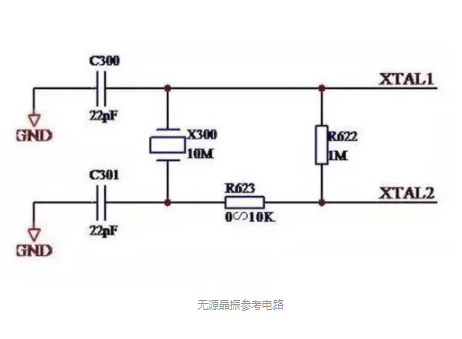

晶體本身無法振蕩,需要依賴外部電路來產(chǎn)生時(shí)鐘信號(hào)。使用晶體的芯片內(nèi)部通常都集成了振蕩電路。

晶振只需通電即可振蕩并輸出時(shí)鐘信號(hào),因?yàn)槠鋬?nèi)部已經(jīng)集成了振蕩電路。有時(shí),晶體被稱作無源晶體,而晶振被稱作有源晶體,這種稱呼方式凸顯了兩者在電源需求上的差異。

03輸出方式

晶體沒有電源引腳,但有輸入和輸出兩個(gè)引腳。

晶振有電源引腳,但只有一個(gè)輸出引腳。

焊接方向04

晶體沒有方向性,可以正向或反向焊接,不影響使用。

晶振有方向,焊反則信號(hào)無法傳至芯片。芯片上的XTAL_IN和XTAL_OUT是為內(nèi)部振蕩電路而標(biāo),與外部晶體無關(guān)。晶體無方向,正向、反向壓電效應(yīng)相同。晶振在芯片上通常只標(biāo)XTAL_IN或XTALCLOCK,只需連對應(yīng)芯片腳即可。

05引腳數(shù)量

兩個(gè)引腳的一定是晶體。晶體只需要一個(gè)薄片狀的水晶片即可振蕩。因此,一個(gè)水晶片的兩個(gè)引腳就是晶體的最少引腳數(shù)。小尺寸的晶體可能會(huì)帶有兩個(gè)地腳,用于將晶體的外殼接地屏蔽。

- 晶振至少有三個(gè)引腳,包括電源、地和時(shí)鐘輸出。如果再加上一個(gè)壓控腳,就是四個(gè)引腳了。

二、晶體與晶振的應(yīng)用場景有何不同?1

晶體在電路中的應(yīng)用

當(dāng)考慮晶體在電路中的應(yīng)用時(shí),其主要作用是提供一個(gè)穩(wěn)定、準(zhǔn)確的時(shí)鐘信號(hào)。這種信號(hào)對于同步和協(xié)調(diào)電子設(shè)備中的各種操作至關(guān)重要。

①、穩(wěn)定的時(shí)鐘源:晶體與芯片內(nèi)部的振蕩電路相結(jié)合,可以為整個(gè)系統(tǒng)提供一個(gè)穩(wěn)定的時(shí)鐘信號(hào)。這是大多數(shù)數(shù)字電路,特別是微處理器和存儲(chǔ)器,所必需的。

②、低成本解決方案:由于晶體本身只需外部連接,不需要復(fù)雜的供電或控制線路,這使得它成為一個(gè)低成本的時(shí)鐘解決方案。

③、緊湊電路設(shè)計(jì):晶體通常很小,適合在緊湊的電路板設(shè)計(jì)中使用。

④、焊接無方向性:晶體沒有特定的焊接方向,這降低了焊接錯(cuò)誤的風(fēng)險(xiǎn)。 2

2

晶振在電路中的應(yīng)用

晶振,與晶體相比,是一個(gè)更為完整的解決方案,因?yàn)樗鼉?nèi)部已經(jīng)包含了必要的振蕩電路。這使得它在某些應(yīng)用中更為方便。

(1)簡化電路設(shè)計(jì):由于晶振內(nèi)部已經(jīng)有了振蕩電路,所以只需要為其提供電源,它就會(huì)輸出一個(gè)時(shí)鐘信號(hào)。這簡化了電路板設(shè)計(jì)。

(2)高精度和高穩(wěn)定性:晶振通常能夠提供比基本的晶體更高的精度和穩(wěn)定性,特別是在寬溫度范圍內(nèi)。

(3)易于控制:對于需要頻率控制的應(yīng)用,如使用壓控振蕩器(VCXO)的場景,晶振可以提供一個(gè)簡單的接口來實(shí)現(xiàn)這一點(diǎn)。

(4)適應(yīng)特定需求:對于需要寬溫度范圍或?qū)纫蟾叩膽?yīng)用,如GPS模塊或高端處理器,溫補(bǔ)晶振(TCXO)可以確保系統(tǒng)在不同環(huán)境下都能正常工作。

三、晶體的布局布線指南

三、晶體的布局布線指南

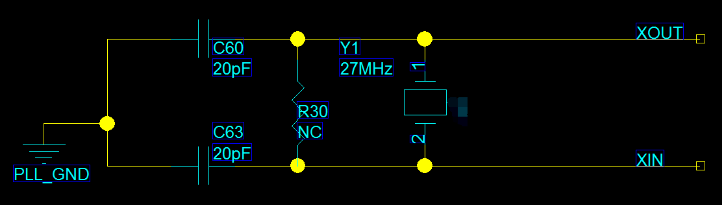

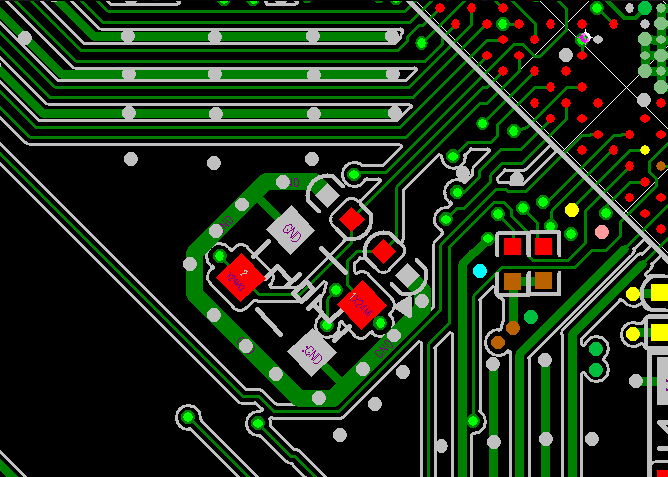

1、晶體布局:

優(yōu)先考慮緊湊布局,將元件優(yōu)先放置在TOP層,盡量靠近IC管腳。

為降低寄生電容,當(dāng)放置兩個(gè)電容時(shí),應(yīng)確保分支長度最小化。

2、晶體布線:

優(yōu)先選擇TOP層進(jìn)行布線。若需過孔,務(wù)必在附近設(shè)置回流過孔。

晶體信號(hào)線應(yīng)走線成類差分形式。

加粗晶體信號(hào)線至8/10mil。

為減小寄生電容,通常將電容的地線扇出線寬加粗至18-22mil。

對時(shí)鐘信號(hào)線實(shí)施包地處理,確保其穩(wěn)定性。

在晶體附近設(shè)置屏蔽地過孔,以吸收和減少輻射噪聲。

- 晶體下方禁止其他信號(hào)穿越,確保無干擾。

四、晶振的布局布線指南

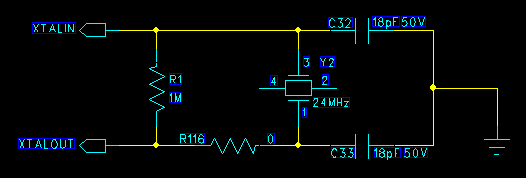

1、晶振布局:

保持緊湊布局,優(yōu)先考慮在TOP層進(jìn)行布局。

將匹配電阻緊鄰晶振放置,以減小電阻與晶振之間的信號(hào)延遲。

對于晶振電源,采用π型濾波以提高電源質(zhì)量。在空間允許的情況下,濾波電容應(yīng)優(yōu)先放置在TOP層,并按照先大后小的順序放置,以確保良好的濾波效果。

2、晶振布線:

為避免干擾,晶振本體下方禁止走線。在布線密度較大的情況下,至少確保晶振本體經(jīng)過兩個(gè)平面層的屏蔽后方可走線,以維護(hù)信號(hào)完整性。

晶振輸出信號(hào)應(yīng)按照嚴(yán)格的50歐姆阻抗進(jìn)行走線。在換層處,務(wù)必打過回流地過孔,并與其他信號(hào)保持至少4W以上的間距,以減小串?dāng)_和電磁干擾。

- 在晶體附近設(shè)置屏蔽地過孔,以吸收和降低輻射噪聲,提高電路的穩(wěn)定性。

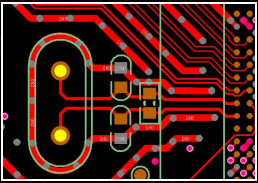

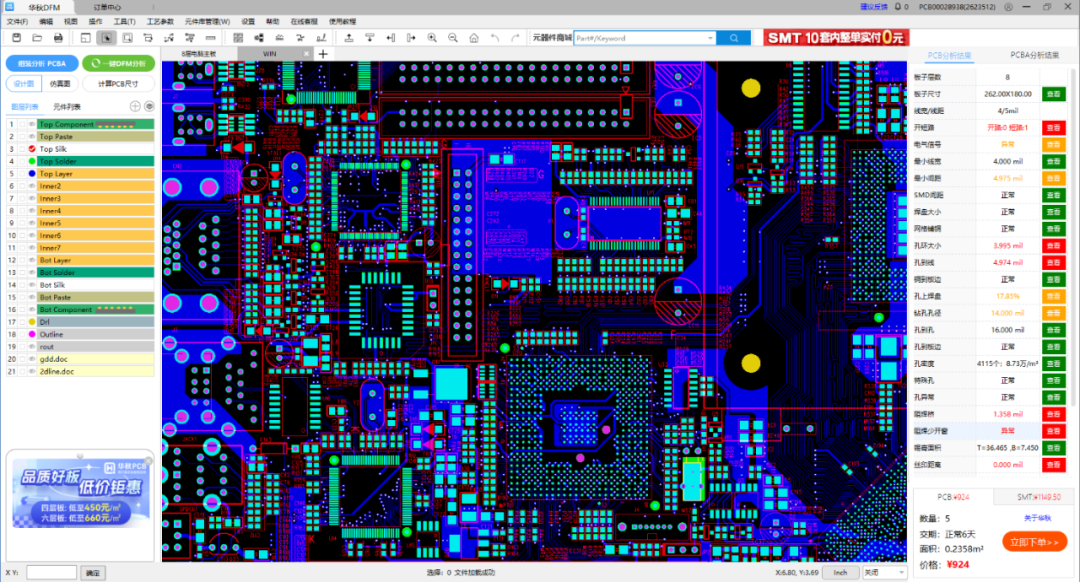

五、晶體晶振的PCB可制造性檢查

在PCB布局和布線設(shè)計(jì)完成后,為確保順利制造并避免潛在的可制造性問題,進(jìn)行可制造性檢查是至關(guān)重要的一步。特別是對于晶體和晶振的PCB設(shè)計(jì),應(yīng)對線寬、線距、孔距和孔徑大小進(jìn)行仔細(xì)檢查。此外,還要核實(shí)孔環(huán)是否足夠,以確保穩(wěn)定的電氣連接。

我們可以使用華秋DFM軟件對晶體和晶振的PCB設(shè)計(jì)進(jìn)行詳細(xì)檢查,包括最小線寬、線距,焊盤的大小以及是否漏引腳孔等多項(xiàng)工藝問題,還可以提前預(yù)防是否存在可制造性問題等。

結(jié)語:

希望通過本文的闡述,讀者們能夠?qū)w和晶振有更清晰的認(rèn)識(shí),理解它們在電路中的重要作用,以及在設(shè)計(jì)和應(yīng)用時(shí)需要注意的關(guān)鍵點(diǎn)。對于工程師來說,選擇合適的元件并進(jìn)行合理的布局和布線,是確保電路性能穩(wěn)定、可靠的關(guān)鍵步驟。希望大家在實(shí)踐中學(xué)以致用,不斷積累經(jīng)驗(yàn),為電子行業(yè)的發(fā)展貢獻(xiàn)自己的力量。

-

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6673文章

2451瀏覽量

204167 -

晶體

+關(guān)注

關(guān)注

2文章

1351瀏覽量

35418 -

晶振

+關(guān)注

關(guān)注

34文章

2859瀏覽量

68005

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

1.8432MHZ晶振和18.432M晶振,小數(shù)點(diǎn)千萬別調(diào)皮哦

工業(yè)互聯(lián)網(wǎng)和工業(yè)4.0傻傻分不清楚?

不要再對各種電機(jī)、舵機(jī)傻傻分不清楚了 精選資料分享

科普:石墨烯電池、石墨烯基電池二者有何不同?別傻傻分不清

如何區(qū)分晶體與晶振,晶體和晶振的真正定義

曾經(jīng)分不清的RAM知識(shí) 你現(xiàn)在搞明白了嗎?

如何區(qū)分有源晶振與無源晶振?區(qū)別是什么?

傻傻分不清?射頻模擬信號(hào)源和矢量信號(hào)源的區(qū)別

晶體與晶振傻傻分不清?看完這篇文章您就明白了

晶體與晶振傻傻分不清?看完這篇文章您就明白了

晶體與晶振傻傻分不清?看完這篇文章您就明白了

評(píng)論