節(jié)點尺寸大致代表了芯片的工藝迭代和先進程度,但是幾納米到底是指什么尺寸?本文帶大家一探究竟,了解芯片節(jié)點命名的多次更改。

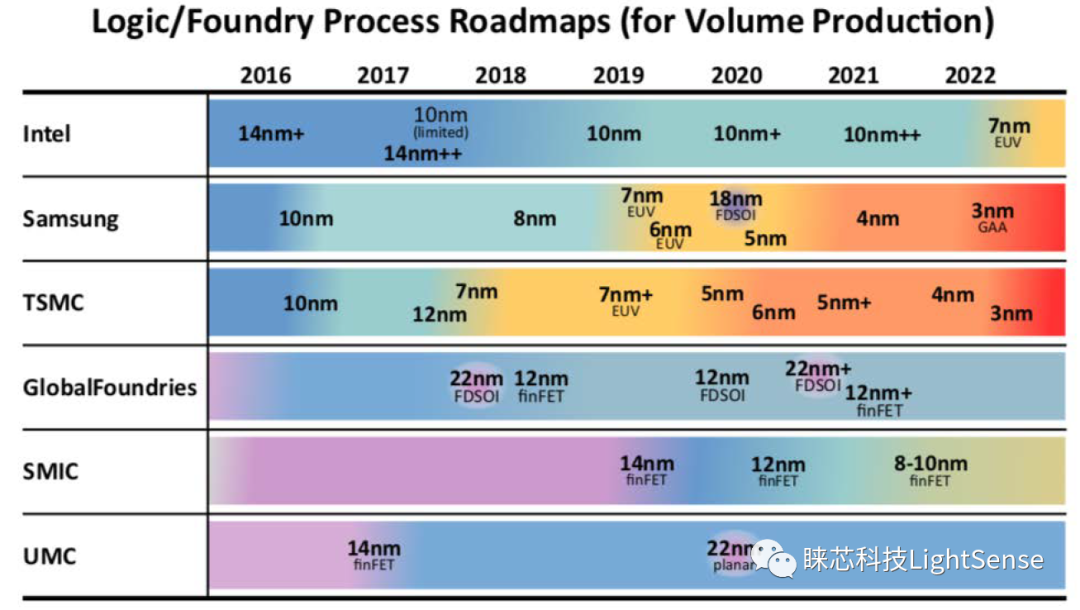

Sources: Companies, conference reports and IC Insights

目前所謂的nm數(shù),只是大致表示工藝的迭代和先進程度,但不是晶體管的尺寸真是“幾納米”。那么,幾納米,到底是什么尺寸呢?

從1992年到現(xiàn)在,命名技術節(jié)點的方法遵循NTRS、ITRS和IRDS的定義。技術節(jié)點的名稱通常與最近金屬層的最小節(jié)距的一半相關。

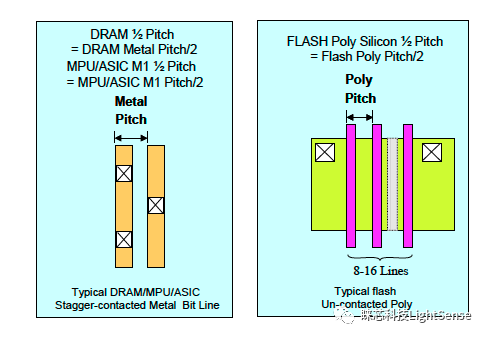

1. 節(jié)點的原始定義:最近金屬層的半節(jié)距

在20世紀70年代、80年代和90年代的大部分時間里,最近的金屬線半節(jié)距和柵極長度半節(jié)距的尺寸基本上相同,選擇該值作為節(jié)點名稱是因為它用單個數(shù)字傳達了密度的概念和性能的概念。下圖展示了節(jié)點的原始定義:最小金屬層的半節(jié)距。

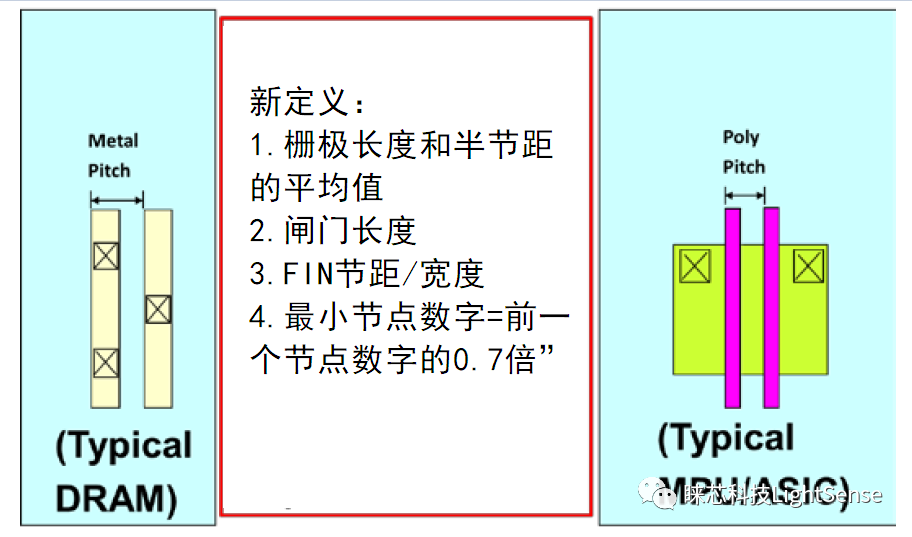

2. 節(jié)點的第二次定義:變成了上一代節(jié)點數(shù)字的70%

在90年代后半葉,消費者對PC的采用對任何新產品的推出都提出了更高的期望,即更高的晶體管密度和更高的性能。因此,在90年代,微處理器技術的引入從以前的3-4年周期加速到了2年周期,以滿足消費者的需求。隨著軟件程序變得更大、更復雜,因此需要更高的執(zhí)行速度,有必要更系統(tǒng)、更積極地將晶體管的溝道長度減少到前一代的60%,以便產生在更高頻率下工作的更快晶體管。

在這段競爭激烈的時間里,少數(shù)公司開始將金屬半節(jié)距尺寸與柵極長度尺寸進行平均,作為與其最新技術相關的節(jié)點名稱。由于這種平均過程(即70%的半金屬節(jié)距減少和60%的柵極長度減少導致約的65%尺寸減少)。這些最新技術在紙面上看起來更小,更加吸引客戶。后來,一些公司決定只使用柵極一個維度來定義技術節(jié)點的名稱。350nm以后,技術節(jié)點的定義變成了上一代節(jié)點名稱的70%。

此時,節(jié)點數(shù)字已經不代表實際尺寸了。

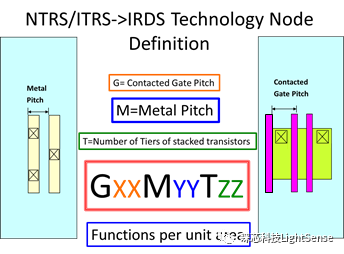

3. 節(jié)點的第三次定義:14nm之后,節(jié)點數(shù)字更是成謎了

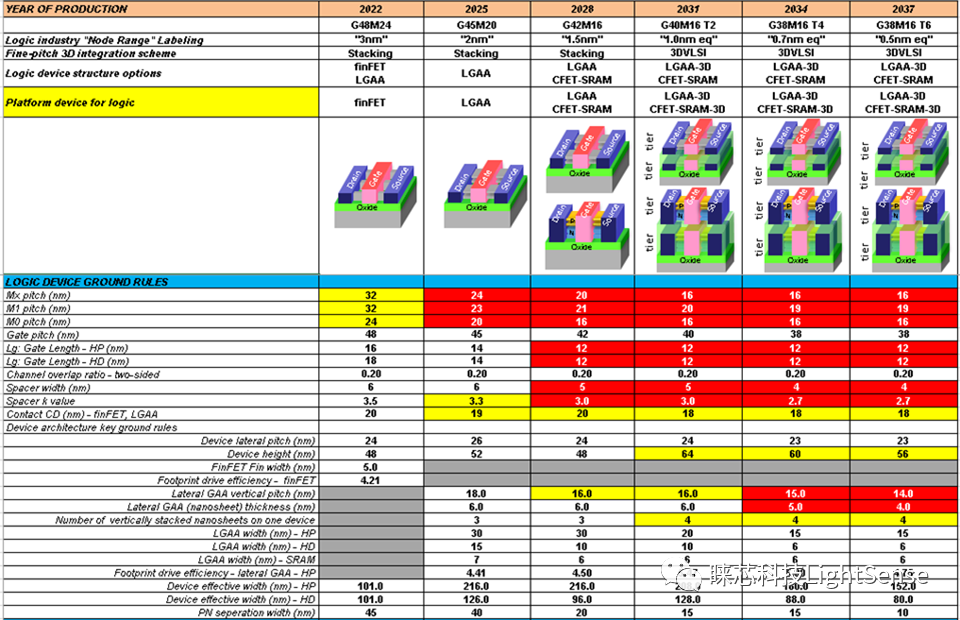

以上一代節(jié)點數(shù)字的70%來定義節(jié)點導致了IC功能和技術節(jié)點名稱之間的完全分離。因此,回到基礎并重新激活節(jié)點定義以更緊密地表示現(xiàn)實是有益的。IRDS采用了更廣泛的節(jié)點定義,但仍與NTRS和ITRS的歷史定義有關。下圖所示,用GxxMyyTzz,G表示接觸層柵極間距,M表示金屬間距,T表示堆疊晶體層的層數(shù)。

所以,從上圖看出來,3nm節(jié)點,大致相當于接觸柵極間距48nm,柵極長度16nm或18nm,第0層金屬間距24nm,堆疊晶體層的層數(shù)為1層。

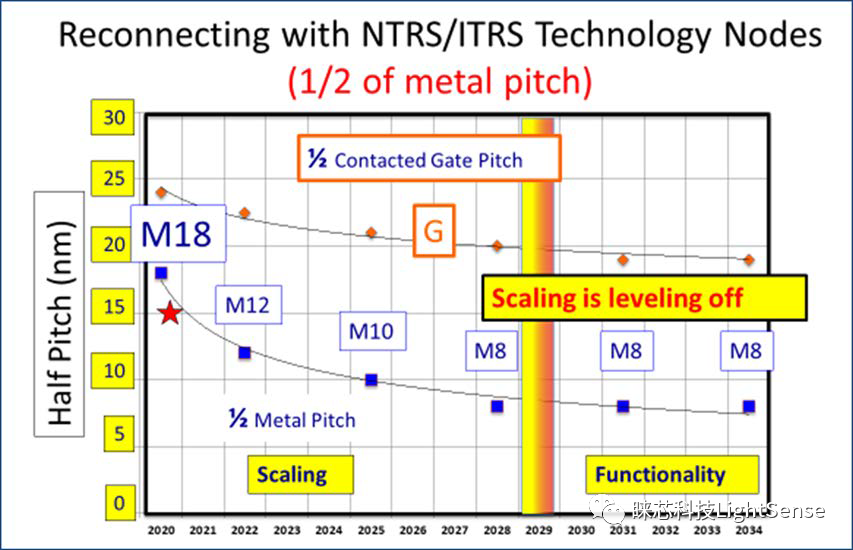

預計在本十年結束時,特征縮放將達到約7-8nm的基本極限,如下圖:

審核編輯:黃飛

-

芯片

+關注

關注

456文章

50892瀏覽量

424328 -

晶體管

+關注

關注

77文章

9701瀏覽量

138374

發(fā)布評論請先 登錄

相關推薦

波形圖控件,如何通過屬性節(jié)點給曲線命名

英特爾半導體制程的節(jié)點命名

什么是新型納米吸波涂層材料?

一個更改尺寸類型的LISP程序

2019年起高通新款7納米移動裝置系統(tǒng)單芯片(SoC)將不再以800系列命名

納米材料是指什么材料_納米材料的特性

蘋果15芯片是多少納米?蘋果15芯片幾納米的?

蘋果15芯片幾納米工藝 蘋果15芯片是什么型號

為什么45納米至130納米的工藝節(jié)點如此重要呢?

幾納米指什么尺寸?了解芯片節(jié)點命名的多次更改

幾納米指什么尺寸?了解芯片節(jié)點命名的多次更改

評論