一RZ/T、RZ/N系列MPU

芯片啟動注意事項

RZ/T、RZ/N系列MPU有3路電源域,在啟動時,外圍設備也需要進行不同電源域的配置,所以電源時序,復位信號,以及系統管腳的配置都會影響芯片的啟動流程,如果不能正確配置,芯片則有可能啟動不正常,以下為芯片啟動時需要注意的配置介紹。

二啟動系統介紹

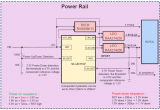

1電源

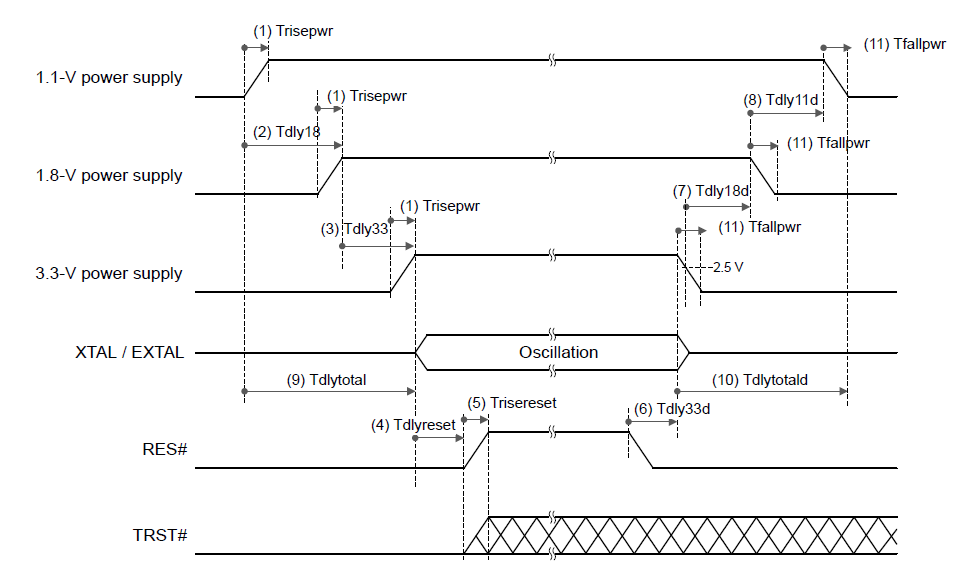

上下電時序要求:

芯片對于上下電有明確的時序要求,具體要求詳見user manual(用戶手冊)>>Electrical Characteristics章節。

由于上電時序十分重要,大部分啟動不了的問題都是上電時序不滿足導致,所以瑞薩有匹配的電源時序控制方案可直接使用:

① PMIC(DAS9061/DA9080)

② GPARK(SLG46582)

2復位電路

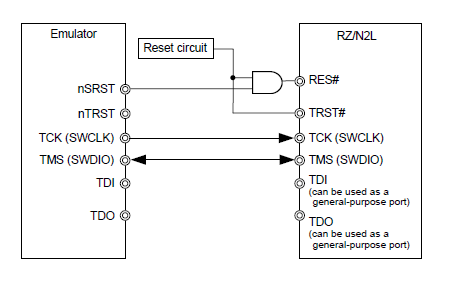

RZT/RZN芯片有2個復位信號:

RES復位除了仿真電路以外的LSI外設,所以仿真器的復位需要連到此信號。

TRST復位TAP(Test Access Port),仿真器復位管腳不能連到此處,否則上電復位時,會直接復位TAP電路,導致不能仿真,此管腳有2種推薦接法:

a.和RES接相同的信號,使用仿真器時,參考接法如下:

b. 不用此管腳時,可通過一個下拉電阻接地,或和RES接相同的信號,注意不能懸空。

仿真器端有2個復位信號:

nSRST系統復位,一定要接,可通過調試器復位系統,方便調試。

nTRSTTAP復位,可不接。

3時鐘

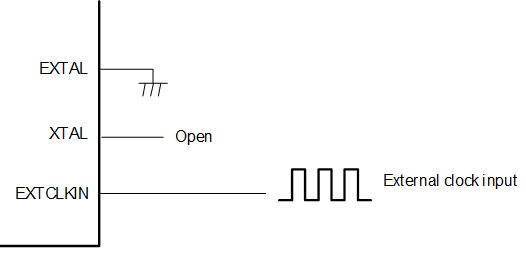

有源晶振

尤其是使用ECAT網絡時,推薦使用有源晶振,接到EXTCLKIN,精度要求25ppm以內,EXTAL連接到VSS,XTAL保持開。

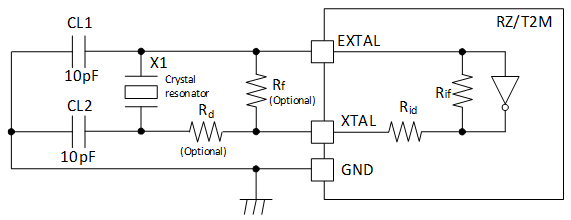

無源晶振

晶振和電容盡可能靠近EXTAL和XTAL引腳,晶體的PCB周圍最好用GND包起來,用于屏蔽的GND走線寬度應不小于0.3 mm,與相鄰走線之間應保持0.3 mm ~ 2.0 mm的距離。

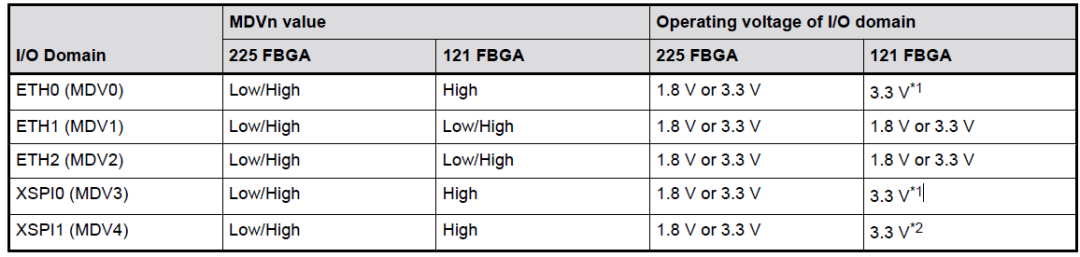

4MDV電源域配置管腳

點擊可查看大圖

RZT/RZN有不同的電源域配置,根據MDV0~MDV4管腳進行配置:

MDV0~MDV2

對應ETH0~ETH2,根據實際的PHY芯片選擇對應的1.8V還是3.3V

MDV3~MDV4

對應XSPI0,XSPI1,根據外部配置的存儲芯片類型確定。

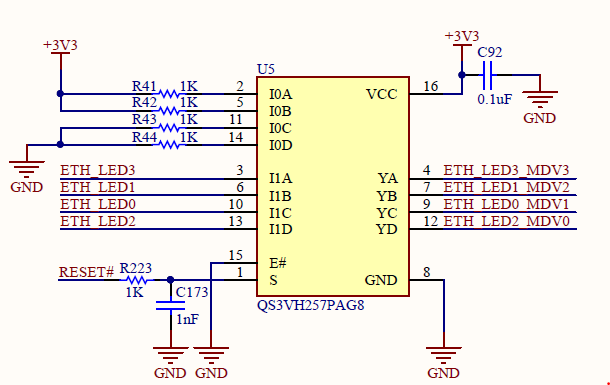

以上管腳只在復位釋放時檢測,程序正常啟動后可以復用為其他功能,以下為參考設計方法,使用一個選通芯片進行選擇,復位拉低時,選通固定的高低電平配置,復位拉高后,使用為EtherNET LED功能。

5其他需要特殊處理的系統管腳

MDD (JTAG authentication by hash signal)下拉(正常模式)。

BSCANP (Boundary scan setting)下拉(關閉邊界掃描設置)。

MDX系統管腳,固定接下拉。

MDW (ATCM wait cycle select signal)此管腳配置ATCM的訪問延時,如果CPU時鐘低于或等于400MHz時,為0等待(MDW =0),高于400MHz時,為1個等待(MDW = 1),所以此管腳只在RZT系列才有,RZN系列最高跑在400MHz,不需要此管腳。

NMI (不可屏蔽中斷) 上升沿或下降沿都會觸發此中斷,所以常規接法是將此管腳上拉。

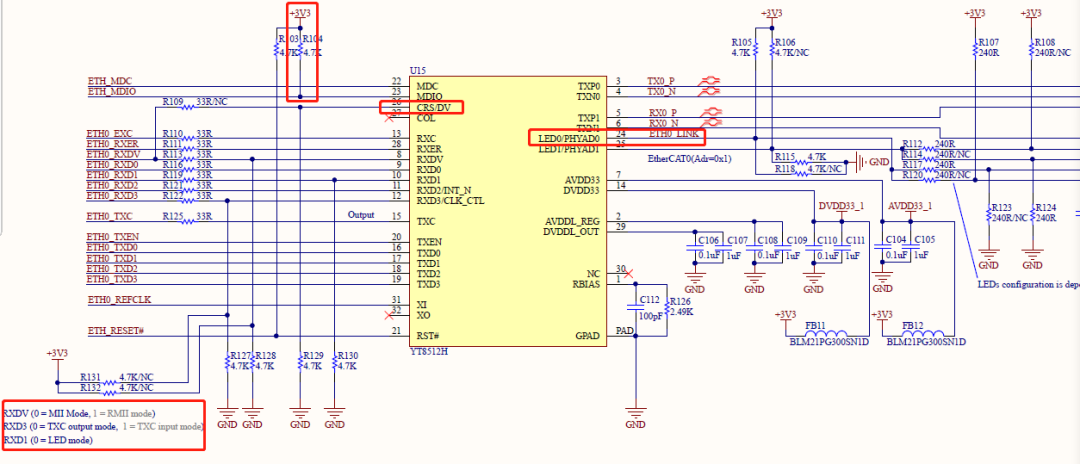

6網絡周邊 (適配YT8512為例)

ECAT推薦使用MII接口,小地址IN,大地址OUT,地址需要連續,地址0一般不用。

YT8512芯片LED1/PHYAD[1]/ETHn_LINK,3個信號在同一個管腳復用,所以需要做以下操作:

① LED的狀態需要保持在穩定狀態,即不能做成閃爍狀態。(PHY寄存器改成0x30,收發包時,LED亮,down時,LED滅)

LEDO對應的寄存器為ext Reg0x40C0;(上電默認值為0x0311)

LED1對應的寄存器為ext Reg0x40C2;(上電默認值為0x0320)

向這兩個寄存器賦不同值,則LED做相應的狀態顯示,典型幾種配置如下:

ext Reg0x40C0/0x40C3 配置值

動作行為

0x0311

link在10M時,LED亮;link在10M且收發包,LED閃

0x0320

link在100M時,LED亮;link在100M且收發包,LED閃

0x30

link或收發包時,LED亮;link down時滅

0x1300

收發包時閃爍;不收發包即滅

② YT8512的LED1內部有自動檢測外部上下拉狀態的判斷LED1有效的功能,需要根據PHY芯片LED1的上下拉狀態,來對應配置MPU的link檢測狀態的極性PHYLNK.CATLNK,否則ECAT網絡會反復Link-up,Link-down,以下是YT8512外圍的參考設:

1. 硬件設計

●參考25Mhz時鐘可以使用外部時鐘源,或從芯片直接提供給PHY

●檢查MDIO是否需要一個外部上拉電阻,CRS接地

●考慮在信號源附近增加串聯終端電阻以減少信號線上的反射

2.PCB走線注意

●RMII/MII的阻抗為50歐姆±10%,大多數布線的正常標準

●所有MII/RMII信號線(數據線、時鐘線和其他)應在單層上布線,并具有精確的長度匹

數據線和時鐘線的跡長偏差應在10mm以內,應避免通孔

● MII/RMII信號的路徑應該盡可能的直,且越短越好。否則,軌跡彎曲不應超過45度

●時鐘信號走線硬盡可能短,特殊情況需要等長布線時,要可被地線屏蔽

●在信號層下面或上面放置一個地面層,以便MII/RMII信號的返回電流隨時返回

審核編輯:湯梓紅

-

電源

+關注

關注

184文章

17704瀏覽量

249959 -

處理器

+關注

關注

68文章

19259瀏覽量

229651 -

MPU

+關注

關注

0文章

357瀏覽量

48775 -

復位信號

+關注

關注

0文章

54瀏覽量

6314

原文標題:RZ/T2M N2L T2L原理圖設計要點

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RZ/T2M 組 RZ/T2M 電機解決方案套件啟動手冊(用于 EtherCAT)

RZ/T2M 組 RZ/T2M 電機解決方案套件啟動手冊(用于 EtherCAT)

RZ/G1H、RZ/G1M、RZ/G1N和 RZ/G1E Linux啟動指南

工業MPU新標桿,多協議工業以太網+運動控制 - 瑞薩RZ/T2H 新產品

RZ/T、RZ/N系列MPU芯片啟動注意事項

RZ/T、RZ/N系列MPU芯片啟動注意事項

評論