導言

在很久之前便陸續談過亞穩態,FIFO,復位的設計。本次亦安做一個簡單的總結,從宏觀上給大家展示跨時鐘域的解決方案。

什么是亞穩態?

對大多數工程師來講,亞穩態是非常難以追蹤的,因為它具有不確定性,在相對規范的設計下,如果仍然發生這個問題,那么可能非常難以復現異常。簡單來講,當觸發器不滿足建立時間和保持時間要求時,就會導致亞穩態。亞穩態出現時,觸發器既不是高邏輯也不是低邏輯,后續電路則可能讀取為0或者1(不確定狀態),導致電路邏輯做出不符合當前事物邏輯的事情。

對于數字設計人員來講,只要信號從一個時鐘域跨越到另一個時鐘域,那么就可能發生亞穩態。我們稱為“跨時鐘域”即“Clock Domain Crossing”,或CDC。

所以今天主要簡單了解如何處理CDC這些基礎問題。

同步跨時鐘域信號

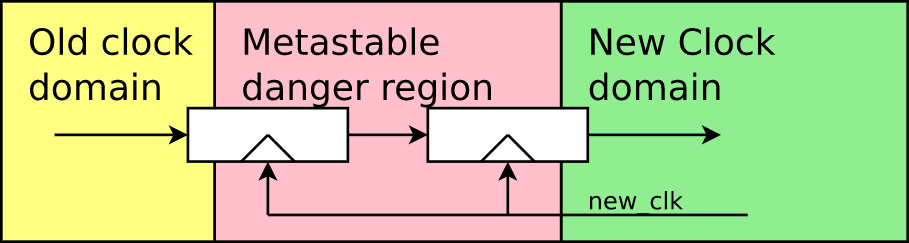

對大多數初學者來講,當我們遇到CDCs時,有經驗的工程師會告訴我們“打兩拍”,即讓信號通過兩個 flip-flops,每個flip-flop都由新時鐘域的時鐘驅動(如下圖)。第一個觸發器出現亞穩態的概率很高,但第二個觸發器的輸出亞穩態的概率就會低得多。當然更多的flip-flops會讓亞穩態的概率進一步下降,但一般下降的概率差距不會太大,如何選擇取決于設計者自己。但并非多數CDC問題都能用這種簡單方法,這種設計適用于舊時鐘域比新時鐘域慢的多的情況。經典的可配置的代碼如下。

//Language:Verilog-2001 `resetall `timescale1ns/1ps `default_nettypenone /* *Synchronizesanasyncronoussignaltoagivenclockbyusingapipelineof *tworegisters. */ modulesync_signal#( parameterWIDTH=1,//widthoftheinputandoutputsignals parameterN=2//depthofsynchronizer )( inputwireclk, inputwire[WIDTH-1:0]in, outputwire[WIDTH-1:0]out ); reg[WIDTH-1:0]sync_reg[N-1:0]; /* *Thesynchronizedoutputisthelastregisterinthepipeline. */ assignout=sync_reg[N-1]; integerk; always@(posedgeclk)begin sync_reg[0]<=?in; ????for?(k?=?1;?k?

異步復位同步釋放

CDC中一個常見的例子就是異步復位,這個問題我在“FPGA復位信號設計討論“一文中有詳細的表述,這里簡單講解,對于初學者而言,不太建議用異步復位,盡管他們各有優劣,但至少對FPGA設計者而言,這個建議應該是有效的,即使是Xilinx官方也同樣建議使用同步復位(UG949)。

但有些狀態下可能同步復位無效,比如在低功耗設計中,時鐘可能在復位前就已經被“無效”,那么異步復位自然成為一個選擇。異步復位關鍵點不在進入復位狀態,而在于移除復位,因為移除狀態可能會進入亞穩態,除了“FPGA復位信號設計討論”一文,大家同樣可以參閱我翻譯的經典論文“同步復位與異步復位”。經典的代碼如下所示,但請注意區別此處代碼和“打兩拍“的區別。

//Language:Verilog-2001 `resetall `timescale1ns/1ps `default_nettypenone /* *Synchronizesanactive-highasynchronousresetsignaltoagivenclockby *usingapipelineofNregisters. */ modulesync_reset# ( //depthofsynchronizer parameterN=2 ) ( inputwireclk, inputwirerst, outputwireout ); (*srl_style="register"*) reg[N-1:0]sync_reg={N{1'b1}}; assignout=sync_reg[N-1]; always@(posedgeclkorposedgerst)begin if(rst)begin sync_reg<=?{N{1'b1}}; ????end?else?begin ????????sync_reg?<=?{sync_reg[N-2:0],?1'b0}; ????end end endmodule `resetall

很多人爭論高電平復位有效好還是低電平復位有效好,一般情況下我常見低電平復位有效,但高電平復位有效也不是沒有,一般認為在FPGA中區別不是太大,但在ASIC中,低電平似乎更加常見。

跨時鐘握手

有時需要一種方法來處理CDC,例如從慢時鐘到快時鐘,從快時鐘到慢時鐘,這時需要:握手信號,在“AXI4協議邏輯規范以及BUG處理”一文寫過握手的注意點。握手的詳細技術點感興趣的朋友可以網上找相關資料。

FIFO

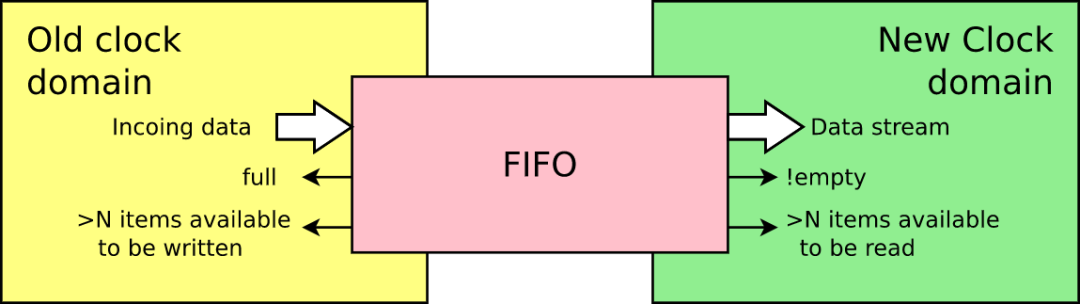

FIFO網上的文章特別多,具體的設計細節有很多需要討論的地方,但對于跨時鐘域而言,FIFO幾乎是最方便的數據傳輸方式。這里不展開講,之前我寫過關于FIFO的相關文章,不是特別詳細,接下來會有詳細的關于FIFO的計劃,在此之前,大家可以看Clifford E. Cummings經典論文,他的論文真的很推薦。

http://www.sunburst-design.com/papers/CummingsSNUG2008Boston_CDC.pdf

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26509 -

fifo

+關注

關注

3文章

387瀏覽量

43648 -

CDC

+關注

關注

0文章

57瀏覽量

17798 -

觸發器

+關注

關注

14文章

2000瀏覽量

61132 -

時鐘域

+關注

關注

0文章

52瀏覽量

9535

原文標題:跨時鐘域的幾種基本處理方法

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

跨時鐘域的解決方案

跨時鐘域的解決方案

評論