PCB 設(shè)計(jì)規(guī)范

一、引言

1. 目的

本規(guī)范規(guī)定了我公司 PCB 設(shè)計(jì)流程和設(shè)計(jì)原則,為 PCB 設(shè)計(jì)人員提供必須遵循的規(guī)則和約定。

提高 PCB 的設(shè)計(jì)質(zhì)量和設(shè)計(jì)效率。

提高 PCB 的可生產(chǎn)性,可測試性,可維護(hù)性。

使得 PCB 的設(shè)計(jì)滿足安規(guī)、EMC、EMI 等技術(shù)規(guī)范要求。

2. 術(shù)語定義

● PCB:印制電路板

● 原理圖:用原理圖設(shè)計(jì)工具繪制成的表達(dá)硬件電路中各種之間的連接關(guān)系圖。

● 網(wǎng)表:由原理圖設(shè)計(jì)工具生成的表達(dá)元器件間電氣連接關(guān)系的文本文件。

● 布局:PCB 設(shè)計(jì)過程中按照設(shè)計(jì)要求把元器件擺放在板上的過程。

● 仿真:利用 EDA 設(shè)計(jì)工具對 PCB 布局布線效果進(jìn)行仿真分析從而在物理實(shí)現(xiàn)

之前發(fā)現(xiàn)設(shè)計(jì)中存在的 EMC 問題、時序問題和信號完整性問題。

3. 適用范圍

本規(guī)范適用于所有產(chǎn)品的 PCB 工藝設(shè)計(jì),運(yùn)用于但不限于 PCB 的設(shè)計(jì)、PCB 投板工藝審查等活動。

4. 概述

電路原理圖設(shè)計(jì)完畢,就要進(jìn)行 PCB 設(shè)計(jì)。PCB 設(shè)計(jì)是一項(xiàng)專業(yè)性很強(qiáng)的工作,而且對產(chǎn)品開發(fā)周期起著舉足輕重的作用。PCB 設(shè)計(jì)質(zhì)量除了直接同設(shè)計(jì)人員素質(zhì)有關(guān)以外,還同原理圖設(shè)計(jì)的正確性、提交原理圖者的準(zhǔn)備情況有關(guān)。

PCB 設(shè)計(jì)必須考慮生產(chǎn)工藝流程及維護(hù)測試需要,例如選用表貼器件還是插件、單面還是雙面放置器件、機(jī)械安裝孔及表貼加工定位孔、測試點(diǎn)、元器件擺放方向、散熱器及固定件的位置,特殊接插件的位置等等,這些常常為經(jīng)驗(yàn)不足的硬件開發(fā)人員所忽略,導(dǎo)致設(shè)計(jì)出的板只能是廢板。硬件工程師對此要引起足夠的重視。

本規(guī)范不討論其中的原理,只是給出相應(yīng)要求,以便于 PCB 評審時有依據(jù)。

二、 設(shè)計(jì)過程

設(shè)計(jì)任務(wù)受理

2.1 PCB 設(shè)計(jì)申請流程

當(dāng)硬件設(shè)計(jì)人員需要進(jìn)行 PCB 設(shè)計(jì)時提出申請,由項(xiàng)目經(jīng)理下達(dá)任務(wù)。進(jìn)行設(shè)之前必須做好如下材料的準(zhǔn)備。

● 經(jīng)過評審的完全正確的原理圖,包括紙面文件和電子文件。

● 帶有元器件編碼的 BOM 清單

● PCB 結(jié)構(gòu)圖,注明外型尺寸、安裝孔位置及大小、接插件定位尺寸、禁止布線區(qū)(可選)

● 對于新器件要提供器件封裝資料

● PCB 布線規(guī)則約束文檔

● 相關(guān)源文件已經(jīng)上傳到 SVN

2.2 理解設(shè)計(jì)要求并制定設(shè)計(jì)規(guī)劃

●仔細(xì)閱讀原理圖,理解電路工作條件(比如,模擬電路的工作頻率,數(shù)字電路的速度),理解相關(guān)的布線要求

●在于原理圖設(shè)計(jì)者充分交流的基礎(chǔ)上,并閱讀相應(yīng)的布線規(guī)則文檔,理解和確認(rèn)板上的關(guān)鍵網(wǎng)絡(luò),比如電源、時鐘、高速信號等

●如果發(fā)現(xiàn)原理圖中有不符合硬件設(shè)計(jì)規(guī)范的地方,理解提出,并協(xié)助修改。●制定 PCB 設(shè)計(jì)計(jì)劃及進(jìn)度,包括

▲ 原理圖網(wǎng)表導(dǎo)入成功

▲ 布局完成

▲ 布線完成

▲ 信號完整性和 EMC 分析

▲ GERBER 文檔的生成

● 制定出每一步完成的具體時間,每一步完成后均要由原理圖設(shè)計(jì)者及相關(guān)設(shè)計(jì)人員進(jìn)行評審,評審?fù)ㄟ^后方可進(jìn)行下一步。

2.3 創(chuàng)建 PCB 板

1) 根據(jù)單板結(jié)構(gòu)圖或?qū)?yīng)的標(biāo)準(zhǔn)板框,創(chuàng)建 PCB 設(shè)計(jì)文件,包括安裝孔、禁布區(qū),

SMT 光學(xué)定位孔等,

2) 正確選定單板坐標(biāo)原點(diǎn)的位置,原點(diǎn)的設(shè)置原則如下:

| ●單板左邊和下邊的交叉點(diǎn)或延長線的交叉點(diǎn)。● 單板左角的第一個焊盤 | (優(yōu)先) |

3) 一旦原點(diǎn)確定,元件布局布線均以此為準(zhǔn),布局推薦設(shè)置格點(diǎn)為 25MIL。

4) 板框的線寬應(yīng)該為 8MIL。安裝孔在沒有特殊要求的情況下,孔內(nèi)徑為 130,外徑

為 260。

5) 板框四周倒圓角,倒角半徑為 100MIL。特殊情況參考機(jī)械設(shè)計(jì)要求。

6) 板子大于 400X200MM 的 BGA 板子,需要 BGA 附近的對角上面放置機(jī)械固定孔。

2.4 布局

1) 元件布局區(qū)域需離板邊至少 3MM,推薦使用 5MM

2) 在安裝孔周圍,布局和布線均需距離 3MM

3) 需先放置與結(jié)構(gòu)有關(guān)的元件,如對外的接口,電源接口,板與板之間的接口等。

4) 優(yōu)先放置核心電路元件或體積較大的元件,再以該元件為中心,放置外圍電路。

5) 高功率的器件,應(yīng)盡量放在利于散熱的位置,如通風(fēng)口附件。

6) 質(zhì)量比較大的元器件,應(yīng)盡量不放在線路板的中間。

7) 元器件盡量布在正面,盡量在反面只有一種元器件(去藕電容),若無特殊情況,

反面盡量不布芯片。

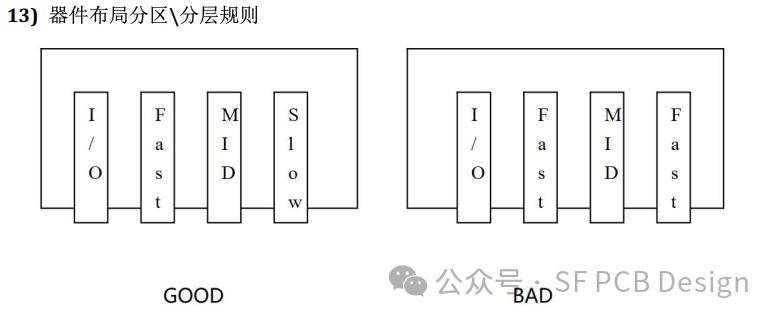

8) 布局應(yīng)盡量滿足以下要求:總的連線盡可能短,關(guān)鍵信號線最短;高電壓、大電流信號

與小電流,低電壓的弱信號完全分開;模擬信號與數(shù)字信號分開;高頻信號與低頻信號

分開;高頻元器件的間隔要充分。

9) 在布局時,應(yīng)考慮同一電源的器件盡量放在一起,雙方便電源分割。

10) 考慮信號流向,合理布局,盡量使信號流向一致。

11) 輸入、輸出應(yīng)盡量遠(yuǎn)離。

12) 帶高壓的元器件應(yīng)放在手不易觸及的地方。

13) 可調(diào)元件應(yīng)放于方便調(diào)節(jié)的地方。

14) 布局應(yīng)均勻、整齊、緊湊。

15) 表面貼元件焊盤排列方向應(yīng)盡量一致,以方便焊接。

16) 表面貼元件和高的元器件應(yīng)留有一個的焊接空間,建議大于 10MM,以方便焊接。

17) 去藕電容應(yīng)盡量放置在電源輸入端。

18) 用于阻抗匹配的阻容器件,應(yīng)根據(jù)其屬性合理布局。串聯(lián)匹配電阻的布局要靠近信

號的驅(qū)動端,距離一般不超過 500mil。匹配電阻、電容的布局一定要分清信號端,對

于多負(fù)載的終端匹配一定要在信號的最遠(yuǎn)端匹配。在同一電路,在各個產(chǎn)品里,盡量保持布局一致。

2.5 疊層設(shè)計(jì)

2.5.1. 在 CPB 的 EMC 和 SI 設(shè)計(jì)

在 CPB 的 EMC 和 SI 設(shè)計(jì)考慮中,首先涉及的便是層的設(shè)置;PCB 板的層數(shù)由電源、地的層數(shù)和信號層數(shù)組成;電源層、地層、信號層的相對位置以及電源、地平面的分割對單板的 MEC 和 SI 的指標(biāo)至關(guān)重要。

1) 合理的層數(shù)

根據(jù)電源、地的種類,信號密度,工作頻率,有特殊布線要求的信號數(shù)量,以及綜合單板的性能指標(biāo)要求與成本承受能力來綜合評定,根據(jù)評定結(jié)果最終確定單板的層數(shù);對于 MEC 和 SI 指標(biāo)要求苛刻而相對成本能承受的情況下,適當(dāng)增加地平面乃是 PCB 的 EMC 設(shè)計(jì)的殺手锏之一。

a) 電源、地的層數(shù)

電源的層數(shù)由其種類數(shù)量準(zhǔn)定;單一電源供電,一個電源平面足夠了;多種電源,若相互不交錯,可以采用電源層割;若多種電源相互交錯,則需考慮 2 個或以上的電源平面。電源平面的設(shè)置滿足以下條件:

● 單一電源或多種互不交錯的電源;

● 相鄰層的關(guān)鍵信號不跨分割區(qū);地的層數(shù)除滿足電源平面的要求外,還要考慮:

● 元件面下面(第 2 層或倒數(shù)第 2 層)有相對完整的地平面

● 高頻、高速、時鐘等關(guān)鍵信號有一相鄰地坪面

● 關(guān)鍵電源有一對應(yīng)地平面相鄰。

b) 信號層數(shù)

基本布局完成后,根據(jù)布線密度對所需的層數(shù)進(jìn)行大致判斷。然后結(jié)合板上的工作頻率、有特殊布線要求的信號數(shù)量以及性能要求與成本承受能力,最后確定信號層數(shù)。

2) 性能指標(biāo)與成本要求

在設(shè)計(jì)過程中,需根據(jù)產(chǎn)品定位、 推出時間、 質(zhì)量要求等相關(guān)方面,進(jìn)行統(tǒng)一評估,以達(dá)到最佳的性價比。

為了盡快將穩(wěn)定產(chǎn)品推向市場,在開發(fā)的初始階段,過于強(qiáng)調(diào)成本、加工工藝因素毫無疑問會對產(chǎn)品的開發(fā)進(jìn)度、質(zhì)量造成一定的影響。

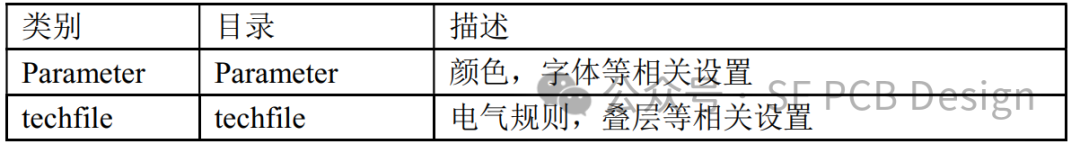

3) 環(huán)境規(guī)則導(dǎo)入

在 SVN 的 SOURCE 下面,將逐步添加相關(guān)環(huán)境規(guī)則,具體分類如下:

4) 電源層、地層、信號層的相對位置

a) 電源、地平面的阻抗以及電源、地之間的 EMC 環(huán)境問題

● 電源、地平面存在自身的特性阻抗,電源平面的阻抗比地平面阻抗高;

● 為降低電源平面的阻抗,盡量將 PCB 的主電源平面與其對應(yīng)的地平面相鄰排布并且盡量靠近,利用兩者的耦合電容,降低電源平面的阻抗;

● 電源、地平面構(gòu)成的平面電容與 PCB 上的退耦電容一起構(gòu)成頻響曲線比較復(fù)雜的電源、地電容,它的有效退耦頻帶比較寬。

b) 電源、地作為參考平面,兩者的區(qū)別

電源、地平面均能作參考平面,且有一定的屏蔽作用,但相對而言,電源平面具有較高的特性阻抗,與參考電平存在較大的電位差;從屏蔽的角度,地平面一般均作了接地處理,并作為基準(zhǔn)電平參考點(diǎn),其屏蔽效果遠(yuǎn)遠(yuǎn)優(yōu)于電源平面

在選擇參考平面時,應(yīng)優(yōu)選地平面。

c) 電源層、地層、信號層的相對

板層的排布一般原則:

● 元件面下面(第二層或倒數(shù)第二層)為地平面,提供器件屏蔽層以及為頂

層布線提供參考平面;

● 所有信號層盡可能與地平面相鄰;

● 盡量避免兩信號層直接相鄰;

● 主電源層盡可能與其對應(yīng)地相鄰;

● 兼顧層壓結(jié)構(gòu)對稱。

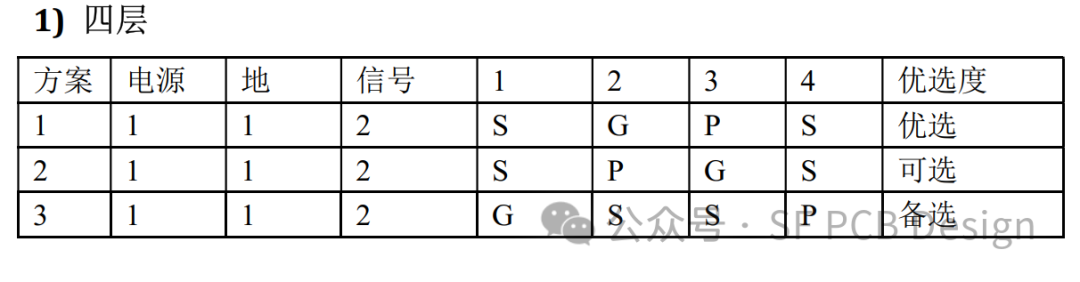

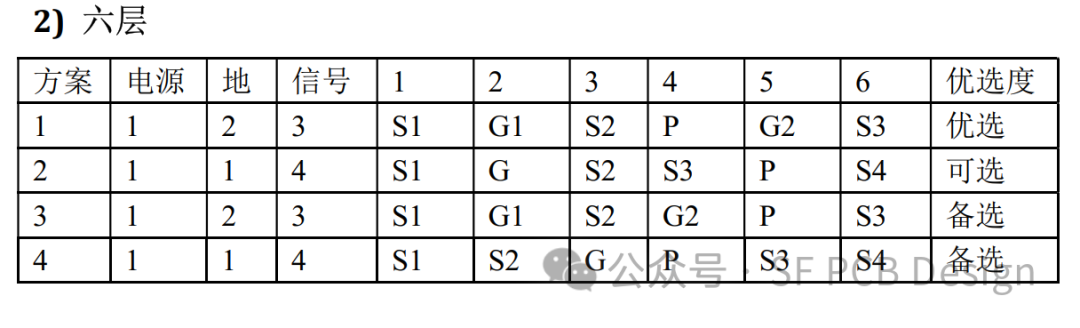

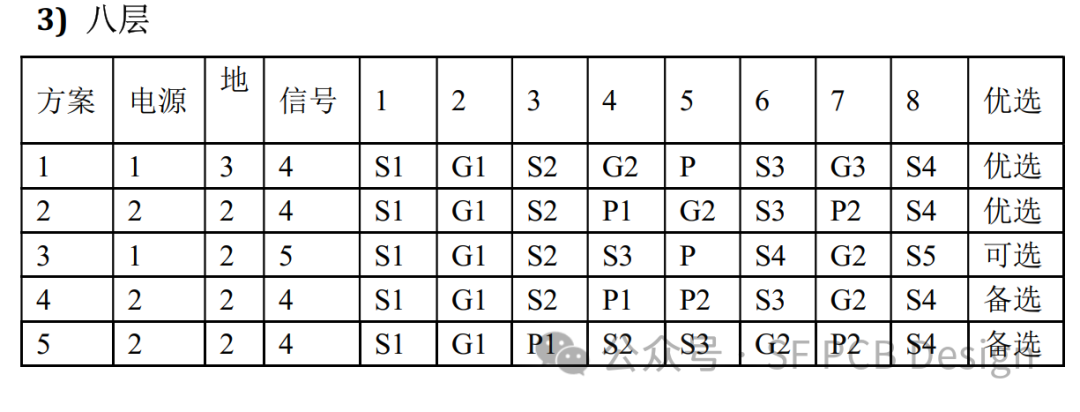

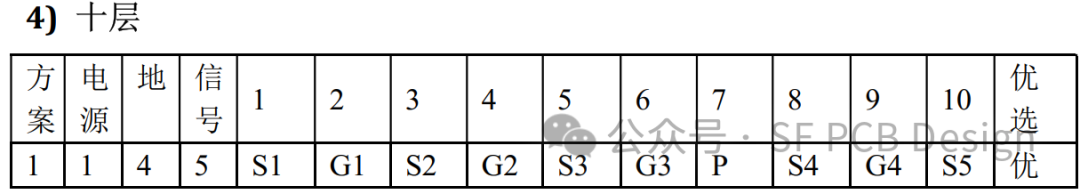

2.5.2. 具體層數(shù)設(shè)置探討

S 代表信號層,G 代表地層,P 代表電源層

2.6 布線

2.6.1 線寬和線間距設(shè)置

線寬和線間距設(shè)置需考慮以下因素:

1) 單板密度。

單板密度越高,使用更細(xì)的線寬和更窄的線間距。

2) 信號的電流強(qiáng)度。

當(dāng)信號平均電流較大時,需考慮布線寬度所能承受的電流多小。經(jīng)寬與電流關(guān)系可參照以下表格:

注 A:用銅皮作導(dǎo)線通過大電流的時候,銅箔寬度的載流量應(yīng)參照表中的數(shù)值降低 50%去選擇。

注 B:在 PCB 加工作,通常用 OZ(盎司)作為銅皮厚度單位,1 盎司銅厚的定義為1 平方

英尺面積內(nèi)銅箔重量為一盎司。對應(yīng)的物理厚度為 35UM,2OZ 的厚度為 70UM。

3) 可靠性要求。

在可靠性要求高時,使用較寬的布線和較大的線間距。

4) PCB 加工限制。

現(xiàn)在國內(nèi)的 PCB 加工工藝為:推薦最小線寬/線間距為 6MIL/6MIL,極限線寬線間距為:4MIL6MIL。

2.6.2 孔的設(shè)置

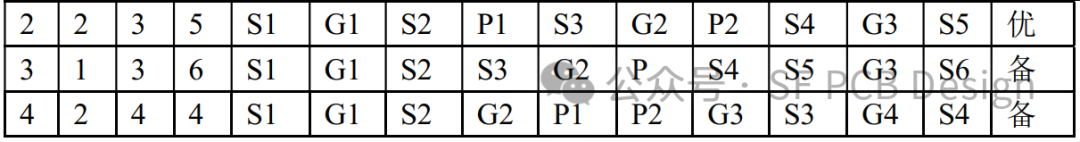

1. 制成板的孔的大小取決于板的厚度,板厚孔徑比應(yīng)介于 5-8 2. 過孔孔徑優(yōu)選系列如下(單位 MIL):

2.6.3 進(jìn)行 PCB 設(shè)計(jì)應(yīng)遵循的規(guī)則

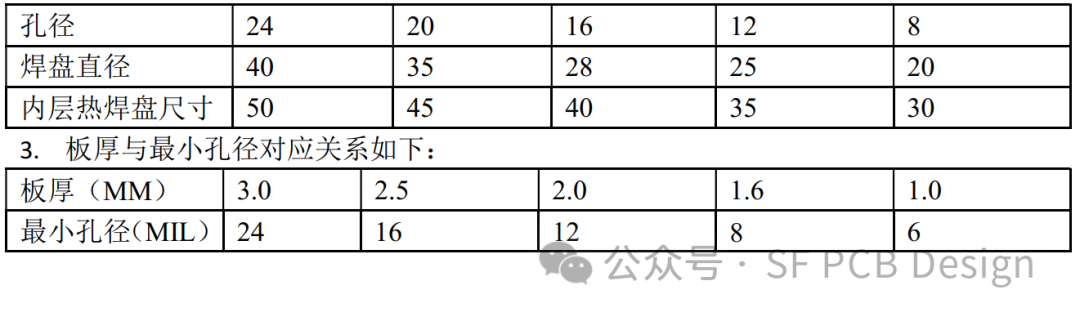

環(huán)路最小規(guī)則,即信號線與其回路構(gòu)成的環(huán)面積要盡可能小,環(huán)面積越小,對外的輻射越少,接收外界的干擾也越小。針對這一規(guī)則,在地平面分割時,要考慮地平面與重要信號走線的分布,防止由于地平面開槽等帶來的問題。在雙層板設(shè)計(jì)中,在為電源留下足夠空間的情況下,應(yīng)該將留下的部分用參考地填充,且增加一些必要的過孔,將雙面地信號有效連接起來,對一些關(guān)鍵信號盡量采用地線隔離,對一些頻率較高的設(shè)計(jì),需要特別考慮其也平面信號回路問題。

2) 串?dāng)_控制

串?dāng)_是指 PCB 上不同網(wǎng)絡(luò)這間因較長的平行布線引起的相互干擾,主要由于平行線間的分

布電容和分布電感的作用。解決串?dāng)_的主要措施是:

A、 加大平行布線的間距,遵循 3W 規(guī)則。

B、 在平行線間插入地線。

C、 減小布線層與地線間的距離。

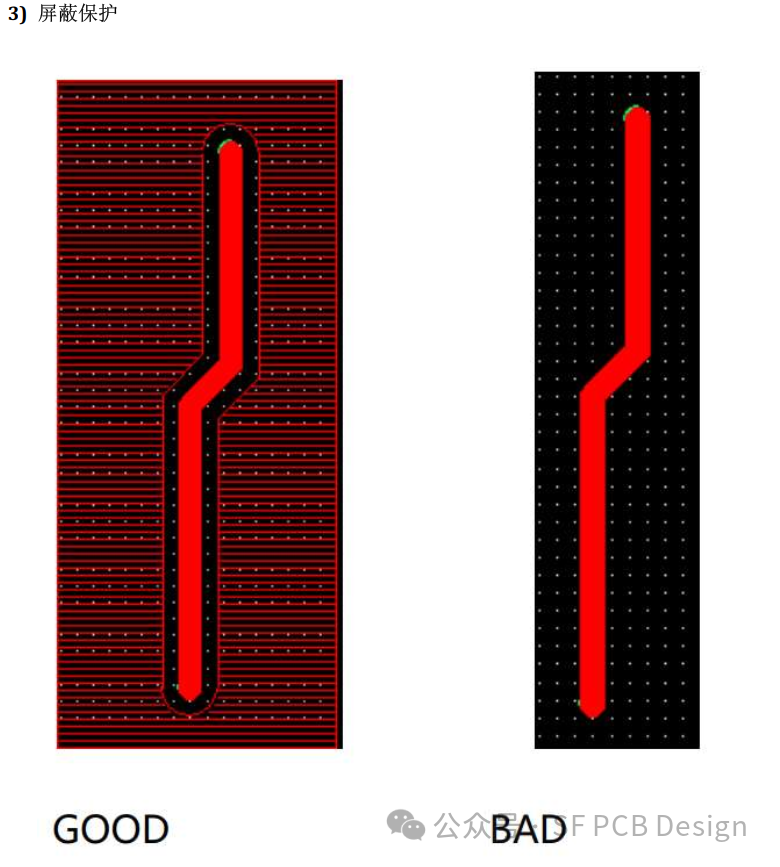

對應(yīng)地線回路規(guī)則,實(shí)際上也是為了盡量減小信號的回路面積,多見于一些比較重要的信號,如時鐘信號,同步信號。對一些特別重要,頻率特別高的信號,應(yīng)該考慮采用銅軸電纜屏蔽結(jié)構(gòu)設(shè)計(jì),即將所布的線上下左右同地線隔離,而且還要考慮好如何有效讓屏蔽地與實(shí)際地平面有效結(jié)合。

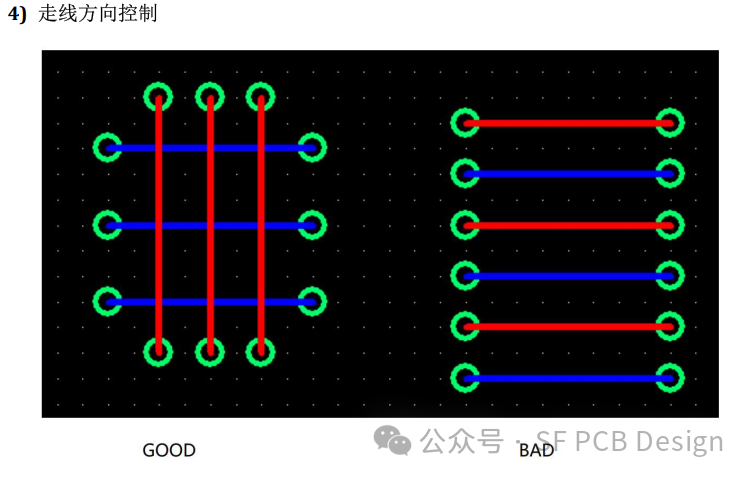

相鄰層的走線方向成正交結(jié)構(gòu)。避免將不同的信號線在相鄰層走成同一方向,以減少不必要的層間串?dāng)_。當(dāng)由于板結(jié)構(gòu)限制,難以避免出現(xiàn)該情況,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,有地信號線隔離各信號線。

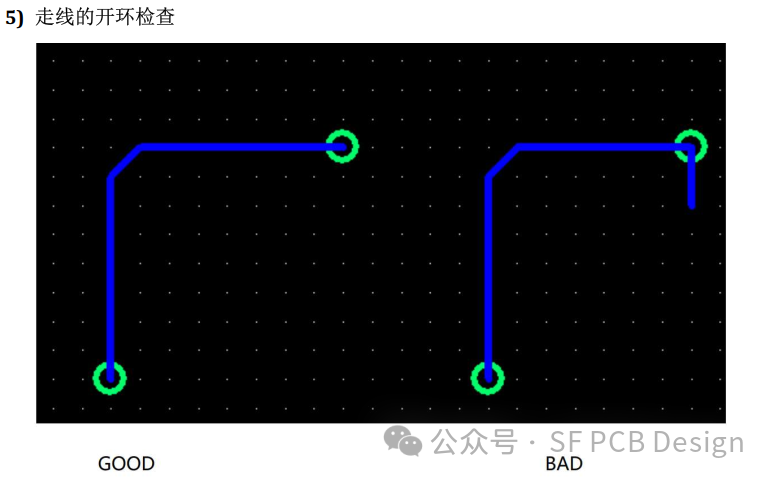

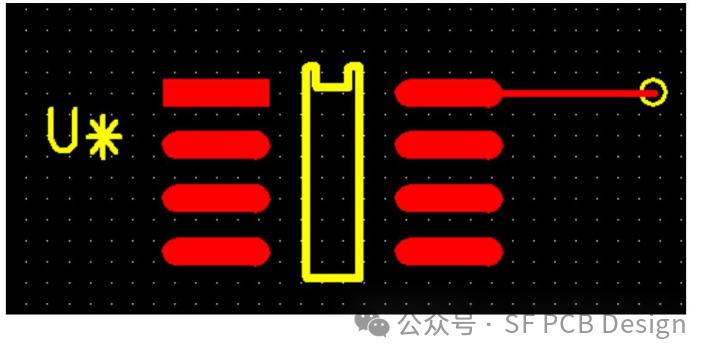

一般不允許出線一端浮空的走線。

主要以免產(chǎn)生不必要的天線效應(yīng),減小不必要的干攏輻射和接收,帶來不必要的不可預(yù)知的錯誤和問是。

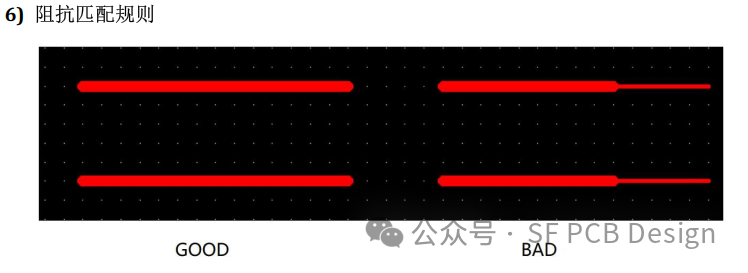

同一網(wǎng)線的布線寬度應(yīng)盡量保持一致,線寬的變化會變成線路的特征阻抗不均勻,不傳輸速率較高時,會產(chǎn)生發(fā)射。在設(shè)計(jì)中應(yīng)盡量避免這種情況的發(fā)生。在有些條件下,如BGA 走線,可能無法避免這種情況的發(fā)生。在這種情況下,應(yīng)盡量減小中間寬度不一致的走線的有效長度。

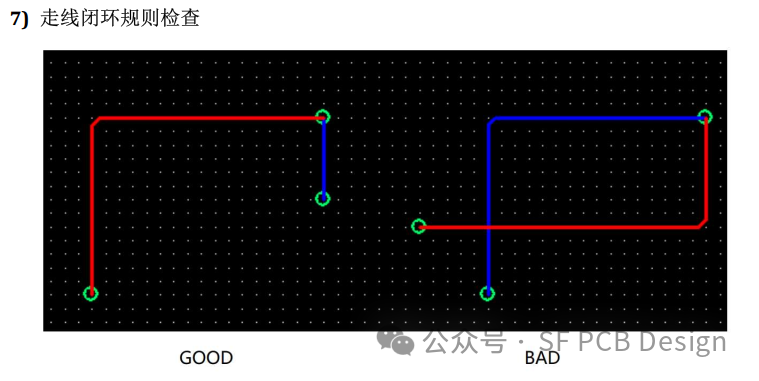

信號線在各個不同層走線,不能形成自環(huán),特別在多層板設(shè)計(jì)中,容易產(chǎn)生這樣的問題。自環(huán)將引起幅射干擾。

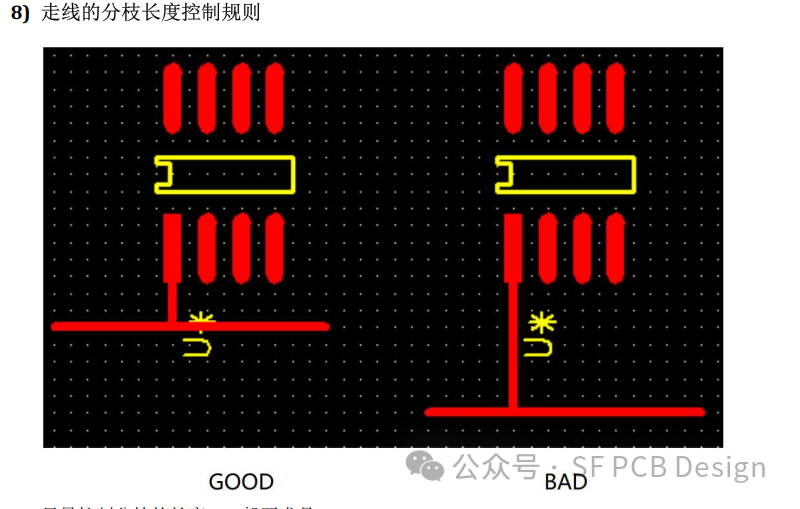

盡量控制分枝的長度,一般要求是 Tdelay<=Trise/20

9) 走線長度控制

在設(shè)計(jì)時,應(yīng)該盡量讓布線長度盡量短,以減少由于走線過長帶來的干擾問題,特別是一些重要信號線,如時鐘線,務(wù)必將其振蕩器放在離器件很近的地方。對驅(qū)動多個器件的情況,應(yīng)根據(jù)具體情況決定采用何種網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)。

10) 走線的諧振規(guī)則:

主要針對高頻信號設(shè)計(jì)而言,即布線長度不得與其波長成整數(shù)倍關(guān)系,以免產(chǎn)生諧振現(xiàn)象。

11) 走線倒角

PCB 設(shè)計(jì)中應(yīng)避免產(chǎn)生銳角和直角,直角和銳角會產(chǎn)生不必要的輻射,同時工藝性能也不好。

12) 器件去藕

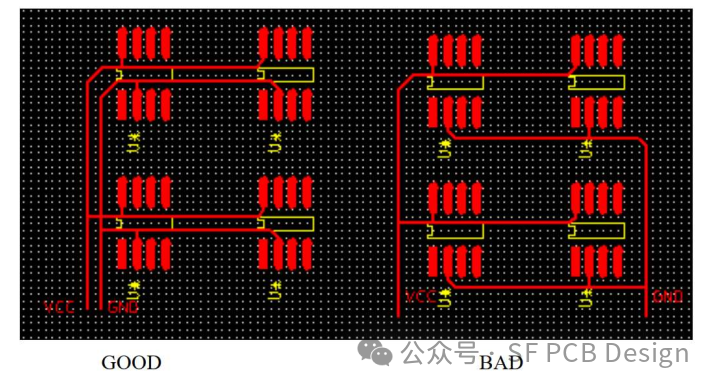

A、 在線路板上,加上必要的去藕電容,濾去電源上的干擾信號,使電源穩(wěn)定。在多層板中,對電源的去藕電容,要求不是很高,但是在雙層板子,去藕電容的布局和布線方式,將直接影響到整個系統(tǒng)的穩(wěn)定性。

B、 在雙層板設(shè)計(jì)中,一般應(yīng)該使電流先經(jīng)過濾波電容濾波再供器件使用,同時還要充分考慮到由于器件產(chǎn)生的電源噪聲對下游的器件的影響,一般來說,采用總線結(jié)構(gòu) 設(shè)計(jì)比較好,在設(shè)計(jì)時,還要考慮到由于傳輸距離過長而帶來的電壓跌落給器件造成的影響,必要時增加一些電源濾波環(huán)路,避免產(chǎn)生電位差,影響系統(tǒng)穩(wěn)定性。

C、 在高速電路設(shè)計(jì)中,能否正確使用去藕電容,直接影響系統(tǒng)的穩(wěn)定性。D、 去藕電容一般布在芯片電源輸入處,越靠近電源,效果越好。

A、 主要是為了防止不同工作頻率的模塊之間的相互干擾,同時,盡量縮短高頻部分的走線長度。通常將高頻部分布在接口部分減少走線長度,同時,也要考慮低頻信號可能受到的干擾。在處理高頻和低頻部分的地,一般采用兩者分割,再在接口處單單點(diǎn)接地。B、 對模擬數(shù)字混合信號的處理,同樣也是一般采用分別布在線路板的兩邊,走線也走在不同的兩個層上。

14) 孤立銅區(qū)控制

孤立銅區(qū)的出現(xiàn),將會帶來一些不可控的問題,因此孤立銅和別的信號連接將有助改善信號質(zhì)量。一般將孤立銅區(qū)和地平面相連。

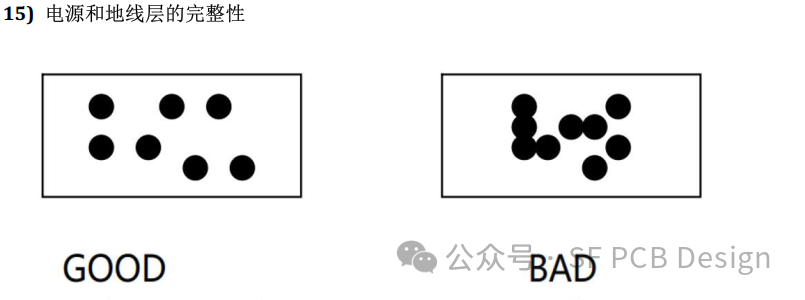

在過也密集區(qū)域,應(yīng)注意避免過孔在電源和地層平面探空區(qū)域相互連接,形成對平面的分割,從面破壞整個平面的完整性,導(dǎo)致信號回路面積增大。

16) 重疊電源和地層規(guī)則

不同電源,在空間上要避免重疊。主要是為了減小電源平面之間的干擾,特別是一些電壓相差比較大的電源層之間,必須想辦法避免重疊,如果實(shí)在沒辦法避免重疊,則需在兩個電源之間加上一個地層。

17) 3W 規(guī)則

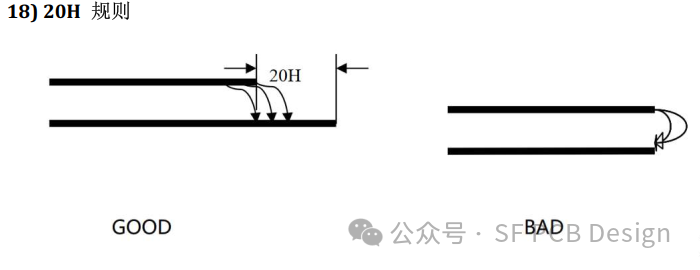

為了減少線間串?dāng)_,應(yīng)該保持線間有足夠?qū)挼木€間距離,當(dāng)線中心距不少 3T 時,則可保持 70%的電場不相互干擾,稱為 3T 規(guī)則。如果要在到 98%的電場不相互干擾,則需要 10T。

由于電源層和地層之間的電場是變會在,在電路板邊緣會向外輻射電磁干擾,稱為邊緣效應(yīng)。解決辦法是電源層內(nèi)縮,使得電場只能在接地層內(nèi)傳導(dǎo),以 H(電源和地之間的介質(zhì)厚度)為單位,若縮進(jìn)去 20H,則 70%的電場在接地層內(nèi)傳導(dǎo),或 100H,則 98%的電場在接地層同傳導(dǎo)。

2.6.4 具體布線原則

2.6.4.1 電源和地平面

1) 盡量給出單獨(dú)的電源層和地層,即使要在表層接線,電源線和地線也要盡量的短而

且要足夠粗。

2) 對于多層板,一般都有電源層和地層,需要注意的只是模擬部分和數(shù)字部分的地和

電源即使電壓相同也要分割開來。

3) 對于雙層板電源線應(yīng)盡量粗而短,電源線和地線的寬度要求可以根據(jù) 1MM 的線寬

最大對應(yīng) 1A 的電流來計(jì)算,電源和地構(gòu)成的環(huán)路盡量小。

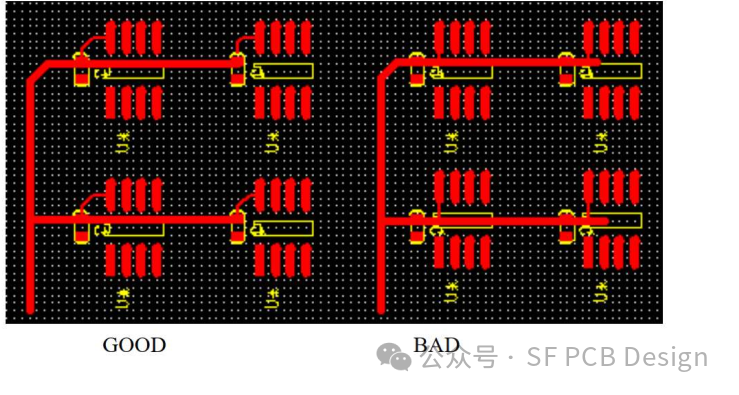

4) 為了防止電源線較長時,電源線上的藕合雜訊直接進(jìn)入負(fù)載器件,應(yīng)在進(jìn)入每個負(fù)

載器件之前進(jìn)行去藕,且為了防止各器件之間的相互干擾,需對每個器件進(jìn)行獨(dú)立

去藕。并且做到先濾波,再進(jìn)行負(fù)載器件。

2.6.5 特殊信號布線

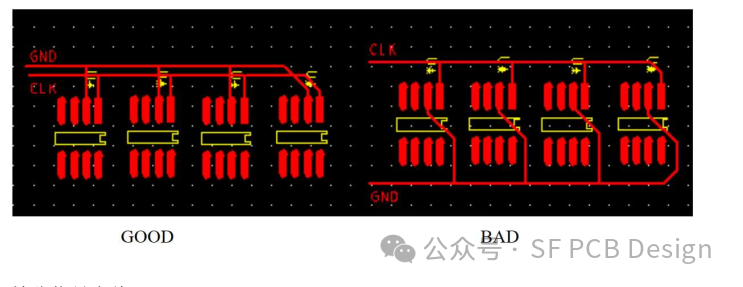

1) 時鐘布線

● 時鐘作為對 EMC 最大的影響之一,走時鐘線應(yīng)盡量少打過孔,盡量避免和其它信號線平行,且應(yīng)遠(yuǎn)離信號線,避免對信號線干擾。

● 同時應(yīng)該避開電源部分,以避免電源和時鐘互相干擾。

● 當(dāng)一個線路板上有多個不同頻率的時鐘信號時,兩個不同頻率的時鐘不可并行走線。

● 時鐘線應(yīng)盡量避免靠近輸出接口,以免高頻時鐘藕合到 CABLE 線上并延線發(fā)射出去。

● 如果板上有專門的時鐘芯片,時鐘芯片下不能走線,應(yīng)該在其下方鋪銅,必要時可以對他進(jìn)行單獨(dú)割地。

● 對于很多芯片都有參考晶振,這些晶振下方也不可以走線,要鋪銅隔離。晶振外殼需接地。

● 對于雙層板,沒有電源和地層,時鐘走線方式如下:

2) 差分信號布線

● 成對差分線,一般平行走線,盡量少打過也,必需打過孔時,必須兩對線同時打,

以做到阻抗匹配。

3) 相同屬性的信號線

相同屬性的一組總線,應(yīng)盡量并排走線,并且盡量做到等長。

4) 一些基本的走線原則

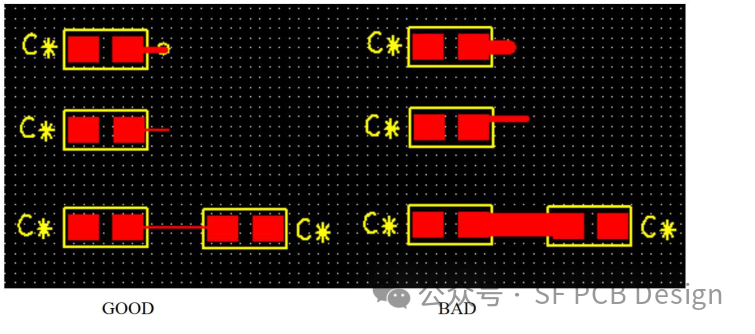

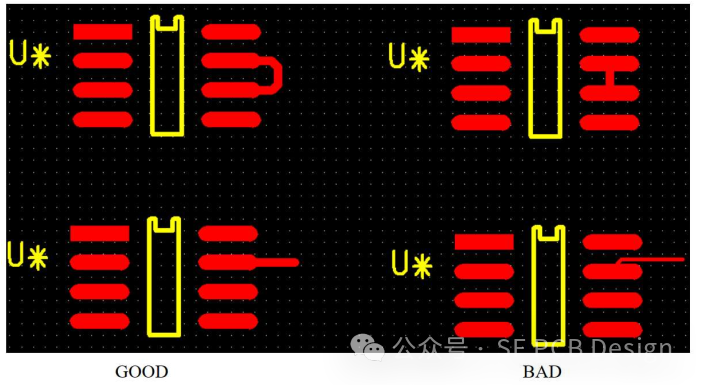

● 考慮到散熱,連焊等因素,正確的走線方法如下:

● 兩焊盤間距很小時,焊盤間不可直接相連

● 從貼片焊盤引出的過孔盡量遠(yuǎn)離焊盤

2.6.6 工藝設(shè)計(jì)要求

2.6.6.1. 所有器件都應(yīng)有唯一的標(biāo)號。

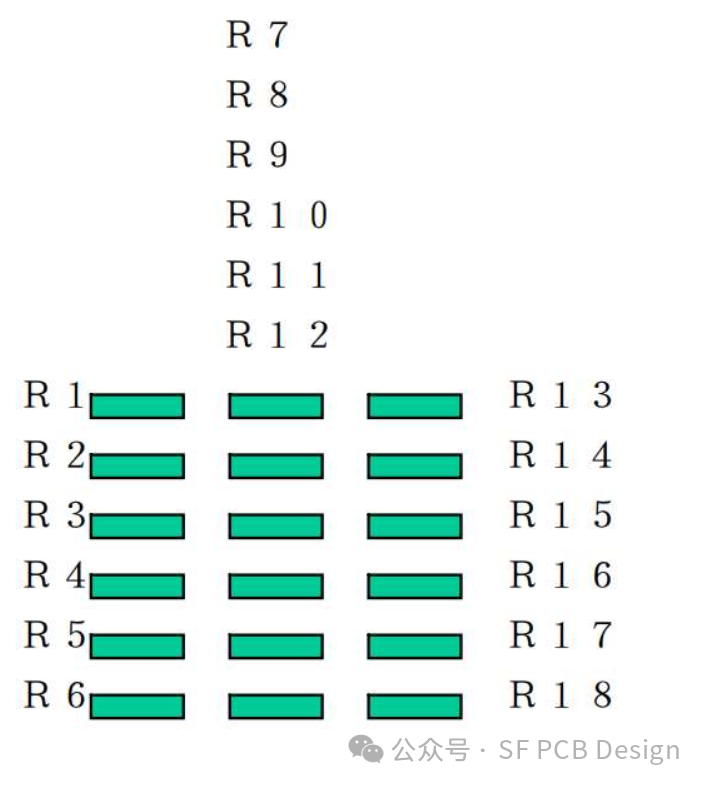

2.6.6.2. 器件的標(biāo)號應(yīng)盡量靠近所指的器件, 盡量避免標(biāo)號遠(yuǎn)離所指器件或與兩個器件的距離相近等使生產(chǎn)人員無法識別的情況。

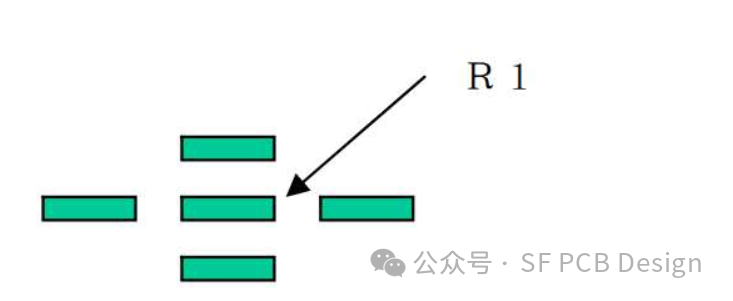

● 如下圖中的標(biāo)號 R1 就比較難以識別。

2.6.6.3. 器件的標(biāo)號必須在 X 軸方向,只有一個方向,在 Y 軸上,也只有一個方向。2.6.6.4. 器件在線路板設(shè)計(jì)完成后,需要重新排,按照從左到右,從上到下依次增大。2.6.6.5. 當(dāng)器件周圍確實(shí)沒有空間放置標(biāo)號時,可采用如下二圖所示的變通方法。

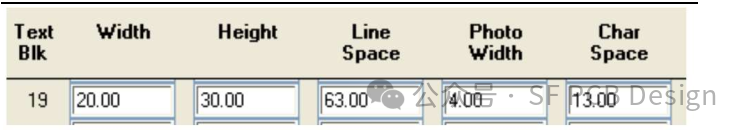

2.6.6.6. 器件位號,板子名稱,版本,編碼的字體大小一律采用如下圖的 19 號字。

2.6.6.7. 在決定板子的整體的放置方向時,應(yīng)考慮在使用過程中需要進(jìn)行手工操作的器件本身的標(biāo)識方向。

2.6.6.8. 在撥動開關(guān)邊上應(yīng)有表格說明每一位撥動開關(guān)的作用,在所有接插件邊上除了器件標(biāo)號外也應(yīng)有必要的說明,如輸入輸出,正負(fù)極性等,所有指示燈邊上也應(yīng)有簡單的內(nèi)容說明。

2.6.6.9. 電阻(包括排阻)標(biāo)號采用 R+編號,電容采用 C+編號,撥動開關(guān)采用 S+編號,集成塊(包括晶振)采用 U+編號,二極管采用 D+編號,接插件(包括跳線開關(guān))采用 J+編號,變壓器采用 T+編號,線圈電感采用 L+編號,振蕩器采用 X+編號。

2.6.6.10. 板上有極性的器件(如電解電容、直流電源),必須注明正極(或能唯一確定其安裝方向標(biāo)識)的位置。

2.6.6.11. 所有線路板,設(shè)計(jì)完成后,需加上線路板版本信息,格式如下:

● 第一行:線路板名稱

● 第二行:線路板版本號

● 第三行:線路板設(shè)計(jì)日期

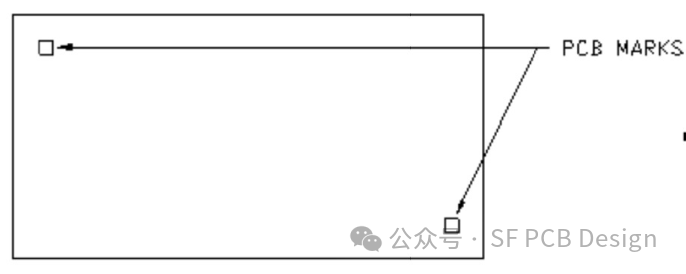

2.6.6.12. 在 PCB 板上上,必須設(shè)計(jì)條形碼貼放位置和 PASS 標(biāo)簽的位置。如下圖:

2.6.6.13. 在 PCB 板上空的位置,需添加防靜電標(biāo)志,如果 PCB 非常密集,可以不加。防靜電標(biāo)志在 PCB 庫的 Format symbols 下面的 ESD 標(biāo)志。

2.6.6.14. 在用貼片元件的 PCB 板上,為了提高貼片元件的貼裝準(zhǔn)確性,PCB 板上必須設(shè)有校正標(biāo)志(MARKS),且每一塊板最少要兩個標(biāo)記,分別設(shè)于 PCB 的一組對角上,如下圖:

審核編輯:湯梓紅

-

原理圖

+關(guān)注

關(guān)注

1297文章

6338瀏覽量

233805 -

元器件

+關(guān)注

關(guān)注

112文章

4709瀏覽量

92206 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4683瀏覽量

85545

原文標(biāo)題:PCB 設(shè)計(jì)規(guī)范

文章出處:【微信號:SF PCB Design,微信公眾號:SF PCB Design】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

解讀PCB設(shè)計(jì)規(guī)范

解讀PCB設(shè)計(jì)規(guī)范

評論