勢壘電容(Barrier Capacitance)的大小直接影響了半導體器件的電學性能和可靠性。

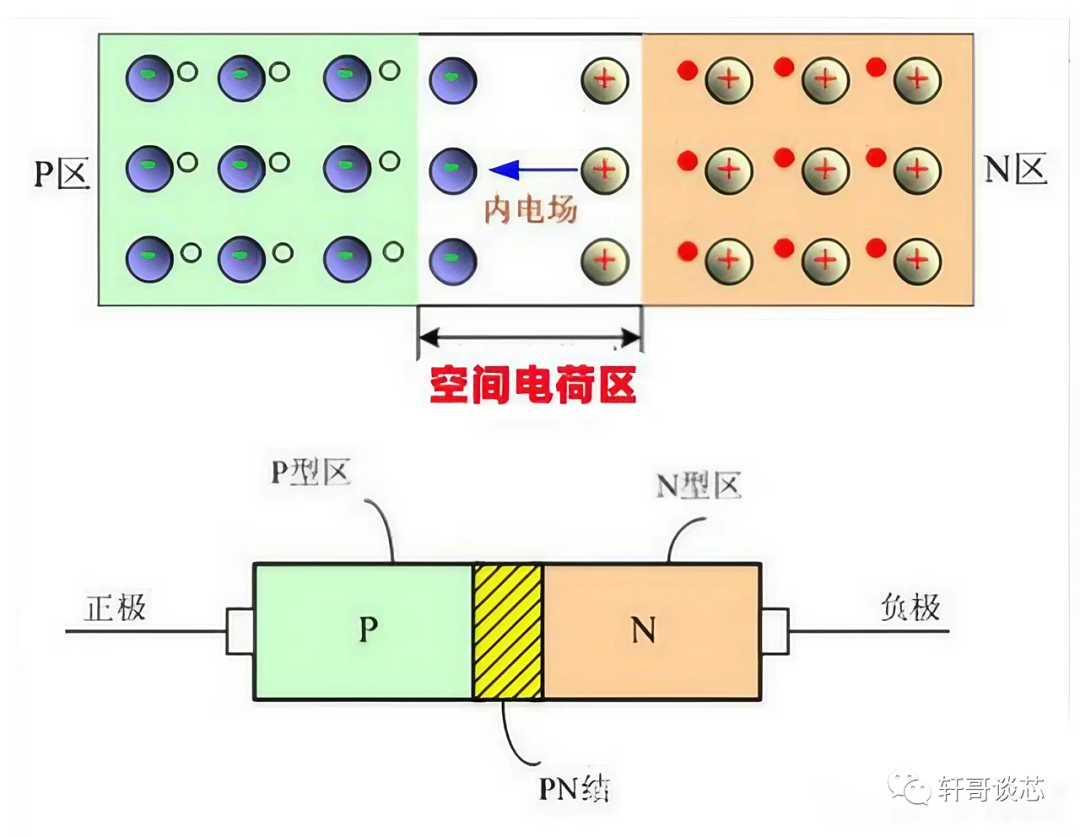

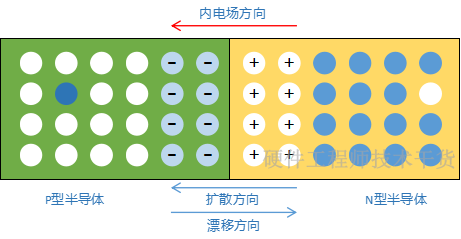

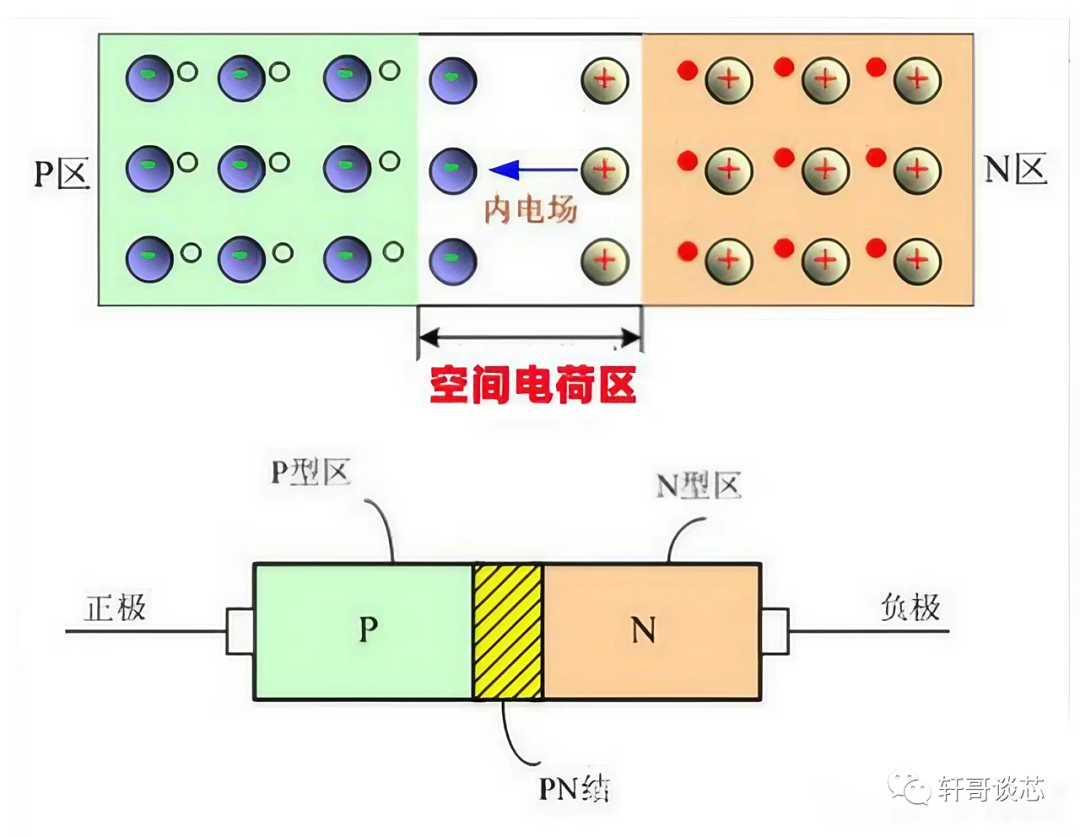

勢壘電容CB是由勢壘區中的電荷量QB和勢壘區的寬度W決定的。勢壘區是指PN結或金屬-半導體接觸處,由于內建電場的作用,電子和空穴被限制在兩個區域之間形成的一個耗盡層。勢壘區的寬度W是指勢壘區在垂直于電流方向上的長度。

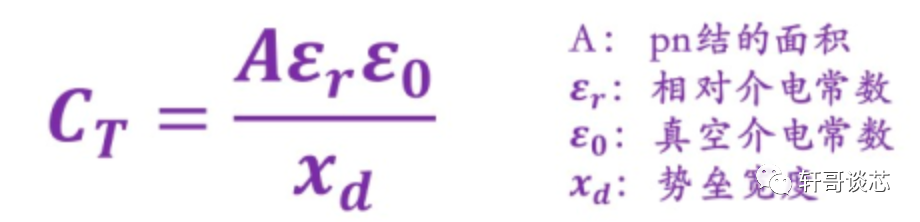

勢壘電容的大小可以理論的計算一下:

當外加電壓有△U 的變化時,電荷有△Q 的變化,假設兩邊的距離為 Xd 時。勢壘電容為:

勢壘電容CB的大小還與勢壘區的載流子濃度、內建電場強度以及溫度等因素有關。當載流子濃度較高時,勢壘區內的電荷量增加,勢壘電容也會相應增大;當內建電場強度較大時,勢壘區內的電荷量減少,勢壘電容也會相應減小;當溫度升高時,載流子濃度增加,勢壘區內的電荷量增加,勢壘電容也會相應增大。

此外,勢壘電容還可以用于制備電容器、存儲器等電子設備。例如,利用金屬-半導體接觸處的勢壘電容可以實現非揮發性存儲器的設計和制備。非揮發性存儲器是一種可以在斷電后保持存儲信息的電子設備,具有廣泛的應用前景。

總之,勢壘電容是半導體器件中的一個重要參數,它描述了PN結或金屬-半導體接觸處的勢壘對電荷的存儲能力。勢壘電容的大小與勢壘區的寬度、載流子濃度、內建電場強度以及溫度等因素有關。通過合理設計和控制勢壘電容的大小,可以提高半導體器件的性能和可靠性,實現各種電子設備的功能和應用。

-

半導體

+關注

關注

335文章

28967瀏覽量

238835 -

電容

+關注

關注

100文章

6259瀏覽量

154407 -

電荷

+關注

關注

1文章

653瀏覽量

36786

發布評論請先 登錄

類比法學習勢壘電容和擴散電容

肖特基勢壘二極管的特征

淺析肖特基勢壘二極管

肖特基勢壘二極管的特點

肖特基勢壘二極管電路設計

肖特基勢壘二極管,肖特基勢壘二極管是什么意思

SiC肖特基勢壘二極管和Si肖特基勢壘二極管的比較

評論