我們在初中物理就學過,電壓又稱電勢差,即任意兩個電勢/電位的差值,一般認為無窮遠處的電勢為0,通常說的“電壓”隱含條件就是相對于0電勢的差值,但這個“無窮遠處的0電勢”太含糊了,實際電路分析的時候不可能去探測到它。好在電壓跟絕對電勢無關,它只是一個差值,因此我們可以任意選擇電路中某一個電位作為參考基準點,人為規定它是0電勢點,則這個基準點就稱為“地”(Ground)。

人為定義好“地”以后,電路中任一點的電壓就有了參考。說“電阻一端的電壓是5V”,實際上是說“電阻某一端對地的電壓是5V”,但如果說“電阻兩端的電壓是5V”,已經明確了是以電阻的某一端作為參考,并不以“地”為參考。

根據應用場合不同,又人為將“地”細分為“電源地”、“數字地”、“模擬地”、“射頻地”,有很多文章和理論分析介紹應該如何處理電路中不同的“地”。本文僅淺談一下自己對“射頻地”的一些認識。

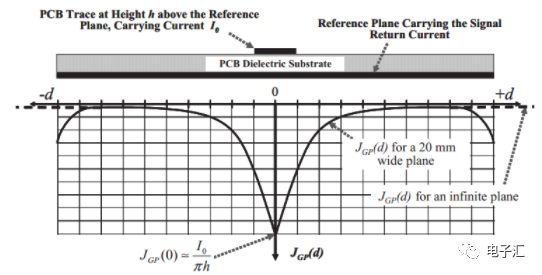

微帶線回流的大小分布,如下圖所示。電流分布在微帶線的下方,且隨著距離微帶線正下方的距離越遠,電流幅度越小。

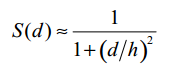

電流的分布,可以近似用以下公式表示:

其中,d是在回流平面上距跡線中心線的水平距離,h是介質厚度。

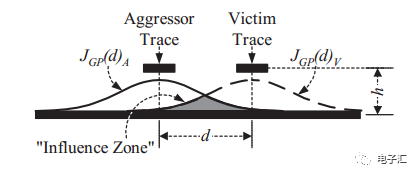

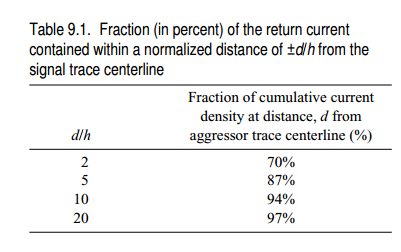

兩根平衡走線,如果靠的比較近,就會有一部分回流重疊,隨著d的距離的增大,在距離d范圍內的電流越多,其數據關系如下表所示:

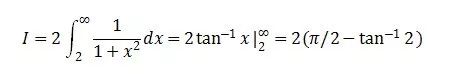

表中也可以通過對S(d)積分,然后進行計算得到。比如對于d/h=2時,則在d=2h以外的電流即為:

而總電流為:

所以包含在-d~d以內的電流的百分比為:

與上表中吻合。按同樣的計算方法,可計算出當d=5h/10h/20h時,分別對應的值為87.4%/93.7%/96.8%。

地孔怎么加?

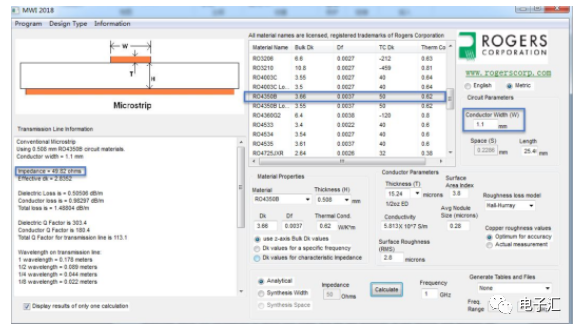

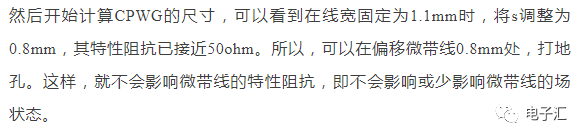

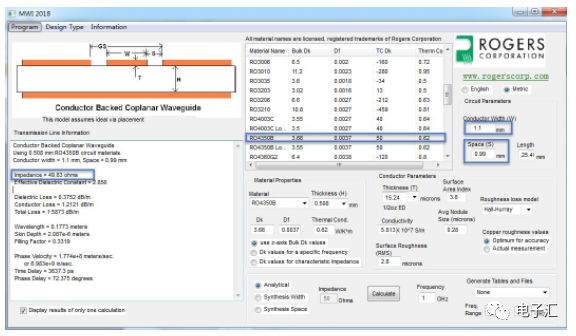

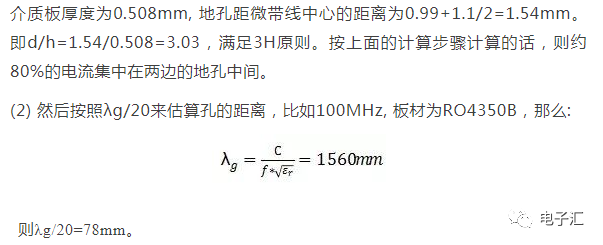

接下來,看看在這個尺寸下,滿足3H原則么?

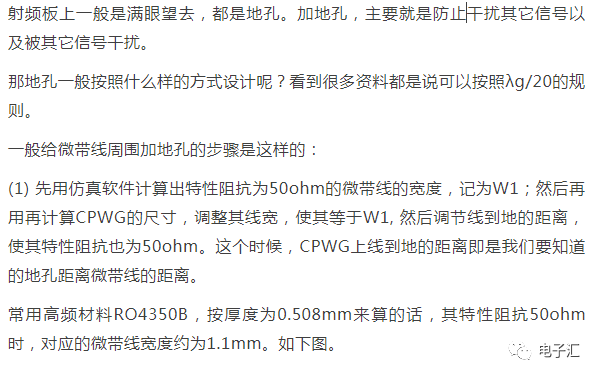

如果從這方面來看的話,整個射頻板可能只需要打幾個過孔就行了。不過,沒有見過這樣做的。一般射頻板都是被打成篩子的。

在算出來的λg/20比較大的時候,我一般是選擇2mm~2.5mm的間隔打,如果λg/20比較小,就適當減小間隔,但是需要保證:

廠家能加工

不要把其他平面打斷(這在數字板中經常需要注意,不要把電源平面打斷)

怎么看待打孔可以增加隔離度呢?

在文獻[3]中,用波導截止頻率的觀點來闡述了這個現象。

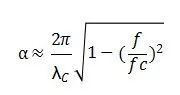

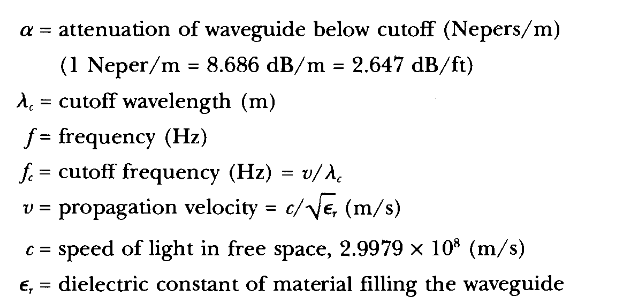

當信號進入小的縫隙或者非諧振盒子時,可以用波導的截止信號的衰減公式來估算。

不過,我按照這個公式算下來的話,發現,如果是一排過孔,孔間距是2mm,孔的大小是0.3mm的話,算出來的經過過孔的衰減值才3.92dB,比我想象中的值小多了。這都有點讓我不相信這公式的正確性。

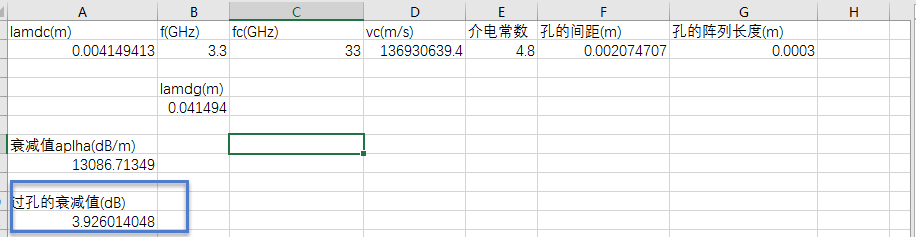

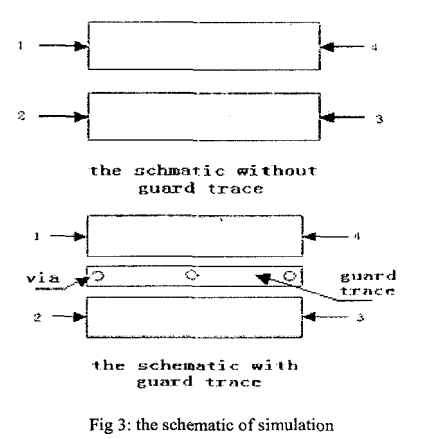

但是,當看到文獻[4]時,我想,這公式可能是對的。文中,對下述原理圖進行了仿真。

以下是仿真結果。發現量級也就在幾個dB左右。隔離度還是主要取決于兩個微帶線的距離。

差分線的布地

下面,再簡單說一下差分線周圍的地線。

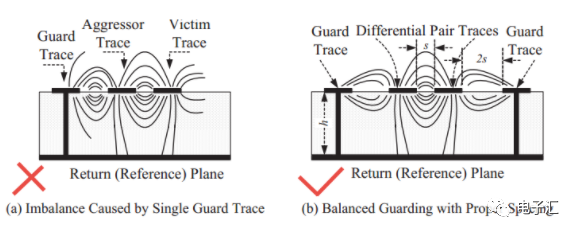

在給差分信號加保護地的時候,為了不破壞差分線之間的平衡關系,要求兩邊同時加地,而且要求地與差分線的距離至少要大于兩倍的差分線的間距,這個還需要考慮信號到參考層的距離(H)。

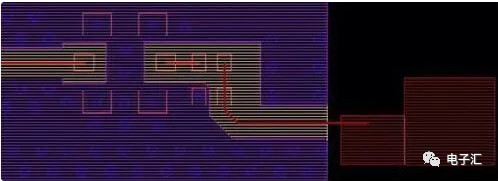

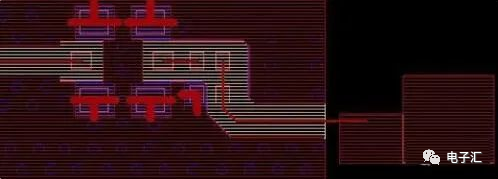

舉個例子,我們將對多層電路板進行射頻線仿真,為了更好的做出對比,將仿真的PCB分為表層鋪地前的和鋪地后的兩塊板分別進行仿真對比;表層未鋪地的PCB文件如下圖1所示(兩種線寬):

圖1a:現款0.1016mm的射頻線(表層鋪地前)

圖1b:現款0.35mm的射頻線(表層鋪地前)

圖1:表層為鋪過地的PCB

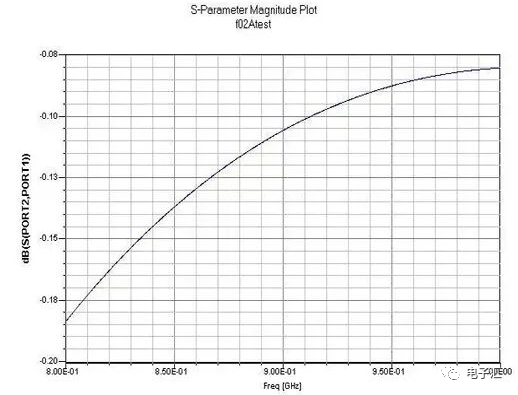

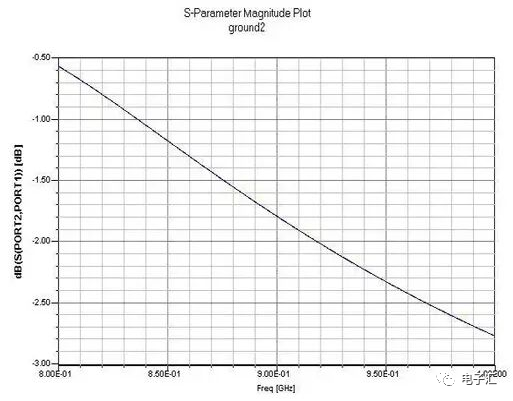

首先將線寬不同的兩塊板(表層鋪地前)導入仿真軟件中,在目標線上加入50Ω端口。針對不同線寬0.1016mm和0.35mm, 我們的仿真結果如圖2所示,圖中顯示的曲線是S21,仿真頻率范圍為800MHz-1GHz。

圖2a:表層為鋪地的S21(線寬0.1016mm)

圖2b:表層未鋪地的S21(線寬0.35mm)

圖2:表層未鋪地的S21

由圖中可以看到,在800MHz-1GHz的范圍內,仿真的數據展示為小數點后一到兩位的數量級,0.35mm的損耗要比0.1016mm的線小一個數量 級,這是因為0.35mm的線寬在該板的層疊條件下其特征阻抗接近50Ω。 因此間接驗證了我們所做的阻抗計算(用線寬約束)是有一定作用的。

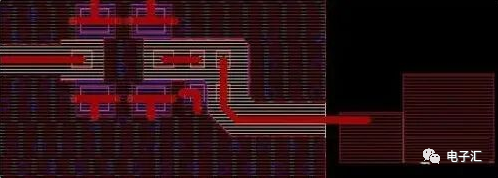

接下來,我們做了表層鋪地后的同樣的仿真(800MHz-1GHz),導入的PCB文件如下圖:

圖3a:0.1016mm的射頻線(表層鋪地)

圖3b:0.35mm射頻線(表層鋪地)

圖3:表層鋪過地的PCB

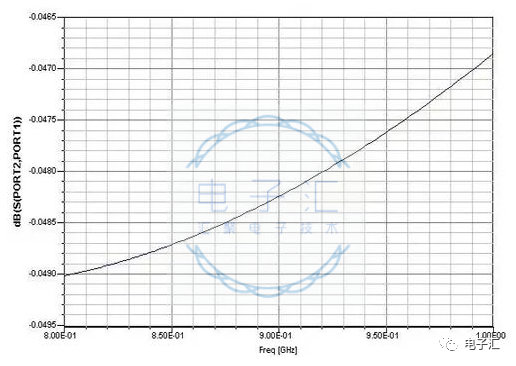

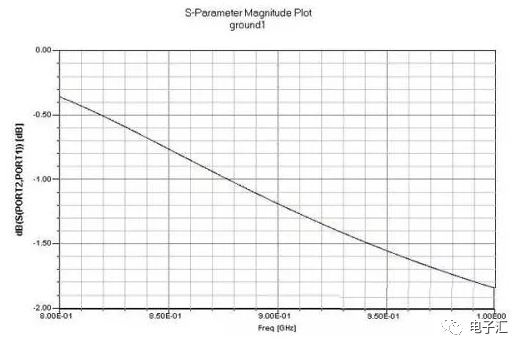

仿真結果如下圖所示:

圖4a:表層鋪地后的S21(線寬0.1016mm)

圖4b:表層鋪地后的S21(線寬0.35mm)

圖4:表層鋪地后的S21

由圖中看到,仿真的數據顯示,該傳輸線的線損已經是1-2 dB的數量級了,當然0.35 mm的損耗要明顯小于0.1016 mm的。另外一個明顯的現象是相對于未鋪地的仿真結果,隨著頻率由800MHz到1GHz的增加,損耗趨大。

我們可以從仿真的結果中得到這樣一個結果:

射頻走線按50歐姆走,可以減小線損;

表層的鋪地事實上是將一部分RF信號能量耦合到了地上,造成了一定的損耗。因此PCB表層的鋪地應該有所講究。盡量遠離RF線。工程經驗是大于1.5倍的線寬。

-

射頻

+關注

關注

106文章

5782瀏覽量

170883 -

電路板

+關注

關注

140文章

5154瀏覽量

103365 -

電壓

+關注

關注

45文章

5718瀏覽量

118449

原文標題:射頻電路板上的地孔以及仿真說明介紹[20240114]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

射頻電路板設計法則

PCB線路板中的盲孔和埋孔介紹

淺談射頻電路板上的地孔以及仿真說明

電路的原理圖設計、電路仿真、印制電路板設計與信號完整性分析

一文詳解半孔pcb電路板設計

激光焊錫應用:插件孔的大小對PCB電路板的影響

評論