芯片短缺難題遲遲未得到緩解,半導體產業鏈正在尋求創新的解決方案來解決這一問題,并致力于提高效率,延長設備壽命。

從汽車、物聯網和消費電子領域,到芯片制造和測試設備,芯片短缺幾乎影響了全球供應鏈,芯片制造工具和設備因缺芯延遲安裝交付,上游材料也面臨供應不足的情況,包括氣體、KrF光刻膠、CMP漿料,甚至不銹鋼。目前,這些問題仍無法輕松解決,而且這些上游原材料與芯片制造設備及工具,與芯片制造的全部流程都相互關聯,因此僅在一個領域擴充產量并不能解決所有問題。測試儀、光刻膠濾光片和封裝基板,以及任何用于直接處理這些晶圓的設備和材料短缺,都將會導致ASIC短缺。

“除了具有極長交貨周期的FPGA之外,ATE還使用了許多定制ASIC,這些ASIC必須爭奪晶圓廠產能,”泰瑞達(Teradyne)戰略業務開發經理Ken Lanier指出。“我們很久以前就對上游材料市場進行了積極的投資,保證供應鏈安全,努力為客戶提供合理的交貨時間。”

然而,人工智能、機器學習、數字孿生體等新興技術的發展,將會進一步改善晶圓廠封裝協調、快速識別良率問題、穩固供應鏈,并為半導體行業在人才短缺的環境中提供優質工具,助力產業實現卓越增長。

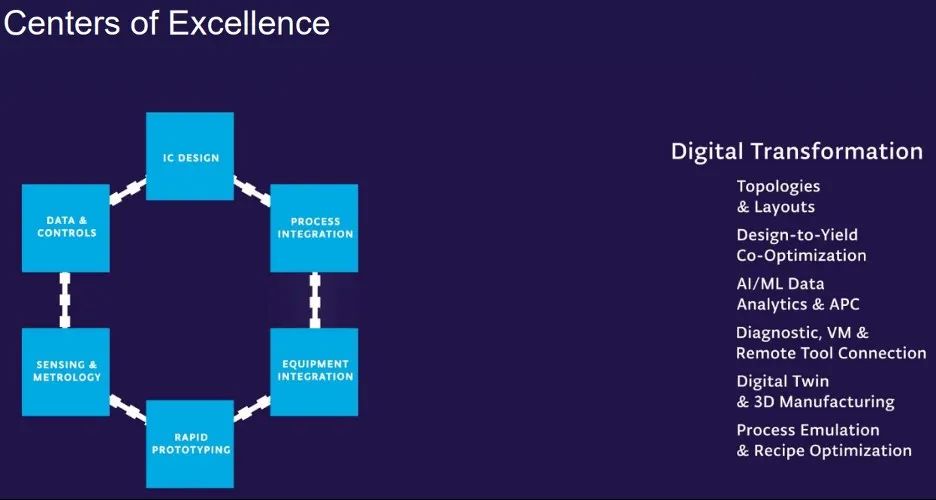

TEL總裁Nate Baxter指出,該公司將數字工具納入芯片設計、工藝設備和計量(虛擬和硬件)流程,并解釋了這些工具如何在公司創新中心使用,例如在其位于紐約州奧爾巴尼的美國研發、制造和工具集成總部。該公司在創新中心執行EUV光刻、FEOL、BEOL和用于封裝的異構集成,TEL設備目前利用超過15,000個傳感器來實現更快的過程診斷、先進的過程控制和數據分析。

圖1:為了實現行業增長預測,晶圓廠正在采用能夠提高良率、生產率和智能制造的技術(圖源:TEL、SEMI ISS)

在最近的先進半導體制造大會(ASMC)上,幾場演講都討論了在晶圓廠中使用機器學習和人工智能來提高良率、工具性能和運營效率。在工具級別,高級建模正在改進流程、庫存管理和元件利用率。例如,在晶圓加工工具中,特定元件的生命周期可以根據工藝溫度、化學特性和其他因素而變化。

“在客戶與客戶之間、工具與工具之間以及工具內元件的位置之間,半導體工具在工藝條件方面都存在很大差異。這些因素都會顯著影響零件的可靠性。例如,兩個氣動閥,一個暴露在惡劣的環境條件下,另一個在同一工具內的既定環境條件下運行,可能具有不同的使用壽命,”泛林集團(Lam Research)的可靠性工程師Swajeeth Panchangam解釋道。

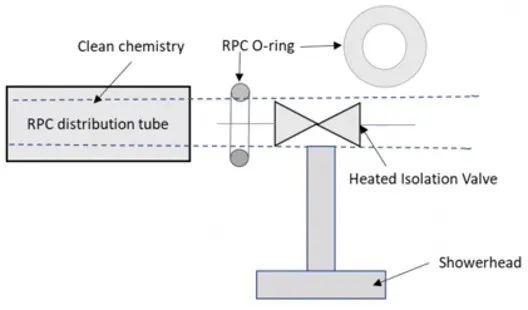

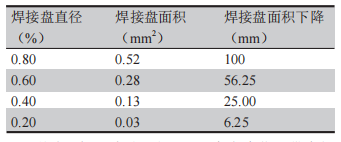

泛林集團為元件生命周期開發了一種新的可靠性模型,在這種情況下,該模型確定了相同的 O 形圈,相對于較低的工藝溫度下,進行較高溫度工藝時可以可靠地減少40%的晶圓。Panchangam 指出,這樣的模型可以幫助工程師更好地規劃所需的庫存,并根據實際組件建模安排預防性維護。

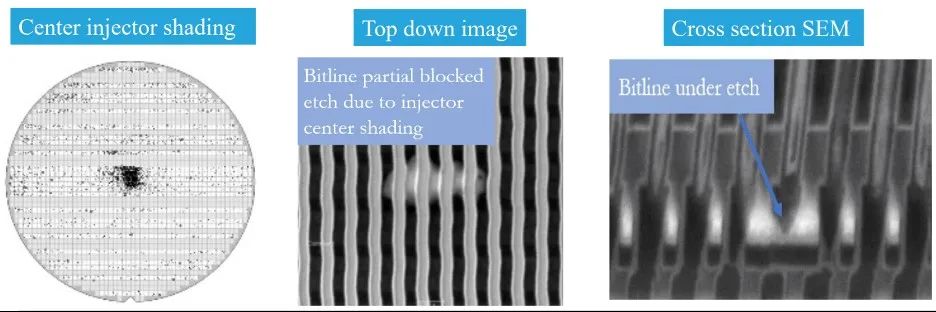

在某些情況下,工程師會大幅修改其工藝,以提高良率和所生產芯片的質量,這對延長組件壽命具有可喜的好處。例如,由于電感耦合等離子體刻蝕機中的空氣分子污染導致位線刻蝕不完整,美光的300mm存儲器工廠正面臨著客戶退貨。

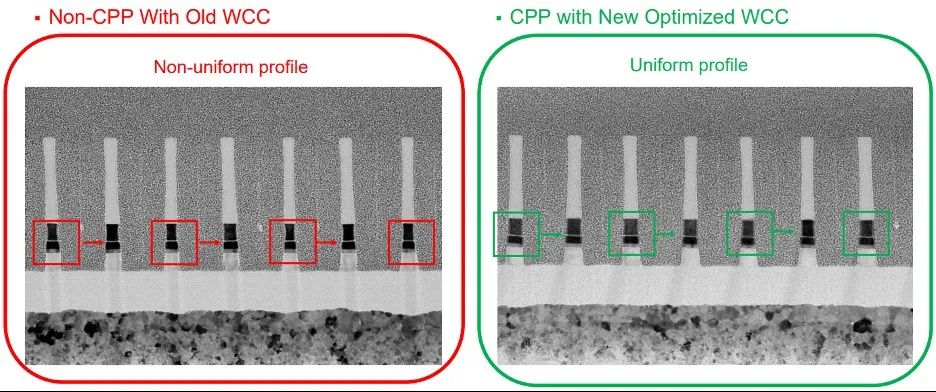

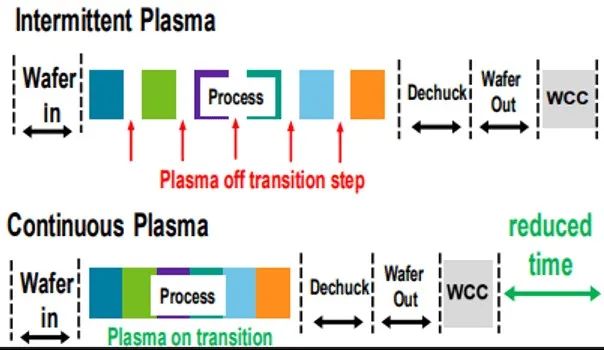

“我們開發了一種新的連續等離子體工藝(CPP)刻蝕,消除了幾個刻蝕步驟之間的穩定壓力,并改進了無晶圓腔清潔(WCC),以消除系統性的良率偏移,并避免了客戶在這種故障機制中重復,”美光技術人員Jeff Ye表示。

最大限度地提高元件和工具的可靠性

由于晶圓遇到的各種工藝條件,組件生命周期建模很難執行。

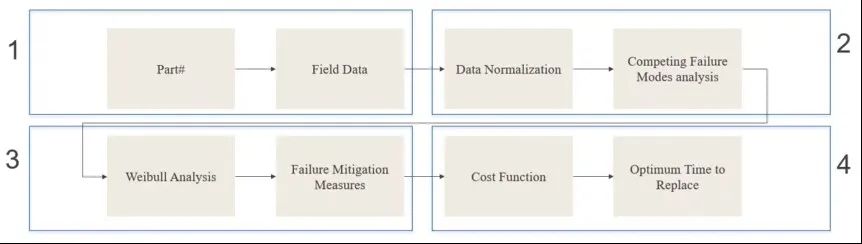

“對于如何使用現場數據模擬半導體組件的壽命,需要一個系統的指南。”泛林集團的Panangam指出,在估算組件的壽命時,工程師通常使用經驗模型。問題是這些往往是保守的,通過不必要的更換縮短了組件的使用壽命,并且由于更頻繁的零件更換和系統停機時間而增加了成本。他還表示,卓越的生命周期建模能夠在需要時優化預防性維護和庫存。

“我們提出了一個使用現場數據的模型,隔離故障模式,并理解引發根本故障的物理原理,”Panagam表示。“我們確定新應用程序的操作條件,并查看故障機制是否正在改變或保持不變。”

現有工藝具有腐蝕性的工藝化學性質和溫度,新工藝中在較高溫度下進行。隨機模型可估計新工藝溫度下的壽命分布。使用成本函數來確定O形圈更換的最佳時間。(工程團隊報告了更換零件的處理時間(以小時為單位),即使實際跟蹤了加工的晶圓數量,以保護客戶的數據。Panangam的團隊確定故障模式(由于化學侵蝕而導致的O形圈磨損)是相同的,但O形圈的最佳使用壽命為2500小時,而在此前較低的工藝溫度下為4000小時。結果有助于為該過程安排適當的PM間隔,并保持足夠的零件庫存。“現在,當我們必須對組件進行調用時,模型和成本函數將指導生產環境中的潛在更換,”Panagam表示。

圖 2:最佳更換周期基于隨機建模、故障模式和動作的可靠性分析以及成本函數(圖源:Lam Research、SEMI ASMC)

圖3:RPC替代從4000到2500小時(晶圓設備),通過基于場數據的更高熱量負載

(圖源:Lam Research、SEMI ASMC)

刻蝕機遠程等離子清洗套件中的O形圈磨損

生命周期模型、成本函數提供O型圈更換時間,可靠性工藝工程師偶爾會確定現場故障是由系統性工具問題引起的。第二個示例顯示了如何重新設計現有流程以解決現場故障,從而顯著提高流程吞吐量并降低零件更換成本。

在其位于弗吉尼亞州馬納薩斯的DRAM工廠,美光在300mm ICP刻蝕機上開發了一種新的連續等離子工藝,并采用了改進的無晶圓腔室清潔 (WCC)。該公司經歷了一些存儲設備故障,這些故障集中在晶圓中心。工程團隊假設這些缺陷可能是由于在等離子 DC 偏壓未開啟時碎片從 ICP 蝕刻噴射器落到晶圓上造成的。

“多年來,我們一直在努力通過各種工藝改進來解決這個問題,但我們決定引入連續等離子體工藝的想法,以及一種新的無晶圓腔室清潔(WCC)來永遠解決這個問題,”美光的Ye表示,他在SEMI最近的ASMC上介紹了新工藝。

空氣中的分子污染問題導致不必要的工具停機(更換經過重新設計的噴射器),但最重要的是,客戶設備會退回。集成的多步驟刻蝕和腔室清潔有大約20個步驟。對于新工藝,Ye的團隊使用300mm素晶圓進行在線表征和探針,使用SEM / EDX識別污染物,并使用TEM來檢查位線CD測量和輪廓。美光決定實施連續等離子體蝕刻工藝,因為修整刻蝕、硬掩模1、2等之間的穩定性步驟會造成污染。

“就像冰箱一樣,關閉再打開也無濟于事,等離子刻蝕室也是如此,”Ye指出。“這導致了連續等離子體工藝 (CPP),以及無晶圓清潔從低壓等離子體到高壓等離子體的變化,以激活等離子體中的更多自由基,從而實現卓越的碳氟化合物去除。WCC 由三個步驟組成——侵蝕性等離子蝕刻、O2 燃燒,然后是電介質調節步驟以涂覆腔室,”Ye 表示。“我們調整了內外氣體噴射器的比例,以更好地清除噴射器壁上堆積的碎屑。”

最終的工藝配方參數調整導致位線刻蝕曲線均勻。美光的結果表明,良率提高了 1%,由于原始加工時間縮短了 8%,刀具良率大幅提高,良率偏移導致的刀具停機時間減少,降低了ICP蝕刻機的新型和返工氣體噴射器成本。

“現在我們不需要經常更換噴油器,良率偏差更少,位線控制和輪廓更出色,并且避免了客戶的退貨授權,”Ye指出。“我們將把這種新的、最著名的方法轉移到先進的技術節點上。”

圖4:晶圓中心污染引起未完成的刻蝕出現存儲位線缺陷(圖源:Micron、SEMI ASMC)

圖5:改進的位線剖面圖是連續腔等離子刻蝕、優化離子注入和優化晶圓刻蝕前工藝調節(圖源:Micron、SEMI ASMC)

圖6:新工藝消除了蝕刻步驟之間的穩定過渡,并優化了WCC以清潔更多副產品,從而延長部件壽命

(圖源:Micron、SEMI ASMC)

總結

人工智能日益滲透至半導體芯片制造流程,通過使用多個工具傳感器估算組件壽命和診斷的新模型,能夠改善良率問題。從工具到晶圓廠級別的工程解決方案將結合更先進的建模、機器學習和反饋機制,以更快地解決問題,并保持工具和晶圓廠生產出優質的設備。

-

asic

+關注

關注

34文章

1199瀏覽量

120436 -

人工智能

+關注

關注

1791文章

47183瀏覽量

238259 -

半導體芯片

+關注

關注

60文章

917瀏覽量

70611

原文標題:如何構建芯片可靠性模型?

文章出處:【微信號:CloudBrain-TT,微信公眾號:云腦智庫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

季豐RA新添可靠性試驗設備恒溫恒濕箱

驅動鈦絲(SMA)的可靠性設計(4) 力量設計

驅動鈦絲(SMA)的可靠性設計(3) 響應時間的設計

PCB高可靠性化要求與發展——PCB高可靠性的影響因素(上)

SGS受邀參加Ansys車規芯片功能安全和可靠性研討會

基于可靠性設計感知的EDA解決方案

汽車功能安全與可靠性的關系

請問FATFS文件系統可靠性如何?

中芯國際獲CNAS認可,車載芯片可靠性專項檢測中心獲認證

如何確保IGBT的產品可靠性

IGBT的可靠性測試方案

如何構建芯片可靠性模型?

如何構建芯片可靠性模型?

評論