VLSI設(shè)計(jì)驗(yàn)證及其方法的重要性

在 VLSI(超大規(guī)模集成)的動(dòng)態(tài)世界中,對(duì)創(chuàng)新產(chǎn)品的需求比以往任何時(shí)候都更高。從概念到功能齊全的產(chǎn)品的過(guò)程涉及許多挑戰(zhàn)和不確定性,其中設(shè)計(jì)驗(yàn)證通過(guò)確認(rèn)設(shè)計(jì)滿足其預(yù)期要求和規(guī)格,在確保復(fù)雜電子系統(tǒng)的功能和可靠性方面發(fā)揮著關(guān)鍵作用。據(jù) Research and Markets 稱,到 2023 年,全球 VLSI 市場(chǎng)預(yù)計(jì)價(jià)值 6622 億美元。據(jù)市場(chǎng)分析師預(yù)測(cè),到 2028 年,其價(jià)值將達(dá)到 9717.1 億美元,復(fù)合年增長(zhǎng)率 (CAGR) 為 8%。

在本文中,我們將探討設(shè)計(jì)驗(yàn)證的概念、其重要性、涉及的過(guò)程、使用的語(yǔ)言和方法,以及超大規(guī)模集成電路設(shè)計(jì)發(fā)展中這一關(guān)鍵階段的未來(lái)前景。

什么是設(shè)計(jì)驗(yàn)證及其重要性?

設(shè)計(jì)驗(yàn)證是一個(gè)系統(tǒng)化的過(guò)程,用于驗(yàn)證和確認(rèn)設(shè)計(jì)滿足其指定的要求并遵守設(shè)計(jì)指南。這是產(chǎn)品開(kāi)發(fā)周期中至關(guān)重要的一步,旨在及早發(fā)現(xiàn)并糾正設(shè)計(jì)問(wèn)題,以避免在開(kāi)發(fā)后期階段進(jìn)行成本高昂且耗時(shí)的返工。設(shè)計(jì)驗(yàn)證可確保最終產(chǎn)品,無(wú)論是集成電路 (IC)、片上系統(tǒng) (SoC) 還是任何電子系統(tǒng),都能正確可靠地運(yùn)行。 SoC 和 ASIC 驗(yàn)證在實(shí)現(xiàn)可靠和高性能集成電路方面發(fā)揮著關(guān)鍵作用。

VLSI設(shè)計(jì)驗(yàn)證涉及兩種類型的驗(yàn)證:

功能驗(yàn)證

靜態(tài)時(shí)序分析

這些驗(yàn)證步驟至關(guān)重要,需要在設(shè)計(jì)的各個(gè)階段進(jìn)行時(shí)執(zhí)行,以確保最終產(chǎn)品滿足預(yù)期要求并保持高質(zhì)量。

功能驗(yàn)證:

它是 VLSI 設(shè)計(jì)的關(guān)鍵階段,旨在確保在各種操作條件下使用的芯片的正確功能。它涉及測(cè)試設(shè)計(jì)以驗(yàn)證其行為是否符合預(yù)期規(guī)格和功能要求。這個(gè)驗(yàn)證階段至關(guān)重要,因?yàn)槌笠?guī)模集成電路設(shè)計(jì)變得越來(lái)越復(fù)雜,在開(kāi)發(fā)過(guò)程中必然會(huì)出現(xiàn)人為錯(cuò)誤或設(shè)計(jì)缺陷。 VLSI設(shè)計(jì)中的功能驗(yàn)證過(guò)程如下。

識(shí)別和準(zhǔn)備:在此階段,確定設(shè)計(jì)要求并準(zhǔn)備驗(yàn)證計(jì)劃。該計(jì)劃概述了后續(xù)驗(yàn)證步驟的目的、目標(biāo)和策略。

規(guī)劃:驗(yàn)證計(jì)劃準(zhǔn)備好后,規(guī)劃階段涉及資源分配、設(shè)置測(cè)試環(huán)境以及創(chuàng)建測(cè)試用例和測(cè)試平臺(tái)。

開(kāi)發(fā):開(kāi)發(fā)階段的重點(diǎn)是使用適當(dāng)?shù)恼Z(yǔ)言和方法對(duì)測(cè)試平臺(tái)和測(cè)試用例進(jìn)行編碼。此階段還包括構(gòu)建和集成模擬和仿真環(huán)境,以促進(jìn)徹底的測(cè)試。

執(zhí)行:在執(zhí)行階段,測(cè)試用例在設(shè)計(jì)上運(yùn)行以驗(yàn)證其功能和性能。這通常涉及廣泛的模擬和仿真器以涵蓋所有可能的場(chǎng)景。

報(bào)告:最后,驗(yàn)證過(guò)程以生成詳細(xì)報(bào)告結(jié)束,包括錯(cuò)誤報(bào)告、覆蓋率統(tǒng)計(jì)數(shù)據(jù)和總體驗(yàn)證狀態(tài)。這些報(bào)告有助于確定需要改進(jìn)的領(lǐng)域,并為未來(lái)的設(shè)計(jì)迭代提供有價(jià)值的見(jiàn)解。

靜態(tài)時(shí)序分析(STA):

靜態(tài)時(shí)序分析是 VLSI 設(shè)計(jì)中的另一個(gè)關(guān)鍵步驟,重點(diǎn)是驗(yàn)證設(shè)計(jì)的時(shí)序要求。在 VLSI 設(shè)計(jì)中,時(shí)序至關(guān)重要,因?yàn)樗鼪Q定信號(hào)如何在芯片中傳播并影響集成電路的整體性能和功能。該過(guò)程用于確定設(shè)計(jì)中最壞情況和最佳情況的信號(hào)傳播延遲。它分析從源(輸入)到目的地(輸出)的時(shí)序路徑,并確保信號(hào)在所需的時(shí)鐘周期內(nèi)到達(dá)預(yù)期目的地,而不違反任何時(shí)序約束。在 STA 期間,設(shè)計(jì)被劃分為時(shí)間路徑,以便可以執(zhí)行時(shí)序分析。每個(gè)時(shí)間路徑由以下因素組成。

起始點(diǎn):時(shí)序路由的起始點(diǎn)是數(shù)據(jù)由時(shí)鐘邊沿啟動(dòng)或需要在特定時(shí)間準(zhǔn)備就緒的位置。每個(gè)起始點(diǎn)必須有一個(gè)寄存器時(shí)鐘引腳或輸入端口。

組合邏輯網(wǎng)絡(luò):它包含沒(méi)有內(nèi)部存儲(chǔ)器的部分。組合邏輯可以使用 AND、OR、XOR 和反相器元件,但不能使用觸發(fā)器、鎖存器、寄存器或 RAM。

端點(diǎn):這是當(dāng)時(shí)鐘邊沿捕獲數(shù)據(jù)或必須在特定時(shí)間提供數(shù)據(jù)時(shí)時(shí)序路徑結(jié)束的位置。每個(gè)端點(diǎn)必須有一個(gè)輸出端口或一個(gè)用于寄存器數(shù)據(jù)輸入的引腳。

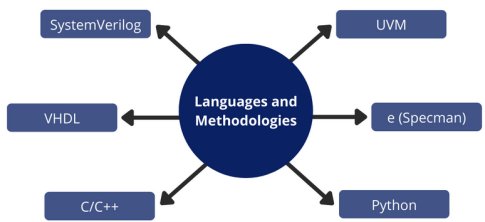

設(shè)計(jì)驗(yàn)證中使用的語(yǔ)言和方法

設(shè)計(jì)驗(yàn)證采用各種語(yǔ)言和方法來(lái)有效測(cè)試和驗(yàn)證 VLSI 設(shè)計(jì)。

SystemVerilog (SV) 驗(yàn)證:SV 提供了一組廣泛的驗(yàn)證功能,包括面向?qū)ο?a target="_blank">編程、約束隨機(jī)測(cè)試和功能覆蓋。

通用驗(yàn)證方法 (UVM):UVM 是一種基于 SystemVerilog 構(gòu)建的標(biāo)準(zhǔn)化方法,可實(shí)現(xiàn)可擴(kuò)展和可重用的驗(yàn)證環(huán)境,從而提高設(shè)計(jì)驗(yàn)證的效率和靈活性。

VHDL(VHSIC硬件描述語(yǔ)言):VHDL廣泛用于超大規(guī)模集成電路行業(yè)的設(shè)計(jì)輸入和驗(yàn)證,為硬件建模、仿真和綜合提供強(qiáng)有力的支持。

e(Specman):e是Yoav Hollander為其Specman軟件開(kāi)發(fā)的驗(yàn)證語(yǔ)言,提供強(qiáng)大的驗(yàn)證功能,例如約束驅(qū)動(dòng)的隨機(jī)測(cè)試和事務(wù)級(jí)建模。后來(lái)更名為 Verisity,并被 Cadence Design Systems 收購(gòu)。

C/C++ 和 Python:這些編程語(yǔ)言通常用于構(gòu)建驗(yàn)證框架、測(cè)試平臺(tái)和基于腳本的驗(yàn)證流程。

VLSI設(shè)計(jì)驗(yàn)證和方法

設(shè)計(jì)驗(yàn)證的優(yōu)點(diǎn)

有效的設(shè)計(jì)驗(yàn)證為超大規(guī)模集成電路行業(yè)提供了眾多優(yōu)勢(shì)。

它縮短了 VLSI 產(chǎn)品的上市時(shí)間

該過(guò)程確保符合設(shè)計(jì)規(guī)范

它增強(qiáng)了設(shè)計(jì)對(duì)不確定性的適應(yīng)能力

驗(yàn)證可最大限度地降低與設(shè)計(jì)失敗相關(guān)的風(fēng)險(xiǎn)

設(shè)計(jì)驗(yàn)證的未來(lái)

設(shè)計(jì)驗(yàn)證的未來(lái)看起來(lái)充滿希望。人工智能和機(jī)器學(xué)習(xí)輔助驗(yàn)證的新方法正在出現(xiàn),以有效解決驗(yàn)證挑戰(zhàn)。采用先進(jìn)的驗(yàn)證工具和方法將對(duì)提高驗(yàn)證過(guò)程的效率、有效性和覆蓋范圍發(fā)揮重要作用。此外,隨著SoC、ASIC和低功耗設(shè)計(jì)的發(fā)展,對(duì)專業(yè)VLSI驗(yàn)證的需求將持續(xù)上升。

設(shè)計(jì)驗(yàn)證是產(chǎn)品開(kāi)發(fā)過(guò)程中不可或缺的一部分,可確保可靠性、功能和性能。設(shè)計(jì)驗(yàn)證采用各種語(yǔ)言、方法和技術(shù)來(lái)解決復(fù)雜設(shè)計(jì)和新興技術(shù)帶來(lái)的挑戰(zhàn)。隨著技術(shù)格局的發(fā)展,設(shè)計(jì)驗(yàn)證將繼續(xù)在提供創(chuàng)新且可靠的產(chǎn)品以滿足不斷變化的世界的需求方面發(fā)揮至關(guān)重要的作用。

審核編輯 黃宇

-

芯片

+關(guān)注

關(guān)注

456文章

50936瀏覽量

424685 -

VLSI

+關(guān)注

關(guān)注

0文章

73瀏覽量

42931

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶圓制造recipe(工藝配方)的定義、重要性、種類及構(gòu)建和驗(yàn)證方式

選擇正版SolidWorks的重要性及如何避免盜版風(fēng)險(xiǎn)

關(guān)于蓄電池氣密性檢測(cè)儀重要性和使用方法

凱迪正大分享電纜交流電壓檢測(cè)的試驗(yàn)方法及其重要性

IO模塊的作用及其在工業(yè)生產(chǎn)中的重要性

武漢凱迪正大享電纜耐壓性檢測(cè):內(nèi)容、標(biāo)準(zhǔn)與重要性

PLC的I/O模塊的作用及其重要性

AC/DC電源模塊的原理、特點(diǎn)以及其在實(shí)際應(yīng)用中的重要性

VLSI設(shè)計(jì)驗(yàn)證及其方法的重要性

VLSI設(shè)計(jì)驗(yàn)證及其方法的重要性

評(píng)論