TTL邏輯電路多余的輸入端該如何處理?能否懸空?

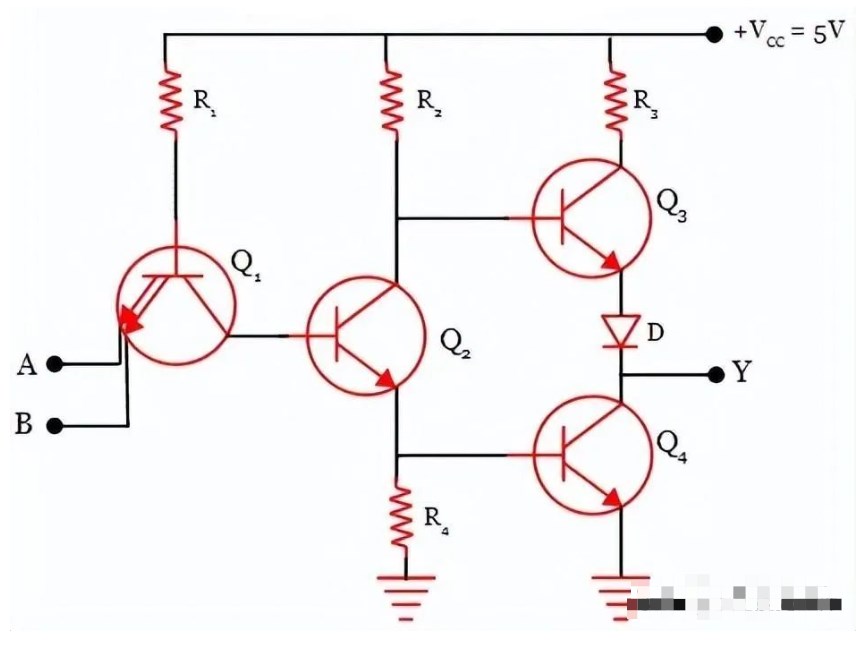

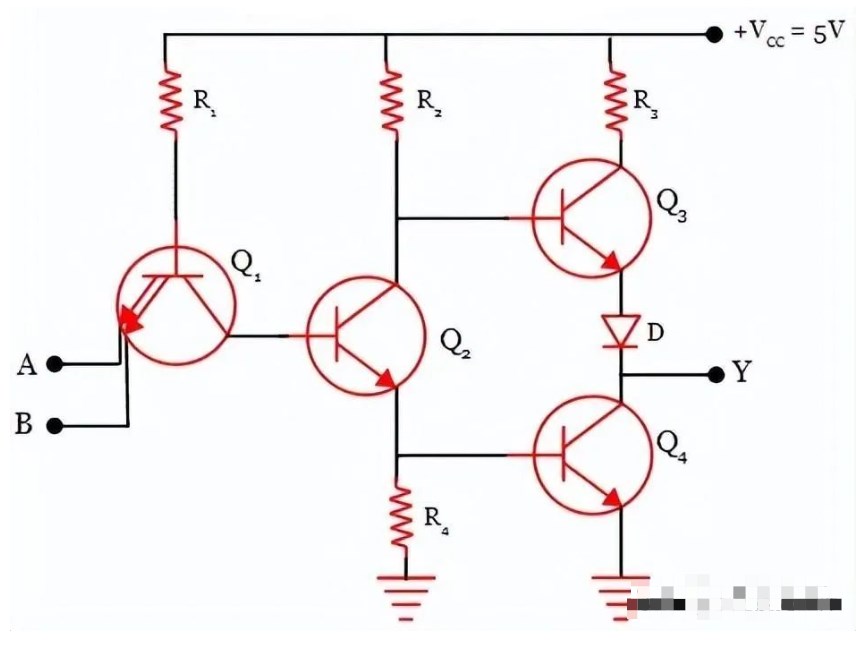

TTL邏輯電路是一種常用的數(shù)字邏輯家族,用于實現(xiàn)各種邏輯功能。在設(shè)計TTL邏輯電路時,經(jīng)常會遇到要處理的多余輸入端的情況。這些多余的輸入端是在設(shè)計過程中添加的,但最終并未用于電路功能。下面將詳細(xì)討論多余輸入端的處理方法以及為什么不能懸空使用。

多余輸入端的處理方法

1. 短路到接地:這是最常見的處理方法之一。將多余輸入端短路到接地,意味著將其與整個電路的地連接在一起。這樣可以確保輸入端保持穩(wěn)定的低電平,而不受外部電磁干擾的影響。

2. 短路到電源:類似于短路到接地,多余輸入端也可以與電源電壓連接在一起。這樣可以確保輸入端保持穩(wěn)定的高電平。

3. 使用外部電阻或電容:通過使用適當(dāng)?shù)耐獠吭梢詫⒍嘤噍斎攵诉B接到某個特定的電平或提供一定的隔離。

4. 使用模擬開關(guān):在某些情況下,多余輸入端可能需要連接到其他數(shù)字邏輯電路的輸出。這時可以使用模擬開關(guān),通過控制開關(guān)的導(dǎo)通或截止?fàn)顟B(tài),將多余輸入端連接或斷開。

為什么不能懸空使用?

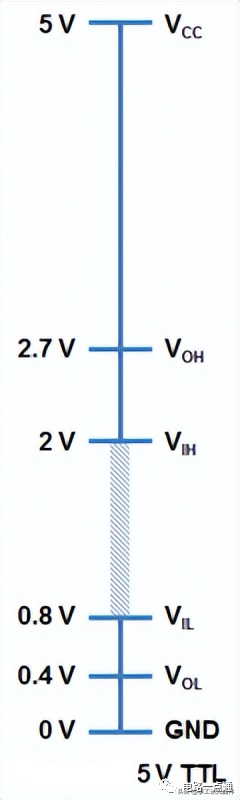

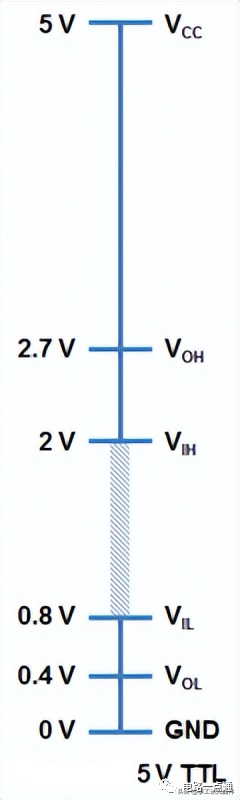

在TTL邏輯電路中,懸空的輸入端會導(dǎo)致電路的不穩(wěn)定性和不可預(yù)測的行為。以下是幾個原因:

1. 外部環(huán)境干擾:懸空輸入端會接收到環(huán)境中的電磁干擾信號,這些干擾信號可能會引起電路錯誤觸發(fā)或穩(wěn)態(tài)輸出錯誤。

2. 確定電平的問題:懸空的輸入端可能會處于高、低電平之間,這會導(dǎo)致電路的無法確定的狀態(tài)。這種不確定性會使電路輸出出現(xiàn)意外錯誤,甚至?xí)茐碾娐返姆€(wěn)定性。

3. 功耗問題:懸空輸入端會導(dǎo)致電流通過不確定的路徑流過電路,從而浪費電能。這種功耗可能不可忽略,尤其在大規(guī)模集成電路中。

在實際設(shè)計中,為了確保邏輯電路的可靠性和穩(wěn)定性,處理多余輸入端是很重要的一部分。通過適當(dāng)?shù)剡B接多余輸入端,可以降低電路的故障率,并提高整個系統(tǒng)的可靠性。

總結(jié)起來,處理多余輸入端的方法包括短路到接地或電源、使用外部元件連接到特定電平,或使用模擬開關(guān)將其連接到其他邏輯電路的輸出。懸空的輸入端會導(dǎo)致電路的不穩(wěn)定性和不可預(yù)測的行為,因此不能懸空使用。通過正確地處理多余輸入端,可以確保邏輯電路的穩(wěn)定性和可靠性。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

相關(guān)推薦

在數(shù)字電子學(xué)中,TTL和CMOS是兩種基本的邏輯電路技術(shù)。它們各自有著獨特的特點和應(yīng)用場景。 TTL邏輯電路 TTL(晶體管-晶體管

![的頭像]() 發(fā)表于

發(fā)表于 11-18 10:26

?882次閱讀

、GPU、內(nèi)存控制器等核心部件均大量使用邏輯電路芯片實現(xiàn)復(fù)雜的運算和控制功能。

通信設(shè)備:路由器、交換機、基站等通信設(shè)備中的信號處理、數(shù)據(jù)轉(zhuǎn)發(fā)等功能依賴于高性能的邏輯電路芯片。

消費電子:智能手機、平板

發(fā)表于 09-30 10:47

加法器不是時序邏輯電路 ,而是組合邏輯電路的一種。時序邏輯電路和組合邏輯電路的主要區(qū)別在于它們?nèi)?b class='flag-5'>何處理輸出信號。 組合

![的頭像]() 發(fā)表于

發(fā)表于 08-28 11:05

?539次閱讀

時序邏輯電路形成對比,后者具有記憶功能,輸出不僅取決于當(dāng)前輸入,還與過去的狀態(tài)有關(guān)。 并行處理能力 :組合邏輯電路可以同時處理多個

![的頭像]() 發(fā)表于

發(fā)表于 08-11 11:14

?913次閱讀

在數(shù)字電子學(xué)中,邏輯電路和時序邏輯電路是兩種基本的電路類型。它們在處理數(shù)字信號和實現(xiàn)數(shù)字系統(tǒng)時起著關(guān)鍵作用。邏輯電路主要用于實現(xiàn)基本的

![的頭像]() 發(fā)表于

發(fā)表于 07-30 15:00

?759次閱讀

問題。這些多余的輸入端如果不妥善處理,可能會對電路的性能和穩(wěn)定性產(chǎn)生不利影響。因此,了解并掌握CMOS門

![的頭像]() 發(fā)表于

發(fā)表于 07-30 14:50

?3066次閱讀

與非門閑置輸入端的處理方法,以確保電路的正常運行和可靠性。 TTL與非門的基本原理 TTL與非門

![的頭像]() 發(fā)表于

發(fā)表于 07-30 14:43

?1253次閱讀

一、引言 組合邏輯電路是數(shù)字電路中的重要組成部分,它僅由邏輯門電路(如與門、或門、非門等)和輸入/輸出端

![的頭像]() 發(fā)表于

發(fā)表于 07-30 14:38

?1163次閱讀

什么是組合邏輯電路和時序邏輯電路?時序邏輯電路和組合邏輯電路的區(qū)別是什么? 組合邏輯電路和時序邏輯電路

![的頭像]() 發(fā)表于

發(fā)表于 03-26 16:12

?3499次閱讀

ttl門多余的輸入端如何處理 ttl多余的

![的頭像]() 發(fā)表于

發(fā)表于 02-18 16:26

?3088次閱讀

TTL電路,即晶體管-晶體管邏輯電路,是一種基于雙極結(jié)型晶體管(BJT)的數(shù)字邏輯電路技術(shù)。

![的頭像]() 發(fā)表于

發(fā)表于 02-18 14:26

?3145次閱讀

TTL電路是一種晶體管-晶體管邏輯電路,它是Transistor-Transistor Logic的縮寫。TTL電路是一種數(shù)字

![的頭像]() 發(fā)表于

發(fā)表于 02-17 14:11

?1.6w次閱讀

時序邏輯電路是一種能夠存儲信息并根據(jù)時鐘信號按照特定順序執(zhí)行操作的電路。它是計算機硬件中非常重要的一部分,用于實現(xiàn)存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據(jù)輸入信號的組

![的頭像]() 發(fā)表于

發(fā)表于 02-06 11:18

?9774次閱讀

對于CMOS電路而言,多余的輸入端是不會影響電路的運行的,因為CMOS電路使用的是恒定電流源和M

![的頭像]() 發(fā)表于

發(fā)表于 02-04 17:00

?2770次閱讀

當(dāng)邏輯電路由多個邏輯門組成且不含存儲電路,對于給定的輸入變量組合將產(chǎn)生確定的輸出,則這種邏輯電路稱為組合

![的頭像]() 發(fā)表于

發(fā)表于 02-04 11:46

?1681次閱讀

TTL邏輯電路多余的輸入端該如何處理?能否懸空?

TTL邏輯電路多余的輸入端該如何處理?能否懸空?

評論