這是電力電子領域令人興奮的時代。在硅占據主導地位數十年后,兩種較新的材料——碳化硅和氮化鎵——已經開始占領價值數十億美元的市場。例如,碳化硅現在是電動汽車逆變器和充電器的首選半導體。如果您最近為智能手機或筆記本電腦購買了壁式充電器,那么它很可能使用氮化鎵。

被稱為寬帶隙半導體的新型材料正在取代這些和其他電力電子應用,因為它們提供了許多優越的特性。然而寬帶隙技術仍然存在根本性的弱點。對于碳化硅晶體管來說,一個很大的問題是溝道中電子的遷移率相對較低,溝道是器件柵極下方的區域,電流通過該區域在源極和漏極之間流動。這種低遷移率阻礙了 SiC 晶體管的高速開關。這反過來又限制了它們在交流電和直流電之間轉換等應用中的效率。

另一方面,氮化鎵晶體管有一個被稱為“動態導通電阻”的特性,這意味著當器件傳導電流時,器件的電阻取決于電壓——電壓越高意味著導通電阻越高。GaN 的另一個問題是,器件的物理尺寸及其成本會隨著其電壓阻斷能力的增加而增加,電壓阻斷能力是器件的一項關鍵能力,預計其開啟和關閉電壓比內部電壓高出許多倍。比如說,一臺典型的計算機。

如果您可以將 GaN 和 SiC 結合在一個器件中,最大限度地減少各自的弱點并最大限度地發揮其優勢,結果會怎樣?這個問題促使香港科技大學和中國其他三所機構的 16 名研究人員組成的團隊不斷思考。經過多年的努力,他們終于成功制造出一種晶體管,他們稱之為混合場效應晶體管(HyFET)。他們在去年 12 月于舊金山舉行的IEEE國際電子設備會議上發表的一篇論文中描述了他們的工作。

未參與該研究的寬帶隙半導體專家對這項技術成果印象深刻。康奈爾大學教授兼實驗室負責人、 IEEE 院士Debdeep Jena表示:“實際上,我對香港Kevin Chen團隊的研究成果感到非常興奮。” “它有很多優點和希望。” 然而,這些專家對該設備商業前景的看法普遍較為謹慎。

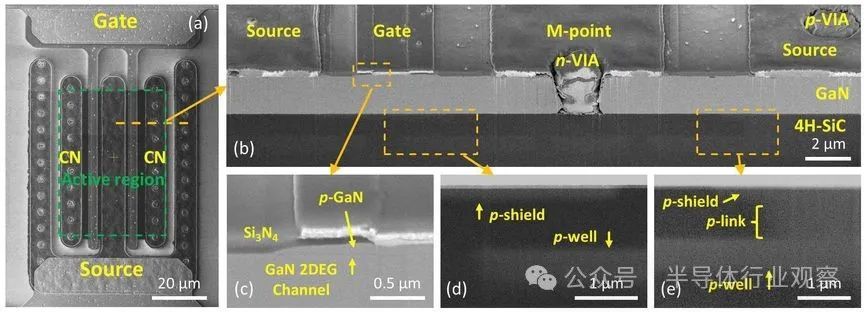

在運行中,該器件使用低壓高速 GaN 晶體管來控制高壓 SiC 結型場效應晶體管 (JFET)。在傳統的 SiC JFET 中,漏極位于器件底部,連接到襯底。電流垂直流動,由器件頂部的柵極控制,通過“漂移層”到達也在器件頂部的一個或多個源極端子。在混合 FET 中,基本配置是可識別的:器件底部有一個漏極,連接到基板。電流向上流過 SiC 漂移層。然而,柵極和源極端子位于直接集成在器件頂部 SiC JFET 上方的 GaN 晶體管中。因此,流經 SiC JFET 的電流由器件 GaN 部分中的柵極和源極端子控制。

這里的優點是,具有高電子遷移率的 GaN 晶體管控制組合器件的開關。該組合器件建立在 SiC JFET 的基礎上,具有大漂移區,具有 SiC 的電壓阻斷能力。測試表明該設備很大程度上滿足了研究人員的期望。他們發現,雖然遷移率不如傳統 GaN 器件那么高,但它“適合高頻開關”。他們還證明,在“關閉”狀態下,該設備可以阻斷大約 600 伏的電壓,具體取決于溫度,這對于首個同類實驗設備來說相當不錯。

制造該設備必須克服許多挑戰。其中主要的方法之一是直接在 SiC 晶體管之上生長 GaN 晶體管。氮化鎵器件通常在 SiC 襯底上制造。然而,這些器件是“在軸上”生長的,這意味著它們是逐層生長的,每層都平行于襯底。但 SiC 器件通常是相對于其襯底晶體晶格的方向離軸生長的。因此,研究人員必須設計出一種在 SiC 器件上生長 GaN 晶體管的方法,其軸偏差或“誤切”為 4 度。

為此,他們開發了一種稱為“兩步雙軸應變釋放”的技術。兩種不同半導體之間界面的一個基本問題是在兩種不同晶體合并的邊界處產生的應變。這種應變會在晶格中產生影響性能的缺陷,稱為位錯。研究人員改進和開發的技術通過兩種特定類型的位錯釋放應變,最大限度地減少其有害影響。

HyFET的弱點之一是晶體管處于導通狀態時對電流的阻力。這個值稱為 R on,相當高,約為每厘米2 50 兆歐。R on越高意味著整體效率越低。當然,混合 FET 確實是同類產品中的第一個,是在大學實驗室中構建的。

作者兼 IEEE 院士 Kevin Chen 在一封電子郵件中寫道:“我們論文中的大 R源于小型設備……以及 SiC 部分非常保守的設計。” “一般來說,利用工業 SiC 制造設施實現 1200 V HyFET的3mΩ?cm2(~2.6)不存在其他障礙。”

不過,為了進行比較,能夠阻斷超過 600 伏電壓的最先進的 SiC 或 GaN 晶體管的導通電阻可以低至2 mΩ?cm2,絕緣晶體管的發明人、IEEE 終身研究員B. 北卡羅來納州立大學電氣工程系杰出教授Jayant Baliga指出。鑒于這些數字,Baliga 質疑當更簡單且可能更便宜的 SiC 晶體管出現時,對商用混合 FET 的需求量會有多大。“如果比導通電阻沒有降低到碳化硅 MOSFET 的以下,那么什么會促使人們轉向更復雜的東西,所有這些層都在生長?” (金屬氧化物半導體 FET),Baliga 問道。

IEEE 院士、加州大學圣巴巴拉分校工程學院院長、GaN 功率器件先驅Umesh Mishra質疑將兩種不同半導體集成到單個器件中的優勢(極小的電感延遲和電容損耗)是否值得制造復雜性和其他因素的成本。他指出,為了制造這樣的設備,公司“現在必須擁有兩種在工廠運行的技術”。“他們必須擁有碳化硅技術,而且必須擁有氮化鎵技術。沒有人愿意這樣做,因為你現在有兩種復雜的技術需要同時嘗試運行”——這是一個成本高昂的提議。

“擴展一些困難的事情總是很困難,”米什拉補充道。“那么問題來了,你的好處是什么?” Mishra 指出,通過簡單地將兩個不同的晶體管連接在一個封裝中,而不是將它們集成到單個混合器件中,就可以以低得多的成本獲得組合器件的大部分優點。

然而,作者陳表示,不需要的電子特性,特別是稱為寄生電感的弱點,將困擾簡單封裝在一起而不是集成的晶體管。“較低的寄生電感可以最大限度地減少開關振蕩并降低開關損耗,”他在電子郵件中寫道。“先進的共封裝技術可以在一定程度上降低寄生電感,但可能不如集成器件(在批量過程中實現)具有成本效益。”

康奈爾大學的 Jena 指出,混合 FET 潛在的不可克服的障礙是 GaN 器件的進步速度。他表示,在可預見的未來,GaN 將變得如此強大,以至于可能不需要混合方案就能取得勝利。“物理學告訴我,從長遠來看,GaN 是贏家,”他說。“我不想從 [混合 FET] 論文中奪走任何東西。這是一篇很棒的論文。但無論他們在這里展示了什么,未來氮化鎵也將成為可能。”他總結道。

來源:半導體行業觀察

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27290瀏覽量

218087 -

晶體管

+關注

關注

77文章

9682瀏覽量

138081 -

SiC

+關注

關注

29文章

2804瀏覽量

62607 -

GaN

+關注

關注

19文章

1933瀏覽量

73286

原文標題:一種結合了SiC和GaN優勢的晶體管

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種結合了SiC和GaN優勢的晶體管

一種結合了SiC和GaN優勢的晶體管

評論