近日,芯來科技攜手杭州廣立微電子股份有限公司(以下簡稱“廣立微”)及上海億瑞芯電子科技有限公司(以下簡稱“億瑞芯”),共同建立在Design for Test(DFT)可測試性設計領域的戰略合作關系,以擴大三方合作的深度和廣度,為產業提供有競爭力的多元化設計方案。

強強聯合提供更優質解決方案

此次戰略合作發揮了三方各自的資源優勢,芯來科技的高性能、低功耗的RISC-V處理器IP,聯合廣立微DFTEXP可測試性設計軟件和良率診斷解決方案以及億瑞芯的DFT流程及設計解決方案,共同為客戶提供更優質的芯片設計IP和解決方案。

RISC-V是基于精簡指令集的CPU開放指令集架構,其在信息安全、工業控制、邊緣計算、自動駕駛等領域,提供了開放、簡潔、模塊化、可定制、可擴展的技術優勢,使得整個產業獲得了一條以更低成本更靈活自主方式進行產品設計的路徑,所以越來越多的芯片公司以及系統公司加入其應用進程。而IP核在RISC-V芯片研發過程中,則扮演著重要的角色,不僅能提高設計研發效率,使得芯片具備更好的功能和性能。

可測試性設計(DFT)給整個測試領域開拓了一條切實可行的途徑,目前國際上大中型IC設計公司基本上都采用了可測性設計的設計流程,DFT已經成為芯片設計過程中的至關重要的一環。DFT可測試性設計的重要工具和流程,已成功用于驗證RISC-V IP的其中一個環節。

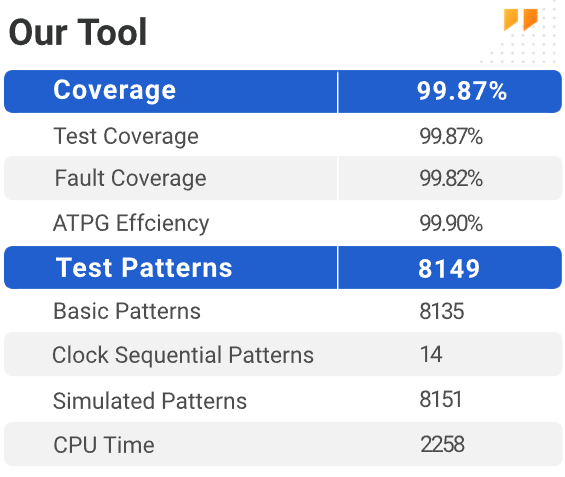

基于廣立微和億瑞芯共同打造的DFTEXP平臺,在芯來NA900RISC-V CPU IP中完成DFT的設計實現,并實現Memory全覆蓋,Logic部分覆蓋率可達到99.87%,達標桿工具水平。未來,三方將通過優勢互補, 打造長期、友好、共贏的戰略合作伙伴關系, 共拓Design for Test(DFT)可測試性設計領域新藍圖。

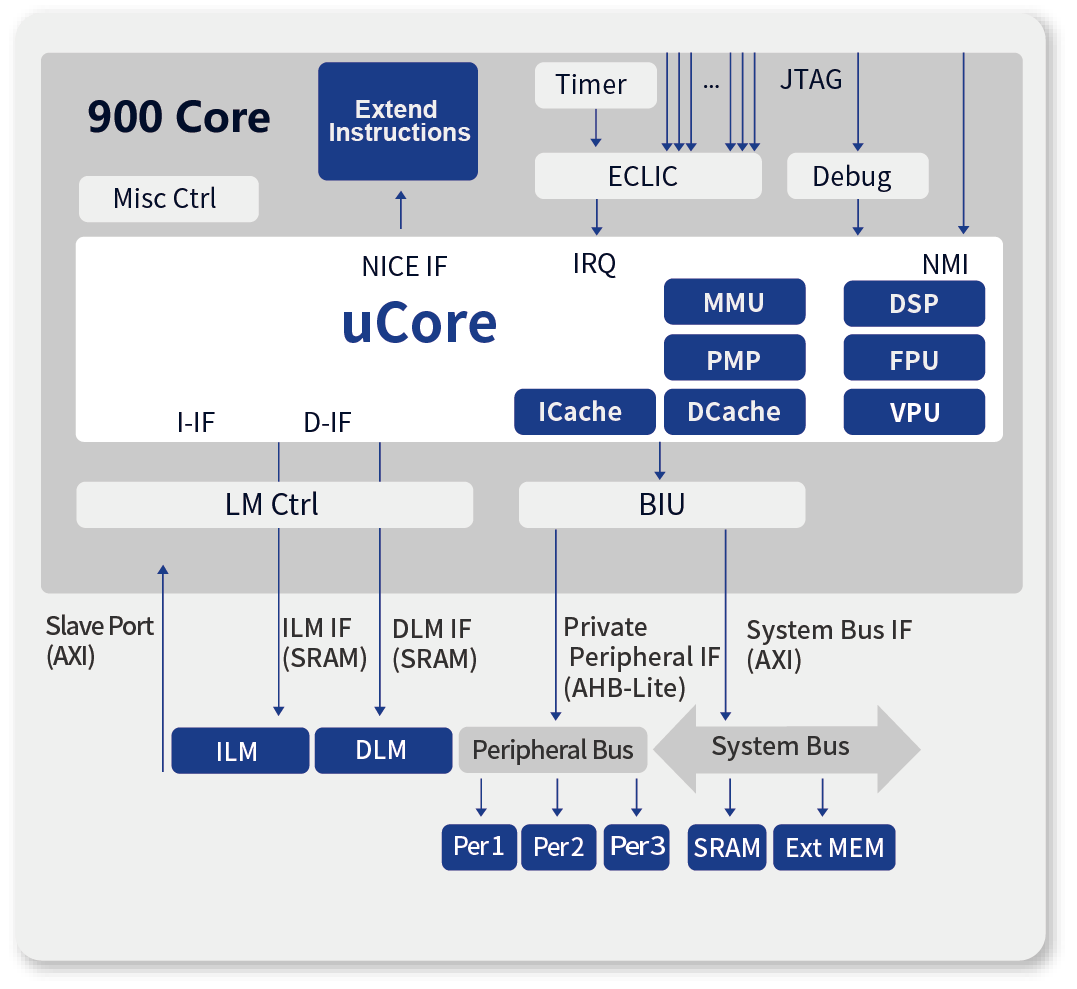

芯來900系列處理器內核

本次使用的產品是芯來科技900系列RISC-V處理器內核。芯來900系列處理器內核包括N900(32位)、U900(32位+MMU)、NX900(64位)和UX900(64位+MMU)四個產品系列,其中U900、UX900帶MMU可以運行重型操作系統,如Linux等。它非常適合對標ARM Cortex-M7、R5、R52+、R8、A5、A7、M85、R82、A35、A53、A55等內核,可應用于AIoT邊緣計算、數據中心、網絡設備和基帶通信等領域。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19312瀏覽量

230032 -

芯片設計

+關注

關注

15文章

1021瀏覽量

54913 -

DFT設計

+關注

關注

0文章

10瀏覽量

8883 -

RISC-V

+關注

關注

45文章

2292瀏覽量

46198 -

芯來科技

+關注

關注

0文章

60瀏覽量

3028

原文標題:共譜“芯”篇章?芯來科技攜手戰略伙伴為RISC-V CPU IP提升DFT可測試性設計

文章出處:【微信號:nucleisys,微信公眾號:芯來科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HighTec C/C++編譯器套件全面支持芯來RISC-V IP

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

Arteris與晶心科技攜手推進RISC-V SoC設計創新

經緯恒潤AUTOSAR產品成功適配芯來RISC-V車規內核

芯來科技攜手戰略伙伴為RISC-V CPU IP提升DFT可測試性設計

芯來科技攜手戰略伙伴為RISC-V CPU IP提升DFT可測試性設計

評論