數字IC設計里,常會出現鎖存器,D觸發器和寄存器,很多人(比如我)老傻傻分不清,搞不懂他們的區別是什么。

寄存器,D觸發器和鎖存器都是數字電路中的重要組件,它們之間存在著密切的關系和明顯的區別。寄存器是一種重要的存儲單元,通常由觸發器組成,用于暫存指令、數據和地址。寄存器的輸出端平時不隨輸入端的變化而變化,只有在時鐘有效時才將輸入端的數據送輸出端。

D觸發器是一種邊沿敏感的存儲單元,具有緩存數據的功能。當CLK輸入上升沿時,D被傳輸到Q,之后Q將在CLK下一個上升沿到來前保持不變。也就是說,D觸發器可以作為寄存器使用。

鎖存器與觸發器不同,它不在鎖存數據時,輸出端的信號隨輸入信號變化,就像信號通過一個緩沖器一樣;一旦鎖存信號起鎖存作用,則數據被鎖住,輸入信號不起作用。鎖存器一般由電平信號控制,屬于電平敏感型。其狀態的變化和特定電平有關(高電平和低電平),而寄存器的狀態變化往往需要邊沿信號(上升沿和下降沿),因此鎖存器不屬于寄存器。

總的來說,鎖存器為電平敏感器件,而D觸發器和寄存器為邊沿信號敏感器件;兩個鎖存器可以構建一個D觸發器;D觸發器屬于寄存器。這些設備由于其各自的特性和工作方式,決定了它們在數字電路中的不同應用場合。

什么是鎖存器

鎖存器是一種電路元件,用于存儲和保持輸入信號的狀態。它通常由一個觸發器和一個或多個門電路組成。當輸入信號發生變化時,鎖存器會將當前狀態保存下來,并在下一個時鐘周期中輸出該狀態。

換句話說, 如果一個模塊的只有在特定電平的作用下,才會將輸入信息更新到他的輸出引腳 ,否則該模塊的輸出將保持不變,那么這個模塊就可以被看成是一個鎖存器。

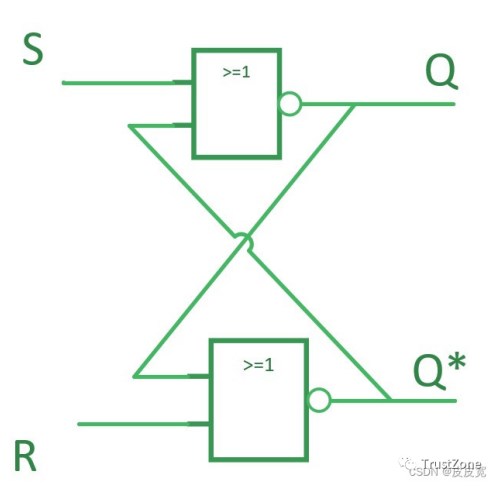

常見的S-R寄存器的結構如下所示:

鎖存器在數字電路設計中有多種應用,例如數據存儲、計數器、移位寄存器等。然而,在某些情況下,鎖存器可能會導致電路出現錯誤或不穩定的行為。

什么情況下會出現鎖存器

以下是一些可能導致鎖存器出現問題的情況:

1.競爭條件:當多個信號同時改變鎖存器的輸入時,可能會出現競爭條件。這會導致鎖存器無法正確地存儲和輸出預期的狀態。

2.亞穩態:在某些情況下,鎖存器的輸出可能會處于不穩定的狀態,即亞穩態。這可能會導致電路的誤操作或故障。

3.毛刺:當輸入信號發生突變時,可能會產生毛刺信號。這些毛刺信號可能會干擾鎖存器的正常工作,導致錯誤的輸出。

4.時序問題:如果鎖存器的時鐘信號與其他電路的時序不匹配,可能會導致電路的不穩定行為或錯誤。

鎖存器的危害

鎖存器的危害主要體現在以下幾個方面:

1.數據丟失:由于鎖存器只能存儲和輸出當前狀態,如果輸入信號的變化被鎖存器忽略或丟失,可能會導致數據的丟失或錯誤。

2.競爭條件:競爭條件可能導致鎖存器無法正確地存儲和輸出預期的狀態,從而導致電路的錯誤或不穩定行為。

3.亞穩態:亞穩態可能導致電路的誤操作或故障,影響電路的穩定性和可靠性。

4.時序問題:時序問題可能導致電路的不穩定行為或錯誤,影響電路的性能和可靠性。

數字IC設計中為什么要避免鎖存器

為了避免鎖存器的問題,數字IC設計中通常會采取以下措施:

1.使用同步電路:同步電路通過使用統一的時鐘信號來控制電路的操作,可以避免競爭條件和時序問題。

2.引入延遲:通過在輸入信號路徑中引入適當的延遲,可以確保鎖存器能夠正確地采樣和存儲輸入信號的變化。

3.使用觸發器:觸發器是一種具有自定時功能的鎖存器,它可以確保在正確的時間點存儲和輸出輸入信號的狀態。

4.進行時序分析:通過對電路進行時序分析,可以評估電路的穩定性和可靠性,并采取相應的措施來避免鎖存器的問題。

總之,鎖存器在數字IC設計中具有重要的應用價值,但在某些情況下可能會出現問題。為了避免這些問題,設計人員需要了解鎖存器的工作原理和可能的危害,并采取相應的措施來確保電路的穩定性和可靠性。

-

IC設計

+關注

關注

38文章

1295瀏覽量

103918 -

移位寄存器

+關注

關注

3文章

258瀏覽量

22265 -

鎖存器

+關注

關注

8文章

906瀏覽量

41495 -

D觸發器

+關注

關注

3文章

164瀏覽量

47902 -

時序分析

+關注

關注

2文章

127瀏覽量

22565

發布評論請先 登錄

相關推薦

數字IC設計中為什么要避免鎖存器呢?

什么是鎖存器?數字IC設計中為什么要避免鎖存器?

什么是鎖存器?數字IC設計中為什么要避免鎖存器?

評論