共讀好書

本篇文章將探討用于晶圓級封裝(WLP)的各項材料,從光刻膠中的樹脂,到晶圓承載系統(WSS)中的粘合劑,這些材料均在晶圓級封裝中發揮著重要作用。

光刻膠(Photoresists, PR):由感光劑、樹脂和溶劑構成,用于形成電路圖案和阻擋層

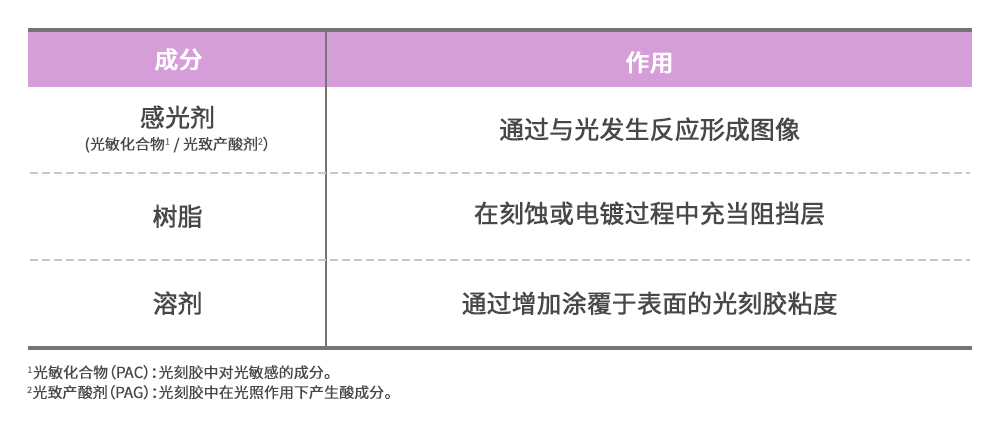

光刻膠是由可溶性聚合物和光敏材料組成的化合物,當其暴露在光線下時,會在溶劑中發生降解或融合等化學反應。在運用于晶圓級封裝的光刻(Photolithography)工藝過程中時,光刻膠可用于創建電路圖案,還可在后續電鍍(Electroplating)1過程中通過電鍍金屬絲以形成阻擋層。光刻膠的成分如圖1所示。

1電鍍(Electroplating):一項晶圓級封裝工藝,通過在陽極上發生氧化反應來產生電子,并將電子導入到作為陰極的電解質溶液中,使該溶液中的金屬離子在晶圓表面被還原成金屬。

▲ 圖1:光刻膠的成分和作用(? HANOL出版社) 根據光照的反應原理,光刻膠可分為正性光刻膠(Positive PR)和負性光刻膠(Negative PR)。對于正性光刻膠,曝光區域會發生降解反應,導致鍵合減弱;而未曝光區域則會發生交聯(Cross-linking)2反應,使鍵合增強。因此,被曝光部分在顯影過程中會被去除。然而對于負性光刻膠,曝光部分會產生交聯反應并硬化,從而被完整保留下來;未曝光部分則被去除。負性光刻膠的粘度通常高于正性光刻膠,旋涂過程中的涂覆厚度更厚,因而通常被用于形成較高的焊接凸點(Solder Bump)。而正性光刻膠則至少需要涂覆兩次。 光刻過程中所使用的光源可根據波長進行分類,波長以納米(nm)為單位。對于細微化(Scaling)的半導體而言,在光刻過程中通常采用波長較短的光源,以增強光刻效果,從而形成更精細的電路圖案。因此,光敏化合物(PAC)用于制作曝光波長較長的g線(g-line)3光刻膠和i線(i-line)?光刻膠。而化學放大型抗蝕劑(CAR)?則用于制作曝光波長較短的光刻膠。晶圓級封裝通常使用i線步進式光刻機(Stepper)?。 2交聯(Cross-link):通過化學鍵將聚合物鏈連接在一起的化學反應。

▲ 圖1:光刻膠的成分和作用(? HANOL出版社) 根據光照的反應原理,光刻膠可分為正性光刻膠(Positive PR)和負性光刻膠(Negative PR)。對于正性光刻膠,曝光區域會發生降解反應,導致鍵合減弱;而未曝光區域則會發生交聯(Cross-linking)2反應,使鍵合增強。因此,被曝光部分在顯影過程中會被去除。然而對于負性光刻膠,曝光部分會產生交聯反應并硬化,從而被完整保留下來;未曝光部分則被去除。負性光刻膠的粘度通常高于正性光刻膠,旋涂過程中的涂覆厚度更厚,因而通常被用于形成較高的焊接凸點(Solder Bump)。而正性光刻膠則至少需要涂覆兩次。 光刻過程中所使用的光源可根據波長進行分類,波長以納米(nm)為單位。對于細微化(Scaling)的半導體而言,在光刻過程中通常采用波長較短的光源,以增強光刻效果,從而形成更精細的電路圖案。因此,光敏化合物(PAC)用于制作曝光波長較長的g線(g-line)3光刻膠和i線(i-line)?光刻膠。而化學放大型抗蝕劑(CAR)?則用于制作曝光波長較短的光刻膠。晶圓級封裝通常使用i線步進式光刻機(Stepper)?。 2交聯(Cross-link):通過化學鍵將聚合物鏈連接在一起的化學反應。

3g線(g-line):在汞光譜中,一條對應波長約為436納米的譜線。

?i線(i-line):在汞光譜中,一條對應波長約為356納米的譜線。

?化學放大型抗蝕劑(CAR):一種用于提高光刻膠材料光敏性的抗蝕劑。

?步進式光刻機(Stepper):用于曝光晶圓的設備。不同類型的設備用于不同精度晶圓的曝光,具體取決于對應的光源類型。

電鍍液:由金屬離子、酸和添加劑組成,用于可控電鍍工藝

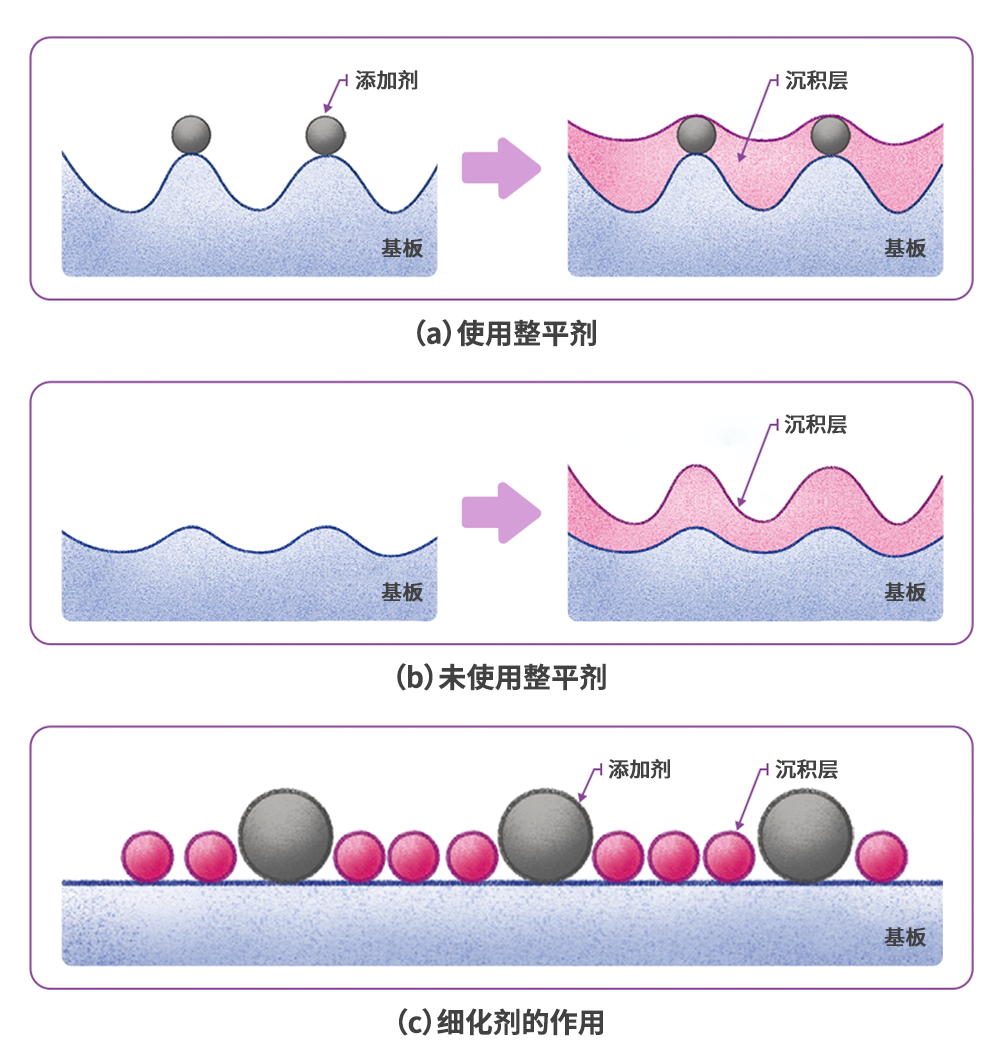

電鍍液(Plating Solution)是一種在電鍍過程中使用的溶液,由金屬離子、酸和添加劑組成。其中,金屬離子是電鍍過程中的待鍍物質;酸作為溶劑,用于溶解溶液中的金屬離子;多種添加劑用于增強電鍍液和鍍層的性能。可用于電鍍的金屬材料包括鎳、金、銅、錫和錫銀合金,這些金屬以離子的形式存在于電鍍液中。常見的酸性溶劑包括硫酸(Sulfuric Acid)和甲磺酸(Methanesulfonic Acid)。添加劑包括整平劑(Leveler)和細化劑(Grain Refiner),其中,整平劑用于防止材料堆積,提高電鍍層平整性;而晶粒細化劑則可以防止電鍍晶粒的橫向生長,使晶粒變得更加細小。

▲ 圖2:電鍍液中添加劑的作用(? HANOL出版社)

▲ 圖2:電鍍液中添加劑的作用(? HANOL出版社)

光刻膠剝離液(PR Stripper):使用溶劑完全去除光刻膠

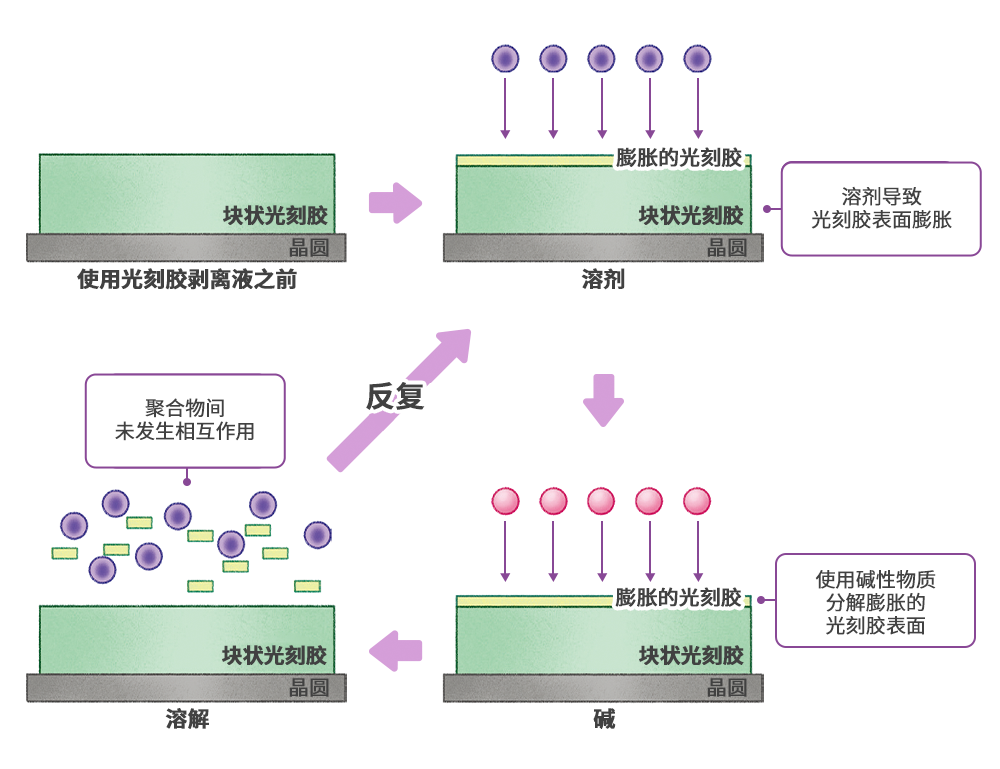

電鍍工藝完成后,需使用光刻膠剝離液去除光刻膠,同時注意避免對晶圓造成化學性損傷或產生殘留物。圖3展示了光刻膠去膠工藝的過程。首先,當光刻膠剝離液與光刻膠表面接觸時,兩者會發生反應,使光刻膠膨脹;接下來,堿性剝離液開始分解并溶解膨脹的光刻膠。

▲ 圖3:光刻膠剝離液的去膠工序(? HANOL出版社)

▲ 圖3:光刻膠剝離液的去膠工序(? HANOL出版社)

刻蝕劑:使用酸、過氧化氫等材料精確溶解金屬

晶圓級封裝需要通過濺射(Sputtering)?工藝形成籽晶層(Seed Layer),即通過濺射或蒸餾的方式形成的一層用于電鍍的薄金屬。電鍍和光刻膠去膠工序完成后,需使用酸性刻蝕劑來溶解籽晶層。 ?濺射(Sputtering):一種用高能離子轟擊金屬靶材,使噴射出來的金屬離子沉積到晶圓表面的物理氣相沉積工藝。

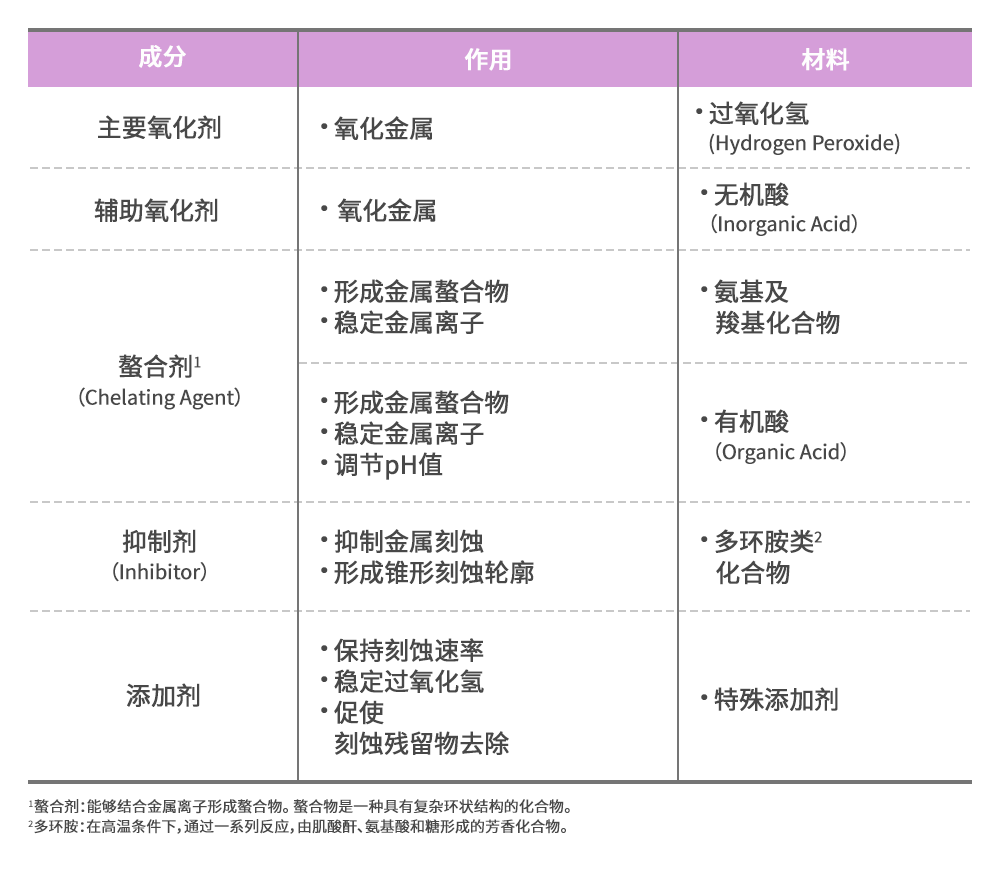

圖4展示了刻蝕劑的主要成分和作用。根據不同的待溶解金屬,可選用不同刻蝕劑,如銅刻蝕劑、鈦刻蝕劑、銀刻蝕劑等。此類刻蝕劑應具有刻蝕選擇性——在有選擇性地溶解特定金屬時,不會溶解或僅少量溶解其它金屬;刻蝕劑還應具備較高的刻蝕速率,以提高制程效率;同時還應具備制程的均勻性,使其能夠均勻地溶解晶圓上不同位置的金屬。

▲ 圖4:刻蝕劑的主要成分和作用(? HANOL出版社)

▲ 圖4:刻蝕劑的主要成分和作用(? HANOL出版社)

濺射靶材:將金屬沉積于基板上

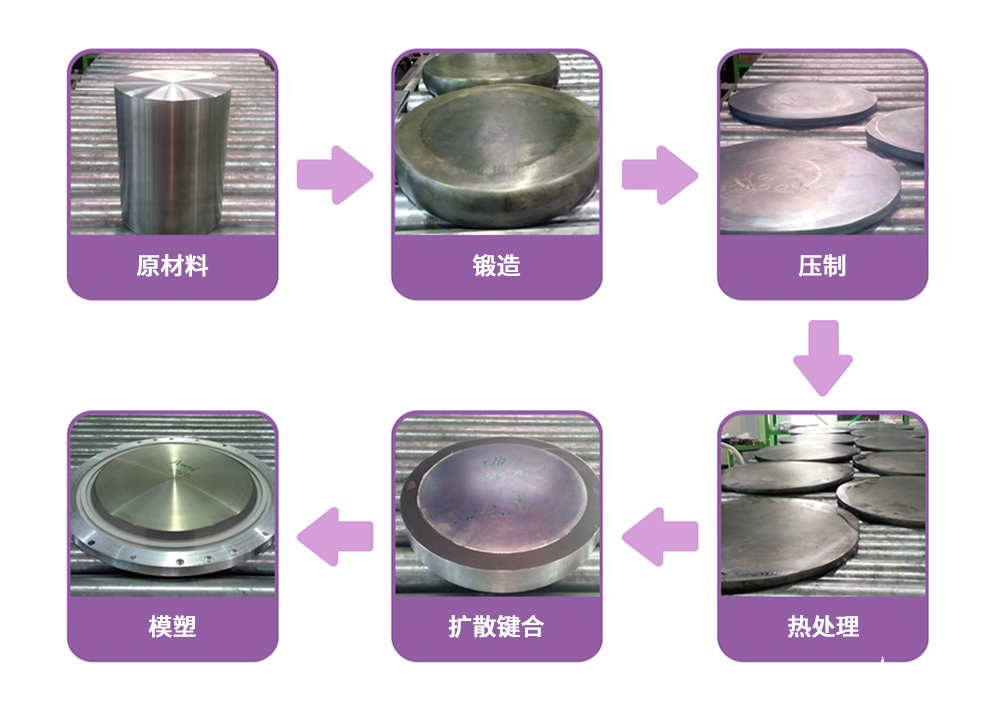

濺射靶材是一種在物理氣相沉積(PVD)?過程中,采用濺射工藝在晶圓表面沉積金屬薄膜時使用的材料。圖5展示了靶材的制造工序。首先,使用與待濺射金屬層成分相同的原材料制成柱體;然后經過鍛造、壓制、和熱處理最終形成靶材。

?物理氣相沉積(PVD):一種采用物理方法將材料分離并沉積在特定表面的薄膜沉積工藝。 ▲ 圖5:濺射靶材的制作工序(? HANOL出版社)

▲ 圖5:濺射靶材的制作工序(? HANOL出版社)

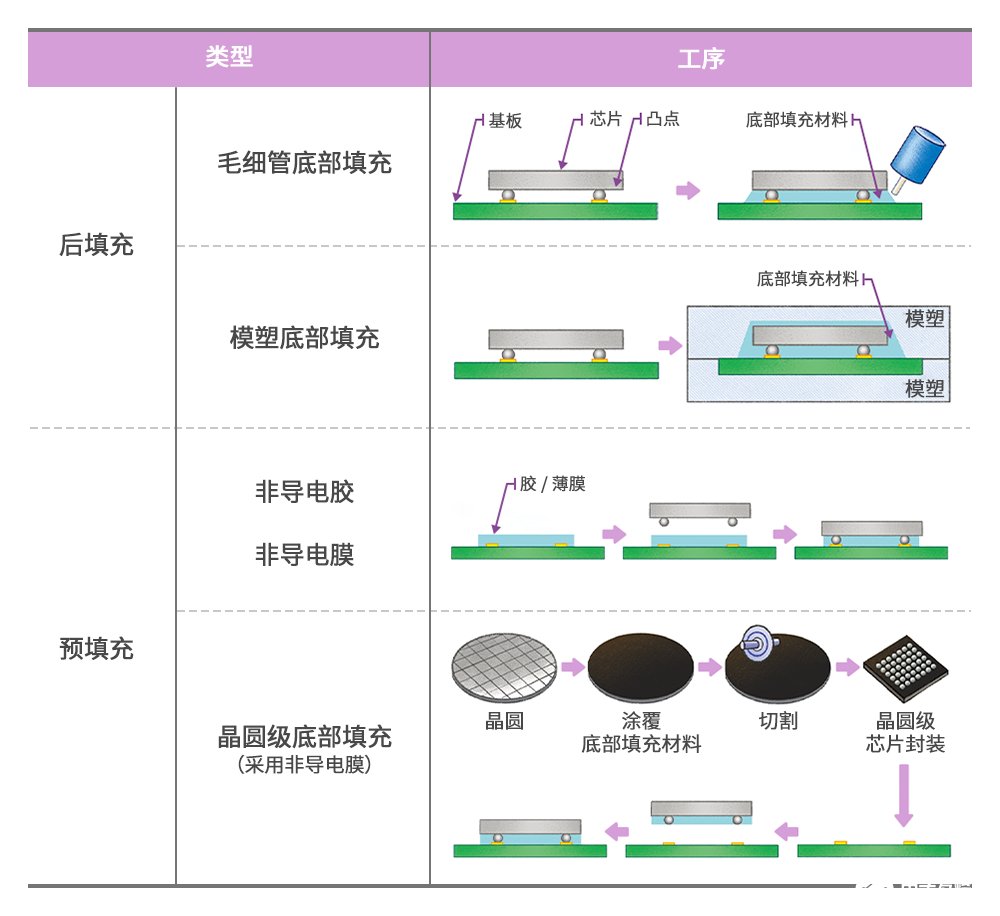

底部填充:使用環氧樹脂模塑料(EMC)、膠和薄膜填充孔洞,實現接縫保護 與倒片鍵合(Flip Chip Bonding)相同,通過填充基板與芯片間的空隙、或以凸點鏈接的芯片與芯片之間的空隙,底部填充增強了接合處的可靠性。用于填充凸點之間空間的底部填充工藝分為后填充(Post-Filling)和預填充(Pre-applied Underfill)兩種。后填充是指完成倒片鍵合之后填充凸點之間的空間,而預填充則是指在完成倒片鍵合之前進行填充。此外,后填充可進一步細分為毛細管?底部填充(Capillary Underfill, CUF)和模塑底部填充(Molded Underfill, MUF)。完成倒片鍵合之后,采用毛細管底部填充工藝,利用毛細管在芯片側面注入底部填充材料來填充凸點間隙,此種工藝增加了芯片和基板之間的間隙內表面張力。而模塑底部填充則是在模塑過程中使用環氧樹脂模塑料(EMC)作為底部填充材料,從而簡化工序。 ?毛細管(Capillary):一種用于將液體封裝材料輸送到半導體封裝體的極細管材。

在預填充過程中,芯片級封裝和晶圓級封裝采用的填充方法也有所不同。對于芯片級封裝,會根據接合處的填充物,如非導電膠(NCP)或非導電膜(NCF),根據不同的填充物,其采用的工藝和材料也不盡不同;而對于晶圓級封裝,非導電膜則被作為底部填充的主材。圖6說明了不同類型的底部填充材料和相關工序。

▲ 圖6:不同類型的底部填充工藝(? HANOL出版社)

▲ 圖6:不同類型的底部填充工藝(? HANOL出版社)

在倒片封裝和硅通孔(TSV)型芯片堆疊工藝中,底部填充材料是保證接合處可靠性的關鍵組成部分。因此,相關材料需滿足腔體填充、界面粘附、熱膨脹系數(CTE)1?、熱導性和熱阻性等等方面的特定要求。 1?熱膨脹系數(CTE):一種材料屬性,用于表示材料在受熱情況下的膨脹程度。

晶圓承載系統:使用載片、臨時鍵合膠(TBA)、承載薄膜(Mounting tape)實現封裝組裝

晶圓承載系統工藝需充分支持薄晶圓載片和臨時鍵合膠等相關工序。載片脫粘后,需使用承載薄膜將正面和背面已形成凸點的薄晶圓固定在環形框架上。 在晶圓承載系統所使用的材料中,臨時鍵合膠尤為重要。在鍵合晶圓與載片形成硅通孔封裝時,臨時鍵合膠必須在晶圓背面加工過程中保持較強的黏附力, 以防止晶圓上的凸點等受損。此外,需確保不會出現排氣(Outgassing)11、空隙(Voids)12、分層(Delamination)13和溢出——鍵合過程中粘合劑從晶圓側面滲出等現象。最后,載體還必須具備熱穩定性和耐化學性,在保證載片易于去除的同時,確保不會留下任何殘留物。

11排氣(Outgassing):氣體從液體或固體物質中釋放出來。如果這種氣體凝結在半導體器件表面,并對器件性能產生影響,則會導致半導體器件存在缺陷。

12空隙(Voids):因氣泡的存在,在材料內部形成的空隙,有可能在高溫工藝或脫粘過程中會膨脹,增加使器件發生損壞或故障的風險。

13分層(Delamination):半導體封裝中兩個相連的表面互相分離的現象。 盡管首選材料為硅載片,但玻璃載片的使用頻率也很高。尤其是在脫粘過程中使用激光等光源的工藝時,必需使用玻璃載片。

通過這些關于傳統封裝和晶圓級封裝所需材料的文章介紹,我們不難發現,材料的類型和質量需不斷與時俱進,以滿足半導體行業的發展需求。

來源:未來半導體

歡迎掃碼添加小編微信

掃碼加入知識星球,領取公眾號資料

審核編輯 黃宇

-

晶圓

+關注

關注

52文章

5024瀏覽量

128640 -

光刻膠

+關注

關注

10文章

323瀏覽量

30489 -

晶圓級封裝

+關注

關注

5文章

33瀏覽量

11569

發布評論請先 登錄

相關推薦

簽約頂級封裝廠,普萊信巨量轉移技術掀起晶圓級封裝和板級封裝的技術革命

不同材料在晶圓級封裝中的作用

不同材料在晶圓級封裝中的作用

評論